## Intel<sup>®</sup> Iris<sup>®</sup> Xe and UHD Graphics Open Source

## **Programmer's Reference Manual**

For the 2020-2021 11th Generation Intel Xeon®, Core™, Celeron®, Pentium® Gold Processors based on the "Tiger Lake" Platform

Volume 6: Memory Views

May 2023, Revision 2.0

### **Notices and Disclaimers**

Intel technologies may require enabled hardware, software or service activation.

No product or component can be absolutely secure.

Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not "commercial" names and not intended to function as trademarks

Customer is responsible for safety of the overall system, including compliance with applicable safetyrelated requirements or standards.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document, with the sole exceptions that a) you may publish an unmodified copy and b) code included in this document is licensed subject to Zero-Clause BSD open source license (0BSD). You may create software implementations based on this document and in compliance with the foregoing that are intended to execute on the Intel product(s) referenced in this document. No rights are granted to create modifications or derivatives of this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

## **Revision History**

| Revision | Description                                                                                                                                                                                                                                              |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0      | Initial Release                                                                                                                                                                                                                                          |

| 2.0      | The following sections were added:<br>• Memory Types and Cache Interface<br>• Memory Object Control State (MOCS)<br>• L3 Control Registers<br>• Memory Interface Control Registers<br>• Required PAT & MOCS Tables<br>• LNCFCMOCSx<br>• GLOB_MOCS_LECC_x |

## **Table of Contents**

| Memory Views                            | 1  |

|-----------------------------------------|----|

| Introduction                            | 1  |

| Graphics Virtual Memory                 | 3  |

| Graphics Translation Tables             | 4  |

| Memory Types and Cache Interface        |    |

| Memory Object Control State (MOCS)      |    |

| L3 Control Registers                    | 15 |

| Memory Interface Control Registers      | 16 |

| Required PAT & MOCS Tables              |    |

| Virtual Addressed TR Translation Tables | 22 |

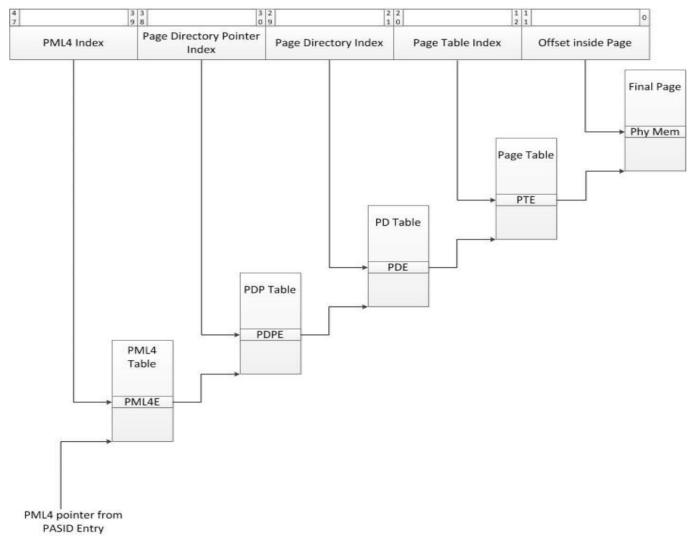

| Walk with 64KB Page                     | 27 |

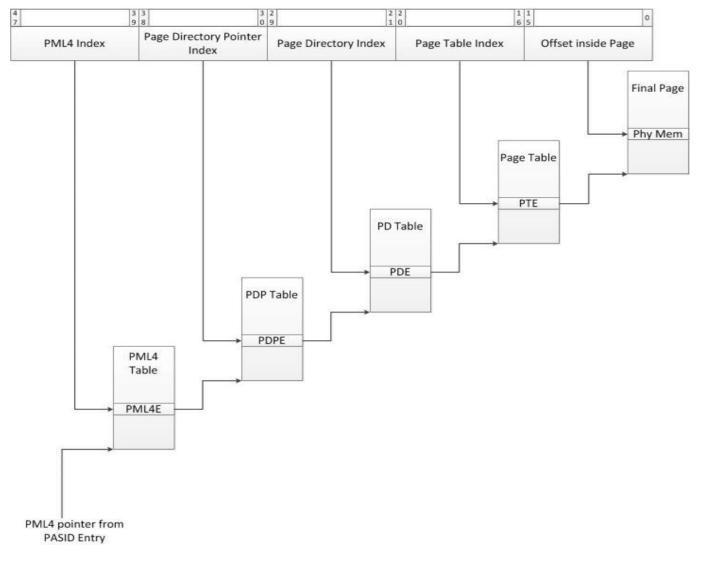

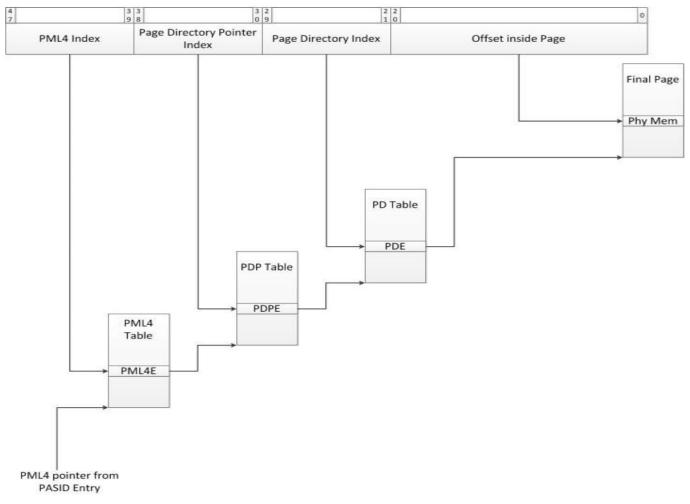

| Walk with 2MB Page                      |    |

| Pointer to PML4 table                   |    |

| PML4E: Pointer to PDP Table             |    |

| PDPE: Pointer to PD Table               |    |

| PDPE for PD                             |    |

| PDPE for 1GB Page                       |    |

| PD: Pointer to Page Table               |    |

| PDE for Page Table                      |    |

| PDE for 2MB Page                        |    |

| PTE: Page Table Entry for 64KB Page     |    |

| PTE: Page Table Entry for 4KB Page      |    |

| LNCFCMOCSx                              |    |

| GLOB_MOCS_LECC_x                        | 41 |

## **Memory Views**

### Introduction

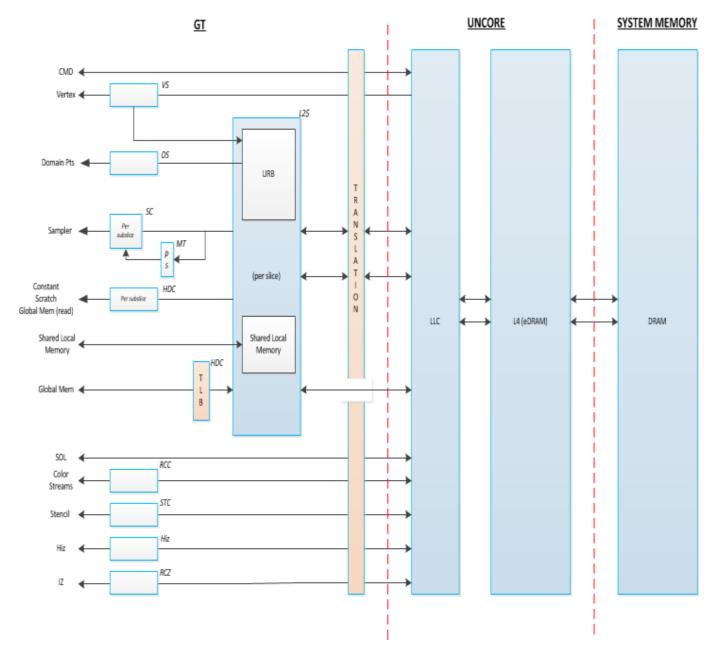

A modern GPU consists of multiple "engines", including Compute, Render (including Fixed Functions), Media Encode/Decode, Media Enhancement, Blitter/Copy, etc. Engines can operate concurrently and independently using different virtual address spaces.

All engines rely heavily on access to and from memory resources to perform their various functions. The memory subsystem connects engines to the memory resources, and provides services such as address translation, compression, caching, and HW virtualization. The memory subsystem is the heart of the GPU.

Key components of the memory subsystem include:

- Translation Services : Translation Lookaside Buffer (TLB) that translates virtual addresses associated with a context (process) running on an engine, to the physical address space of the GPU or System, and performs page table walks if a request misses in the TLB

- L3 Cache : Level 3 cache that is shared by all engines within the "GT" domain. Engines may have their own Level 1 and Level 2 caches that are not shared.

- LLC : Last Level Cache of the CPU host (only relevant for Integrated GPU)

- L4 Cache : Optional cache between L3 and Memory

- Compression : Handles lossless compression and decompression of memory objects

- System Memory : Memory that is physically attached to the CPU and managed entirely by the Operating System or Hypervisor

- Device Memory : Memory that is physically attached to a discrete GPU, or "stolen" from System Memory for an Integrated GPU, and managed entirely by the GPU device driver

The memory subsystem supports flows that are coherent with CPU memory (including CPU caches), as well as those that are not coherent with CPU memory. In general, non-coherent flows provide higher bandwidth more efficiently than coherent flows, but may require special handling by SW.

The following diagram provides an overview of a typical memory subsystem an Integrated GPU.

#### **Cache and Memory Hierarchy**

### **Graphics Virtual Memory**

The GPU uses a virtual memory address space, where the graphics virtual address is mapped through a Page Table to a physical memory address. Normally, this mapping is set up by the graphics device driver and is private to the GPU context. However, in some cases the graphics virtual address is shared with the CPU - see for more information.

The range of valid graphics virtual addresses, and the types of page tables supported for address translation, varies with the GPU configuration. See the section for a summary the ranges and features supported by a specific graphics device.

Although the range of supported graphics virtual addresses varies, most GPU commands and GPU instructions use a common 64 bit definition for a graphics virtual address. Addresses outside of the supported range are reserved for future address space expansion. See the **GraphicsAddress** structure definition for specific details.

Some GPU devices support an extended graphics virtual memory address mapping called Tiled Resources. When enabled, the Tiled Resources Translation Table (TR-TT) pre-processes graphics virtual addresses. TR-TT maps a graphics virtual memory address either to a new graphics virtual memory address or to a Null Tile. Null Tiles return zero on reads and drop writes. For translations that are not Null Tiles, the new graphics virtual memory address is then used for the graphics virtual address and translated through the normal Page Table to generate a physical memory address.

### **Graphics Translation Tables**

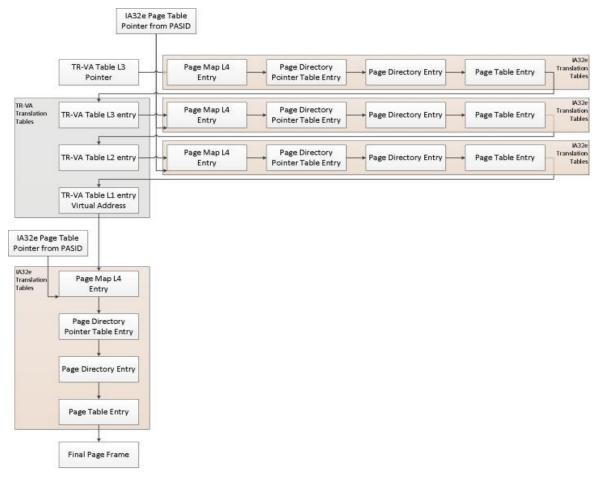

The GPU supports standard virtual memory models as defined by the IA programmer's guide. This section describes the different paging models, their behaviors, and the page table formats.

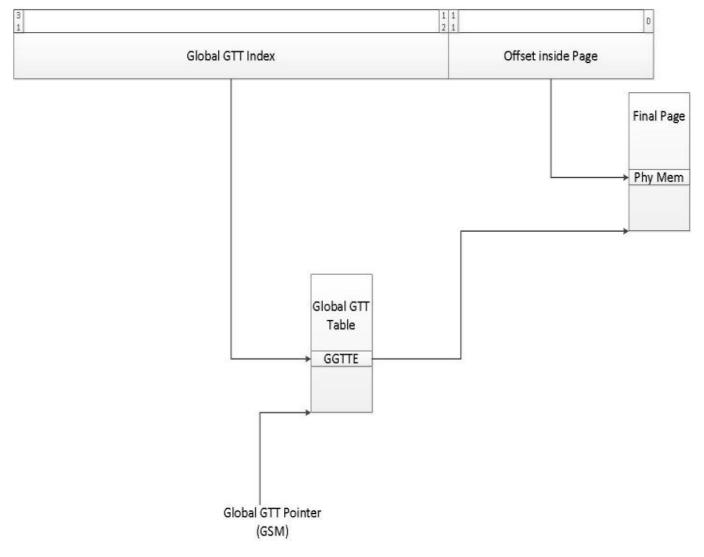

The Graphics Translation Tables (GTT) are memory-resident page tables containing an array of Page Translation Entries (PTEs) used in mapping graphics virtual addresses to physical memory addresses. There are two types of page tables: Global GTT and Per-Process GTT.

The base address of the GGTT and the PPGTT are programmed via the PGTBL\_CTL and PGTBL\_CTL2 MI registers, respectively. The translation table base addresses must be 4KB aligned. The GGTT size is 8MB, to cover 4GB of Global Virtual Address space, and is physically contiguous (ie, "flat"). The global GTT should only be programmed via the MMIO range within the GTTMMADR BAR. The PPGTT is programmed directly in memory and is multi-level. The page tables are further described in later sections.

### **GFX Page Tables**

This section describes the different types of address translation tables used by the GPU.

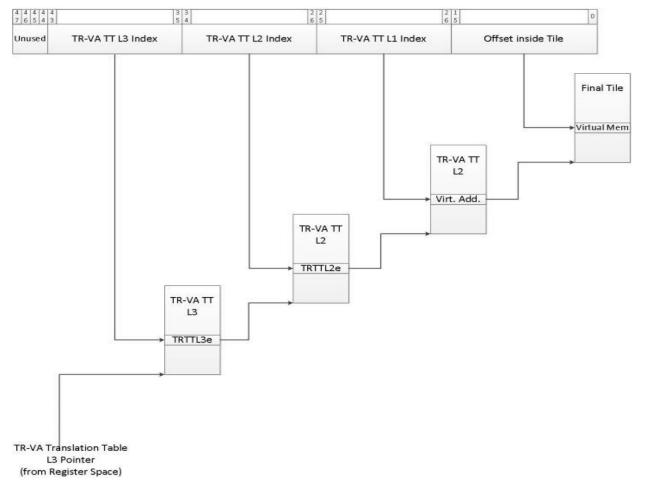

#### **Tiled Resources Translation Tables**

Sparse Tiled Resources can be thought of as a kind of application-controlled virtual memory scheme. The application allocates a resource in a virtual address space. Then the application tells the driver to map specified 64KB tiles within the surface to memory, within resources called Tile Pools. Tiles that are not mapped to a Tile Pool are null tiles.

Tiled Resource Translation Table (TRTT) is constructed as a 3 level tile Table. Each tile is 64KB in size which leaves behind 44-16=28 address bits. 28bits are partitioned as 9+9+10 which corresponds to TRVATT L3, L2 and L1 respectively. This is where TRVATT L3 has 512 entries, L2 has 512 entries and L1 has 1024 entries where each level is contained within a 4KB page hence L3 and L2 is composed of 64b entries and L1 is composed of 32b entries.

| 6 6 6<br>3 2 1 |         | 4 4 4 4<br>9 8 7 6 | <br>3 3 3 3 2 2<br>3 2 1 0 9 8 |        | 1 1 1 1 1 1 1<br>8 7 6 5 4 3 2 | 1 1 9 8 7 6 5 4 3<br>1 0 | 3 2 1 0          |                    |

|----------------|---------|--------------------|--------------------------------|--------|--------------------------------|--------------------------|------------------|--------------------|

|                | Ignored |                    | Address of the TRVA            | ATT-L2 |                                | Ignored                  | NI<br>un<br>II v | TRVATT-L3<br>entry |

| Ignored | Address of the TRVATT-L1 | Ignored | N I<br>un<br>II v |

|---------|--------------------------|---------|-------------------|

|---------|--------------------------|---------|-------------------|

| Tile Virtual Address | TRVATT-L1<br>entry |

|----------------------|--------------------|

|----------------------|--------------------|

The contents of the TRVATT tables are as listed above where L3 and L2 points to the address of the next level which is a 4KB page and L1 contains the 32b VA address pointer needed to map the TR tile to virtual address space.

#### L1 Entry:

| Bits | Field         | Description                                                                           |  |  |

|------|---------------|---------------------------------------------------------------------------------------|--|--|

| 31:0 | ADDR: Address | GFX virtual address of 64KB tile is referenced by this entry.                         |  |  |

|      |               | This field is treated as GFX Virtual Address (GVA) when translated and maps to 47:16. |  |  |

#### L2 Entry:

| Bits  | Field            | Description                                                                                                                                                                                                               |

|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63:48 | Ignored          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                         |

| 47:12 | ADDR:<br>Address | GFX virtual address or Guest Physical Address of 4KB base address pointing to TR-TT L1.<br>TR-TT table entries for L2 and L3 can be in GFX virtual address mode or Guest Physical address<br>mode chosen by GFX software. |

| 11:2  | Ignored          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                         |

| 1     | Null             | Null Tile where reads to this tile returns zero with a Null indicator and writes are dropped.                                                                                                                             |

| 0     | Invalid          | Invalid Tile where reads to this tile returns zero and writes are dropped. Additional interrupt is generated to GFX software when an invalid tile is accessed.                                                            |

### L3 Entry:

| Bits  | Field            | Description                                                                                                                                                                                                               |

|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 63:48 | Ignored          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                         |

| 47:12 | ADDR:<br>Address | GFX virtual address or Guest Physical Address of 4KB base address pointing to TR-TT L2.<br>TR-TT table entries for L2 and L3 can be in GFX virtual address mode or Guest Physical address<br>mode chosen by GFX software. |

| 11:2  | Ignored          | Ignored (h/w does not care about values behind ignored registers)                                                                                                                                                         |

| 1     | Null             | Null Tile where reads to this tile returns zero with a Null indicator and writes are dropped.                                                                                                                             |

| 0     | Invalid          | Invalid Tile where reads to this tile returns zero and writes are dropped. Additional interrupt is generated to GFX software when an invalid tile is accessed.                                                            |

| Programming Note                                                                                                |                                                     |  |  |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|

| Context:                                                                                                        | Tiled ResourceTranslation Tables in Gfx Page Tables |  |  |

| GFX Driver has to disable the TR-TT bypass mode before using tiled resources translation tables. Details of the |                                                     |  |  |

registers are given in "registers for TR-TT management."

| Programming Note                                                 |                                                     |  |

|------------------------------------------------------------------|-----------------------------------------------------|--|

| Context:                                                         | Tiled ResourceTranslation Tables in Gfx Page Tables |  |

| GFX Driver is not allowed to put TR-TT entries into TR-VA space. |                                                     |  |

| Programming Note                                                                       |                                                     |  |

|----------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| Context:                                                                               | Tiled ResourceTranslation Tables in Gfx Page Tables |  |

| Usage model for TR translations are restricted to GFX Render Engine (& POSH pipeline). |                                                     |  |

| Programming Note                                                                                                                                     |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Context: Tiled ResourceTranslation Tables in Gfx Page Tables                                                                                         |  |  |  |  |

| TRTT is only for PPGTT64 (Advanced or Legacy PPGTT64). Enabling TRTT in Legacy PPGTT32 context or GGTT context is considered as invalid programming. |  |  |  |  |

| Programming Note                                                                                                                 |                                                     |  |

|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| Context:                                                                                                                         | Tiled ResourceTranslation Tables in Gfx Page Tables |  |

| When partitioned address space based Dual Context is enabled, bit[47] of the virtual address in L3, L2 and L1                    |                                                     |  |

| When partitioned address space based Dual Context is enabled, bit[47] of the virtual address in L3, L2 and L1 entries must be 0. |                                                     |  |

#### **Registers for TR-TT Management**

Following register is a global mechanism to disable the bypass mode which is considered to be default for h/w. GFX driver has to set this bit to disable bypass mode before using TR-TTs.

Following registers shall be part of the h/w context.

|         | Tiled Resources VA Translation Table L3 Pointer |                                                                                          |                        |                                 |  |

|---------|-------------------------------------------------|------------------------------------------------------------------------------------------|------------------------|---------------------------------|--|

| Registe | er Spac                                         | :e:                                                                                      | MMIO: 0/2/0            |                                 |  |

| DWord   | Bit                                             | Description                                                                              |                        |                                 |  |

| 1       | 63:48                                           | 53:48 Reserved                                                                           |                        |                                 |  |

|         |                                                 | Access:                                                                                  | F                      | RO                              |  |

|         |                                                 | Reserved.                                                                                |                        |                                 |  |

|         | 47:32                                           | Tiled Resource - VA translation Table L3 Poin                                            | ter (Upper Address     | )                               |  |

|         |                                                 | Default Value:                                                                           |                        | 0000h                           |  |

|         |                                                 | Access:                                                                                  |                        | R/W                             |  |

|         |                                                 | Upper address bits for tiled resource VA to virtua                                       | al address translatior | n L3 table.                     |  |

|         |                                                 | For physical memory option, address bits [47:39]<br>limit of physical memory allocation. | has to be programr     | ned to "0" as it is defined the |  |

| 0       | 31:16                                           | Tiled Resource - VA translation Table L3 Poin                                            | ter (Lower Address)    | )                               |  |

|         |                                                 | Default Value:                                                                           |                        | 0000h                           |  |

|         |                                                 | Access:                                                                                  |                        | R/W                             |  |

|         |                                                 | Lower address bits for tiled resource VA to virtua                                       | al address translation | ו L3 table.                     |  |

|         | 15:0                                            | Reserved                                                                                 |                        |                                 |  |

|         |                                                 | Access:                                                                                  | F                      | RO                              |  |

|         |                                                 | Reserved.                                                                                |                        |                                 |  |

|                                                                                  | Tiled Resources Null Tile Detection Register |                                                                                                                                                                                         |             |  |  |

|----------------------------------------------------------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| Register Space:   MMIO: 0/2/0                                                    |                                              |                                                                                                                                                                                         | MMIO: 0/2/0 |  |  |

| DWord Bit Description                                                            |                                              |                                                                                                                                                                                         | cription    |  |  |

| 31:0   Null Tile Detection Value     Default Value:   0000000h     Access:   R/W |                                              |                                                                                                                                                                                         |             |  |  |

|                                                                                  |                                              | 0000000h                                                                                                                                                                                |             |  |  |

|                                                                                  |                                              | R/W                                                                                                                                                                                     |             |  |  |

|                                                                                  |                                              | A 32bit value programmed to enable h/w to perform a match of TR-VA TT entries to detect Null Tiles. Hardware will flag each entry and space behind it as Null Tile for matched entries. |             |  |  |

|                                                                                     | Tiled Resources Invalid Tile Detection Register |                                                                                                                                                                                               |             |  |

|-------------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| Register Space:   MMIO: 0/2/0                                                       |                                                 |                                                                                                                                                                                               | MMIO: 0/2/0 |  |

| DWord Bit Description                                                               |                                                 |                                                                                                                                                                                               | ription     |  |

| 31:0   Invalid Tile Detection Value     Default Value:   0000000h     Access:   R/W |                                                 |                                                                                                                                                                                               |             |  |

|                                                                                     |                                                 | 0000000h                                                                                                                                                                                      |             |  |

|                                                                                     |                                                 | Access:                                                                                                                                                                                       | R/W         |  |

|                                                                                     |                                                 | A 32bit value programmed to enable h/w to perform a match of TR-VA TT entries to detect Invalid Tiles. Hardware will flag each entry and space behind it as Invalid Tile for matched entries. |             |  |

|                                                                                                                                                                                                                                                                                                                                                                      | Tiled Resources Virtual Address Detection Registers (TRVADR) |                       |                                                                                                                                                        |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Registe                                                                                                                                                                                                                                                                                                                                                              | Register Space:   MMIO: 0/2/0                                |                       |                                                                                                                                                        |  |  |

| DWord                                                                                                                                                                                                                                                                                                                                                                | Bit                                                          | Description           |                                                                                                                                                        |  |  |

| 0                                                                                                                                                                                                                                                                                                                                                                    | <sup>31:8</sup> Reserved                                     |                       |                                                                                                                                                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                      |                                                              | Access:               | RO                                                                                                                                                     |  |  |

|                                                                                                                                                                                                                                                                                                                                                                      |                                                              | Reserved.             |                                                                                                                                                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                      | 7:4                                                          | TRVA Mask Value (TRVA | MV)                                                                                                                                                    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                      |                                                              | Default Value:        | 0000b                                                                                                                                                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                      |                                                              | Access:               | R/W                                                                                                                                                    |  |  |

| 4bit MASK value that is mapped to incoming address bits[47:44]. MASK bits are used to which address bits need to be considered for compare. If particular mask bit is "1", map bit needs to be compared to DATA value provided. If "0", corresponding address bit is r makes it don't care for compare ( <i>this field defaults to "0000" to disable detection</i> ) |                                                              |                       | be considered for compare. If particular mask bit is "1", mapping address<br>to DATA value provided. If "0", corresponding address bit is masked which |  |  |

|     | Note that h/w supports two possible values for 44 bit TR-VA space is carved out. | r MASK: "0000" which is disabled case and "1111" |

|-----|----------------------------------------------------------------------------------|--------------------------------------------------|

| 3:0 | ) TRVA Data Value (TRVADV)                                                       |                                                  |

|     | Default Value:                                                                   | 0b                                               |

|     | Access:                                                                          | R/W                                              |

|         |        | Tiled Resources Translation Table                                                                                | Control Register (TRTTE)    |                        |

|---------|--------|------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------|

| Registe | er Spa | ce:                                                                                                              | MMIO: 0/2/0                 |                        |

| DWord   | Bit    | Description                                                                                                      |                             |                        |

| 0       | 31:2   | Reserved                                                                                                         |                             |                        |

|         |        | Access:                                                                                                          | RO                          |                        |

|         |        | Reserved.                                                                                                        |                             |                        |

|         | 1      | TR-VA Translation Table Memory Location                                                                          |                             |                        |

|         |        | Default Value:                                                                                                   |                             | 0b                     |

|         |        | Access:                                                                                                          |                             | R/W                    |

|         |        | This fields specifies whether the translation tables physical (GPA) address space.                               | s for TR-VA to VA are in vi | rtual address space vs |

|         |        | 0: Tables are in Physical (GPA) Space                                                                            |                             |                        |

|         |        | 1: Tables are in Virtual Address Space                                                                           |                             |                        |

|         |        | Tiled Resource Translation Tables in GPA spac<br>should never be set as GPA mode (always set<br>space mode only. |                             |                        |

|         | 0      | TR-TT Enable                                                                                                     |                             |                        |

|         |        | Default Value:                                                                                                   |                             | 0b                     |

|         |        | Access:                                                                                                          |                             | R/W                    |

|         |        | TR translation tables are disabled as default. This translation active.                                          | field needs to be enabled   | l via s/w to get TR    |

The following register (0x4DFC[0]) has enable and disable control of the bypass path across TR translations. By default, bypass is enabled, and bypass needs to be disabled (by setting 0x4DFC[0] = '1) for TR translations to function. Disabling the bypass should be done before render power gating is enabled.

#### **Detection and Treatment of Null and Invalid Tiles**

Two types of definition that need to be extracted from TR-VA walk in addition to reaching the GFX virtual address.

- 1. **Null Tiles**: Null tiles provide the applications the of capability to preventing OS mapping the entire surface. When a memory access hits a Null tile, the access is terminated and zero's are returned to the originator of the memory access for loads along with a null indicator and for stores the access is dropped at the page walker level.

- 2. **Invalid Tiles**: This is the case where GFX software did not update the value of the mapping properly for hardware to separate resident vs null tiles. The Invalid Tile treatment is exactly same however additionally a unique interrupt is generated in h/w

Both detections are done by GPU:

- For L2/L3 entries, Null and Invalid tile information is already embedded in the TR-TT entries

- For L1 entries, the contents (32bits) are compared in hardware to pre-programmed values by GFX software (*values are provided in GFX MMIO space*). For the match values, two separate 32b registers are defined, one for Null Tile detection and one for Invalid Tile detection.

Hardware walking matching the value or detecting L2/L3 would terminate the walk (i.e. rest of the tables are not valid) and define the access as either Null or Invalid.

| Programming Note |                                                                        |  |

|------------------|------------------------------------------------------------------------|--|

| Context:         | Detection and treatment of null and invalid tiles.                     |  |

| The software i   | is not allowed to program both Null and Invalid values to be the same. |  |

| Programming Note                                           |                               |  |  |

|------------------------------------------------------------|-------------------------------|--|--|

| Context:                                                   | TileX Surfaces and Null Tiles |  |  |

| NULL or Invalid Tiles are not supported on TileX surfaces. |                               |  |  |

GPU implements a counter mechanism to roll-up the Null tile accesses detected. The counter value is exposed to GFX software via GFX MMIO.

In implementation, when the TR translation tables are in virtual address domain, the pages faults encountered while walking the IA32e pages are not reported back to the TR walkers or TLBs. These faults are handled as fault & halt, making these faults transparent to the TR walkers. However, when such a fault is not fixed (unsuccessful fault response) or when a non-recoverable fault encountered, main page walker HW converts the cycle to an invalid cycle. Thus, in this case, TR walker or TR TLBs will get incorrect read return data without any notification of the non-recoverable fault condition. Thus, TR walker/TLBs will continue with the TR-walk with incorrect data. This can lead to spurious cycles being generated. However, a Gfx reset/FLR is expected as a result of the non-recoverable fault.

#### **TR-TT Modes**

The L3 table pointer along with TRTTL3e/TRTTL2e is projected to support two modes of address space. Original intent was to have the contents to be in Virtual Address space (OS managed) and have them to be translated to GPA to HPA before getting accessed. Such mechanism will incur high latency penalties due to nested page translations. GPU shall have an additional mode where tiled-resources translation tables are in physical address space (GPA) and eliminate the need to have nested translations to reduce the potentially high miss latencies.

TR-TT walker shall have both modes supported. The Mode bit will be part of the same Register that provides TR-VA TT L3 pointer.

### **Memory Types and Cache Interface**

This section has additional information on the types of memory which are accessible via the various GT mechanisms. It includes discussion on how the various paging models are used and accessed. See the Graphics Translation Tables for more detailed discussions on paging models.

This section also includes descriptions of how different surface types (MOCS) can be cached in the L3 and the different behaviors which can be enabled.

### Memory Object Control State (MOCS)

The memory object control state defines the behavior of memory accesses beyond the graphics core, including encryption, graphics data types that allow selective flushing of data from outer caches, and controlling cacheability in the outer caches.

This control uses several mechanisms. Control state for all memory accesses can be defined page by page in the GTT entries. Memory objects that are defined by state per surface generally have additional memory object control state in the state structure that defines the other surface attributes. Memory objects without state defining them have memory object state control defined per class in the STATE\_BASE\_ADDRESS command, with class divisions the same as the base addresses. Finally, some memory objects only have the GTT entry mechanism for defining this control. The table below enumerates the memory objects and the location of the control state for each:

| Memory Object                                                                                                                               | Location of Control State                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| surfaces defined by SURFACE_STATE: sampling engine surfaces, render targets, media surfaces, pull constant buffers, streamed vertex buffers | SURFACE_STATE                                                  |

| depth, stencil, and hierarchical depth buffers                                                                                              | corresponding state command that defined the buffer attributes |

| stateless buffers accessed by data port                                                                                                     | STATE_BASE_ADDRESS                                             |

| indirect state objects                                                                                                                      | STATE_BASE_ADDRESS                                             |

| kernel instructions                                                                                                                         | STATE_BASE_ADDRESS                                             |

| push constant buffers                                                                                                                       | 3DSTATE_CONSTANT_(VS   GS   PS)                                |

| index buffers                                                                                                                               | 3DSTATE_INDEX_BUFFER                                           |

| vertex buffers                                                                                                                              | 3DSTATE_VERTEX_BUFFERS                                         |

| indirect media object                                                                                                                       | STATE_BASE_ADDRESS                                             |

| generic state prefetch                                                                                                                      | GTT control only                                               |

| ring/batch buffers                                                                                                                          | GTT control only                                               |

| context save buffers                                                                                                                        | GTT control only                                               |

| store DWord                                                                                                                                 | GTT control only                                               |

### **MOCS Registers**

These registers provide the detailed format of the MOCS table entries, that need to be programmed to define each surface state.

|                          | MEMORY_OBJECT_CONTROL_STATE |                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|--------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Size (in b               | Size (in bits): 7           |                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Default Value: 0x0000000 |                             | 0x0000000                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| DWord                    | Bit                         | Description                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                          |                             | <b>Index to MOCS Tables</b><br>The index to define the L3 and system cache memory properties. The details of the controls are further defined in L3 and Page walker (memory interface) control registers. The field is defined to populate 64 different surface controls to be used concurrently. Related control registers can be updated during runtime.                        |  |  |  |

| 0                        | 6:1                         | Programming Notes                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 0                        |                             | When an access is made through Data Port and the index to MOCS[6:1] = [48,59] (decimal), that surface or stateless memory access can be cached in HDC L1 cache.<br>Accesses made through Data Port with MOCS[6:1] < 48 or > 59 will bypass the HDC L1 cache. L1 cache. This bypass is useful when software wants to ensure that Data Port access are coherent with the L3 memory. |  |  |  |

|                          | 0                           | Reserved                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

### **L3 Control Registers**

64x16b control registers are defined within L3 space to interpret MOCS indexing and map it to cache events.

The incoming MOCS value is used to index into one of these registers which hardware uses as control parameters for a given surface. It allows 64 concurrent surface definitions with unique control values for L3 caching.

Also attached are the default settings for each 64 locations if driver chooses to use as is.

Following 16b defines per selection definition:

Register#64 (MOCS value 63) is reserved for h/w use and should not be used by s/w.

#### In L3 Node: B020-B09F (128 Bytes). Please refer to the register section for default values.

| Bits | Description                                                                                                                                                                                                                    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16:6 | Reserved.                                                                                                                                                                                                                      |

| 5:4  | L3 Cacheability Control (L3CC).                                                                                                                                                                                                |

|      | Memory type information used in L3. This field is combined with the additional two bits that are sent by HDC based on binding table index. For all other L3 requesters, this field is the primary source of L3 cache controls. |

|      | 00b: Use binding table index for direct EU accesses - for rest it is reserved.                                                                                                                                                 |

|      | 01b: Uncacheable (UC) - non-cacheable.                                                                                                                                                                                         |

|      | 10b: Reserved                                                                                                                                                                                                                  |

|      | 11b: Writeback (WB).                                                                                                                                                                                                           |

| 3:1  | Skip Caching Control (SCC).                                                                                                                                                                                                    |

|      | Defines the bit values to enable caching. Outcome overrides the L3caching for the surface.                                                                                                                                     |

|      | If "0" - than corresponding address bit value is don't care.                                                                                                                                                                   |

|      | Bit[1]=1: Address bit[9] needs to be "0" to cache in target.                                                                                                                                                                   |

|      | Bit[2]=1: Address bit[10] needs to be "0" to cache in target.                                                                                                                                                                  |

|      | Bit[3]=1: Address bit[11] needs to be "0" to cache in target.                                                                                                                                                                  |

| 0    | Enable Skip Caching (ESC).                                                                                                                                                                                                     |

|      | Enable for the Skip cache mechanism.                                                                                                                                                                                           |

|      | 0: Not enabled.                                                                                                                                                                                                                |

|      | 1: Enabled for L3.                                                                                                                                                                                                             |

### **Memory Interface Control Registers**

64x32b control registers are defined within the page walker where control parameters for LLC/eDRAM caching are defined. Incoming memory control object state index is used to do a look up into the table where the corresponding control parameters are picked for a given surface. These control values are used to control LLC/eDRAM caching.

For EU surfaces where binding table index is used, we also pass two bits of information in the hardware.

Following 32b defines per selection definition:

All MOCS registers are global and need to be saved/restored on RC6 entry/exit.

Certain MOCS indices are used by hardware and carry special meanings. These indices are restricted from being used for regular surfaces. In the following list, the indices are 0 based (i.e., MOCS index 0 is the first register and MOCS index 63 is the last register.)

- Index 'd63 is used for two purposes.

- It is used by the L3 for all its evictions. The programming of the index 'd63 is expected to allow LLC cacheability to enable coherent flows to be maintained.

- It is also used by hardware to force L3 uncacheable cycles. The programming of the index #63 is expected to make the surface L3 uncacheable.

- Index 'd62

- This index is used for Tiled-Resources page walker accesses in previous projects.

- This index is used for AuxTT Nodes for current projects.

- Index 'd61 is used for displayable surfaces. The programming of the index 'd61 is expected to disallow LLC cacheability for the surface to be displayable.

- Index 'd60 is reserved for use in the 3D CCS accesses.

| Bits  | Description                                                                                                                                                                                                                                                   |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:19 | Reserved                                                                                                                                                                                                                                                      |

| 18:17 | Self Snoop Enable                                                                                                                                                                                                                                             |

|       | 00: Default value. Self snoop attribute sent to the uncore is as normal - determined by MIDI unit logic                                                                                                                                                       |

|       | 01: Override the self snoop bit generated by MIDI with 0. No self snoops are sent to the uncore for any transactions from this surface                                                                                                                        |

|       | 11: Override the self snoop bit generated by MIDI with 1. Self snoops are always sent to the uncore for any transactions from this surface                                                                                                                    |

| 16:15 | Class of Service                                                                                                                                                                                                                                              |

|       | This field controls the Class of Service sent to the LLC to determine which sub-set of Ways the surface will be stored in. The allocation of certain LLC ways to different class of service settings is a project dependent decision and listed in the Bspec. |

|       | 00: Value from Private PAT Registers(40E0/40E4/40E8/40EC)<br>01: Class 1<br>10: Class 2                                                                                                                                                                       |

| Bits  | Description                                                                                                                                                                                                                                                                                                                                                                            |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 11: Class 3                                                                                                                                                                                                                                                                                                                                                                            |

| 14    | Snoop Control Field (SCF):                                                                                                                                                                                                                                                                                                                                                             |

|       | Enables s/w to have GFX h/w to be able to consume IA generated buffers that are tagged as WB. Driver can mark these buffers as WB when generating them from IA. In LP-SOCs, the fabric is not forced to be coherent all the time. IA-core generated WB buffers can only be consumed by GPU if that buffer is tagged as snoop-able in GPUs buffer definitions (or via GPU Page tables). |

|       | 1: Non-Coherent Write/Read                                                                                                                                                                                                                                                                                                                                                             |

|       | 0: Coherent Access                                                                                                                                                                                                                                                                                                                                                                     |

| 13:11 | Page Faulting Mode                                                                                                                                                                                                                                                                                                                                                                     |

|       | This fields controls the page faulting mode that will be used in the memory interface block for the given request coming from this surface:                                                                                                                                                                                                                                            |

|       | 000: Use the global page faulting mode from context descriptor (default)                                                                                                                                                                                                                                                                                                               |

|       | 001-111: Reserved                                                                                                                                                                                                                                                                                                                                                                      |

| 10:8  | Skip Caching Control                                                                                                                                                                                                                                                                                                                                                                   |

|       | Defines the bit values to enable caching. Outcome overrides the LLC caching for the surface.                                                                                                                                                                                                                                                                                           |

|       | If "0" - than corresponding address bit value is do not care                                                                                                                                                                                                                                                                                                                           |

|       | Bit[8]=1: address bit[9] needs to be "0" to cache in target                                                                                                                                                                                                                                                                                                                            |

|       | Bit[9]=1: address bit[10] needs to be "0" to cache in target                                                                                                                                                                                                                                                                                                                           |

|       | Bit[10]=1: address bit[11] needs to be "0" to cache in target                                                                                                                                                                                                                                                                                                                          |

|       | The default value of this field is '000. <b>For coherent surfaces, skip caching should not be enabled, as not caching in LLC breaks the coherency.</b>                                                                                                                                                                                                                                 |

| 7     | Enable Reverse Skip Caching                                                                                                                                                                                                                                                                                                                                                            |

|       | Enable for the Skip cache mechanism                                                                                                                                                                                                                                                                                                                                                    |

|       | 0: Not enabled<br>1: Enabled for LLC                                                                                                                                                                                                                                                                                                                                                   |

| 6     | Don't Allocate on miss                                                                                                                                                                                                                                                                                                                                                                 |

|       | Controls defined for RO surfaces in mind, where if the target cache is missed - do not bring the line<br>(applicable to LLC/eDRAM).                                                                                                                                                                                                                                                    |

|       | 0: Allocate on MISS (normal cache behavior)                                                                                                                                                                                                                                                                                                                                            |

|       | 1: Do NOT allocate on MISS                                                                                                                                                                                                                                                                                                                                                             |

| 5:4   | LRU (Cache Replacement) Management (LRUM).                                                                                                                                                                                                                                                                                                                                             |

|       | This field allows the selection of AGE parameter for a given surface in LLC or eLLC. If a particular allocation is done at youngest age ("3") it tends to stay longer in the cache as compared to older age allocations ("2", "1",                                                                                                                                                     |

| Bits | Description                                                                                                                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | or "0"). This option is given to driver to be able to decide which surfaces are more likely to generate HITs, hence need to be replaced least often in caches. |

|      | 00: Take the age value from Uncore CRs.                                                                                                                        |

|      | 01: Assign the age of "0"                                                                                                                                      |

|      | 10: Don't change the age on a hit.                                                                                                                             |

|      | 11: Assign the age of "3"                                                                                                                                      |

| 3:2  | Target Cache (TC).                                                                                                                                             |

|      | This field allows the choice of LLC vs eLLC for caching.                                                                                                       |

|      | 00b: Use TC/LRU controls from page table                                                                                                                       |

|      | 01b: LLC Only.                                                                                                                                                 |

|      | 10b: LLC/eLLC Allowed.                                                                                                                                         |

|      | 11b: LLC/eLLC Allowed.                                                                                                                                         |

|      | For coherent surfaces ensure that LLC caching is enabled - even when using target cache controls from page table.                                              |

| 1:0  | LLC/eDRAM Cacheability Control (LeCC).                                                                                                                         |

|      | Memory type information used in LLC/eDRAM.                                                                                                                     |

|      | 00b: Use Cacheability Controls from page table / UC with Fence (if coherent cycle).                                                                            |

|      | 01b: Uncacheable (UC) - non-cacheable.                                                                                                                         |

|      | 10b: Writethrough (WT).                                                                                                                                        |

|      | 11b: Writeback (WB).                                                                                                                                           |

|      | <b>Note:</b> In case of SVM (advanced context), LLC/eDRAM memory type is used based on the page table controls and cannot be managed via MOCS index.           |

#### **Defaults Table**

| Default | LeCC | тс | LRUM | AOM | ESC | SCC | PFM | Default | LeCC | тс | LRUM | AOM | ESC | SCC | PFM |

|---------|------|----|------|-----|-----|-----|-----|---------|------|----|------|-----|-----|-----|-----|

| 000000  | 00   | 00 | 11   | 0   | 0   | 00  | 000 | 000000  | 00   | 00 | 11   | 0   | 0   | 00  | 000 |

| 000001  | 00   | 01 | 11   | 0   | 0   | 00  | 000 | 000001  | 00   | 01 | 11   | 0   | 0   | 00  | 000 |

| 000010  | 00   | 10 | 11   | 0   | 0   | 00  | 000 | 000010  | 00   | 10 | 11   | 0   | 0   | 00  | 000 |

| 000011  | 01   | 00 | 11   | 0   | 0   | 00  | 000 | 000011  | 01   | 00 | 11   | 0   | 0   | 00  | 000 |

| 000100  | 10   | 00 | 11   | 0   | 0   | 00  | 000 | 000100  | 10   | 00 | 11   | 0   | 0   | 00  | 000 |

| 000101  | 10   | 01 | 11   | 0   | 0   | 00  | 000 | 000101  | 10   | 01 | 11   | 0   | 0   | 00  | 000 |

| 000110  | 10   | 10 | 11   | 0   | 0   | 00  | 000 | 000110  | 10   | 10 | 11   | 0   | 0   | 00  | 000 |

| 000111  | 11   | 00 | 11   | 0   | 0   | 00  | 000 | 000111  | 11   | 00 | 11   | 0   | 0   | 00  | 000 |

| 001000  | 11   | 01 | 11   | 0   | 0   | 00  | 000 | 001000  | 11   | 01 | 11   | 0   | 0   | 00  | 000 |

| 001001  | 11   | 10 | 11   | 0   | 0   | 00  | 000 | 001001  | 11   | 10 | 11   | 0   | 0   | 00  | 000 |

| 001010  | 10   | 00 | 11   | 0   | 0   | 00  | 000 | 001010  | 10   | 00 | 11   | 0   | 0   | 00  | 000 |

| 001011  | 10   | 01 | 11   | 0   | 0   | 00  | 000 | 001011  | 10   | 01 | 11   | 0   | 0   | 00  | 000 |

| 001100  | 10   | 10 | 11   | 0   | 0   | 00  | 000 | 001100  | 10   | 10 | 11   | 0   | 0   | 00  | 000 |

| 001101  | 11   | 00 | 11   | 0   | 0   | 00  | 000 | 001101  | 11   | 00 | 11   | 0   | 0   | 00  | 000 |

| 001110  | 11   | 01 | 11   | 0   | 0   | 00  | 000 | 001110  | 11   | 01 | 11   | 0   | 0   | 00  | 000 |