# Intel® Open Source HD Graphics and Intel Iris™ Plus Graphics

# **Programmer's Reference Manual**

For the 2016 - 2017 Intel Core™ Processors, Celeron™ Processors, and Pentium™ Processors based on the "Kaby Lake" Platform

Volume 6: Command Stream Programming

January 2017, Revision 1.0

#### **Creative Commons License**

**You are free to Share** - to copy, distribute, display, and perform the work under the following conditions:

- **Attribution.** You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

- No Derivative Works. You may not alter, transform, or build upon this work.

#### **Notices and Disclaimers**

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\* Other names and brands may be claimed as the property of others.

**Copyright © 2017, Intel Corporation. All rights reserved.**

## **Table of Contents**

| Graphics Command Formats                                  | 1  |

|-----------------------------------------------------------|----|

| Command Header                                            | 2  |

| Memory Interface Commands                                 | 5  |

| 2D Commands                                               | 7  |

| 3D Commands                                               | 8  |

| VEBOX Commands                                            | 13 |

| MFX Commands                                              | 13 |

| Scheduling                                                | 15 |

| RINGBUF — Ring Buffer Registers                           | 15 |

| Command Stream Virtual Memory Control                     | 15 |

| Execlists                                                 | 15 |

| Execlist Structure                                        | 16 |

| Overall Context Layout                                    | 17 |

| Context Layout                                            | 17 |

| Ring Context                                              | 17 |

| Ring Buffer                                               | 17 |

| Context Descriptor Format                                 | 18 |

| Logical Ring Context Format                               | 18 |

| Context Status                                            | 20 |

| Render Engine Command Streamer (RCS)                      | 23 |

| Batch Buffer Privilege Register                           | 23 |

| Mode Registers                                            | 24 |

| Logical Context Support                                   | 24 |

| Context Save Registers                                    | 25 |

| MI Commands for Render Engine                             |    |

| Watchdog Timer Registers                                  | 26 |

| Interrupt Control Registers                               | 27 |

| Hardware-Detected Error Bit Definitions (for EIR EMR ESR) | 28 |

| Blitter Engine Command Streamer (BCS)                     | 29 |

| Logical Context Support                                   | 30 |

| Mode Registers                                            | 31 |

| MI Commands for Blitter Engine                   | 32 |

|--------------------------------------------------|----|

| Video Command Streamer (VCS)                     | 33 |

| Watchdog Timer Registers                         | 34 |

| Logical Context Support                          | 34 |

| Mode Registers                                   | 35 |

| Registers in Media Engine                        | 35 |

| GFX Pending TLB Cycles Information Registers     | 35 |

| Memory Interface Commands for Video Codec Engine | 36 |

| Video Enhancement Engine Command Interface       | 37 |

| VECS_RINGBUF — Ring Buffer Registers             | 37 |

| Logical Context Support                          | 37 |

| Mode Registers                                   | 38 |

| MI Commands for Video Enhancement Engine         | 38 |

| Watchdog Timers                                  | 39 |

| The Per-Process Hardware Status Page             | 40 |

| Preemption                                       | 41 |

| Ring Buffer Scheduling                           | 41 |

| ExecList Scheduling                              | 42 |

| Command Streamer (CS) ALU Programming            | 43 |

| MI Commands for Graphics Processing Engines      | 44 |

| User Mode Privileged Commands                    | 44 |

## **Graphics Command Formats**

This section describes the general format of the graphics device commands.

Graphics commands are defined with various formats. The first DWord of all commands is called the *header* DWord. The header contains the only field common to all commands, the *client* field that determines the device unit that processes the command data. The Command Parser examines the client field of each command to condition the further processing of the command and route the command data accordingly.

Graphics commands vary in length, though are always multiples of DWords. The length of a command is either:

- Implied by the client/opcode

- Fixed by the client/opcode yet included in a header field (so the Command Parser explicitly knows how much data to copy/process)

- Variable, with a field in the header indicating the total length of the command

Note that command *sequences* require QWord alignment and padding to QWord length to be placed in Ring and Batch Buffers.

The following subsections provide a brief overview of the graphics commands by client type provides a diagram of the formats of the header DWords for all commands. Following that is a list of command mnemonics by client type.

### **Command Header**

#### **Render Command Header Format**

|                             |             |                                                            | Bits                                                                                                                                 |            |                   |                     |             |

|-----------------------------|-------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------|---------------------|-------------|

| ТҮРЕ                        | 31:29       |                                                            | 28:24                                                                                                                                | 23         | 22                |                     | 21:0        |

| Memory<br>Interface<br>(MI) | 000         | 00h – N<br>0Xh – S<br>Comma<br>1Xh – 1<br>Comma<br>2Xh – S | Opcode  00h – NOP  0Xh – Single DWord  Commands  1Xh – Two+ DWord  Commands  2Xh – Store Data Commands  3Xh – Ring/Batch Buffer Cmds |            |                   | rd Count            |             |

| Reserved                    | 001,<br>010 | Opcode                                                     |                                                                                                                                      |            | 18:16<br>Reserved | 15:0<br>DWord Count |             |

| ТҮРЕ                        | 31:29       | 28:27                                                      | 26:24                                                                                                                                | 23:16      |                   | 15:8                | 7:0         |

| Common                      | 011         | 00                                                         | Opcode – 000                                                                                                                         | Sub Opcod  | e                 | Data                | DWord Count |

| Common (NP) <sup>1</sup>    | 011         | 00                                                         | Opcode – 001                                                                                                                         | Sub Opcod  | e                 | Data                | DWord Count |

| Reserved                    | 011         | 00                                                         | Opcode – 010 – 111                                                                                                                   |            |                   |                     |             |

| Single Dword<br>Command     | 011         | 01                                                         | Opcode – 000 – 001                                                                                                                   | Sub Opcode |                   |                     | N/A         |

| Reserved                    | 011         | 01                                                         | Opcode – 010 – 111                                                                                                                   |            |                   |                     |             |

| Media State                 | 011         | 10                                                         | Opcode – 000                                                                                                                         | Sub Opcod  | е                 |                     | Dword Count |

| Media Object                | 011         | 10                                                         | Opcode – 001 – 010                                                                                                                   | Sub Opcod  | е                 | Dword Cou           | int         |

| Reserved                    | 011         | 10                                                         | Opcode – 011 – 111                                                                                                                   |            |                   |                     |             |

| 3DState                     | 011         | 11                                                         | Opcode – 000                                                                                                                         | Sub Opcod  | е                 | Data                | DWord Count |

| 3DState (NP) <sup>1</sup>   | 011         | 11                                                         | Opcode – 001                                                                                                                         | Sub Opcod  | е                 | Data                | DWord Count |

| PIPE_Control                | 011         | 11                                                         | Opcode – 010                                                                                                                         |            |                   | Data                | DWord Count |

| 3DPrimitive                 | 011         | 11                                                         | Opcode – 011                                                                                                                         |            |                   | Data                | DWord Count |

| Reserved                    | 011         | 11                                                         | Opcode – 100 – 111                                                                                                                   |            |                   |                     |             |

| Reserved                    | 100         | XX                                                         |                                                                                                                                      |            |                   |                     |             |

| Reserved                    | 101         | XX                                                         |                                                                                                                                      |            |                   |                     |             |

| Reserved                    | 110         | XX                                                         |                                                                                                                                      |            |                   |                     |             |

#### **Notes:**

<sup>1</sup>The qualifier "NP" indicates that the state variable is non-pipelined and the render pipe is flushed before such a state variable is updated. The other state variables are pipelined (default).

## **Video Command Header Format**

|                             |       |                                | Bits                                                   |      |                                                                                                                         |           |                       |

|-----------------------------|-------|--------------------------------|--------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------|

| ТҮРЕ                        | 31:29 |                                | 28:24                                                  | 23   | 22                                                                                                                      |           | 21:0                  |

| Memory<br>Interface<br>(MI) | 000   | 1Xh – Reserve<br>2Xh – Store D | OWord Commands<br>d<br>ata Commands<br>tch Buffer Cmds |      | Identification No./DWord Count<br>Command Dependent Data<br>5:0 – DWord Count<br>5:0 – DWord Count<br>5:0 – DWord Count |           | dent Data<br>nt<br>nt |

| ТҮРЕ                        | 31:29 | 28:27                          | 26:24                                                  |      | 2                                                                                                                       | 23:16     | 15:0                  |

| Reserved                    | 011   | 00                             | XXX                                                    | XX   |                                                                                                                         |           |                       |

| MFX Single DW               | 011   | 01                             | 000                                                    | Орс  | ode: (                                                                                                                  | 0h        | 0                     |

| Reserved                    | 011   | 01                             | 1XX                                                    |      |                                                                                                                         |           |                       |

| Reserved                    | 011   | 10                             | 0XX                                                    |      |                                                                                                                         |           |                       |

| AVC State                   | 011   | 10                             | 100                                                    | Орс  | ode:                                                                                                                    | 0h – 4h   | DWord Count           |

| AVC Object                  | 011   | 10                             | 100                                                    | Орс  | ode:                                                                                                                    | 8h        | DWord Count           |

| VC1 State                   | 011   | 10                             | 101                                                    | Орс  | ocode: 0h – 4h                                                                                                          |           | DWord Count           |

| VC1 Object                  | 011   | 10                             | 101                                                    | Орс  | pcode: 8h                                                                                                               |           | DWord Count           |

| Reserved                    | 011   | 10                             | 11X                                                    |      |                                                                                                                         |           |                       |

| Reserved                    | 011   | 11                             | XXX                                                    |      |                                                                                                                         |           |                       |

| ТҮРЕ                        | 31:29 | 28:27                          | 26:24                                                  | 23   | :21                                                                                                                     | 20:16     | 15:0                  |

| MFX Common                  | 011   | 10                             | 000                                                    | 000  |                                                                                                                         | subopcode | DWord Count           |

| Reserved                    | 011   | 10                             | 000                                                    | 001- | -111                                                                                                                    | subopcode | DWord Count           |

| AVC Common                  | 011   | 10                             | 001                                                    | 000  |                                                                                                                         | subopcode | DWord Count           |

| AVC Dec                     | 011   | 10                             | 001                                                    | 001  |                                                                                                                         | subopcode | DWord Count           |

| AVC Enc                     | 011   | 10                             | 001                                                    | 010  |                                                                                                                         | subopcode | DWord Count           |

| Reserved                    | 011   | 10                             | 001                                                    | 011- | 111                                                                                                                     | subopcode | DWord Count           |

| Reserved (for VC1 Common)   | 011   | 10                             | 010                                                    | 000  |                                                                                                                         | subopcode | DWord Count           |

| VC1 Dec                     | 011   | 10                             | 010                                                    | 001  |                                                                                                                         | subopcode | DWord Count           |

| Reserved (for VC1 Enc)      | 011   | 10                             | 010                                                    | 010  |                                                                                                                         | subopcode | DWord Count           |

| Reserved                    | 011   | 10                             | 010                                                    | 011- | -111                                                                                                                    | subopcode | DWord Count           |

| Reserved (MPEG2 Common)     | 011   | 10                             | 011                                                    | 000  |                                                                                                                         | subopcode | DWord Count           |

| MPEG2 Dec                   | 011   | 10                             | 011                                                    | 001  |                                                                                                                         | subopcode | DWord Count           |

| Reserved (for MPEG2 Enc)    | 011   | 10                             | 011                                                    | 010  |                                                                                                                         | subopcode | DWord Count           |

| Reserved                    | 011   | 10                             | 011                                                    | 011- | -111                                                                                                                    | subopcode | DWord Count           |

| Reserved                    | 011   | 10                             | 100-111                                                | XXX  |                                                                                                                         |           |                       |

## **Video Enhancement Command Header Format**

|                             | Bits     |                                                                                                                               |    |                                                                                         |                           |  |

|-----------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------------------------------------------------------------|---------------------------|--|

| TYPE                        | 31:29    | 28:24                                                                                                                         | 23 | 22                                                                                      | 21:0                      |  |

| Memory<br>Interface<br>(MI) | 000      | Opcode 00h – NOP 0Xh – Single DWord Commands 1Xh – Two+ DWord Commands 2Xh – Store Data Commands 3Xh – Ring/Batch Buffer Cmds |    | Identification No<br>Command Depe<br>5:0 – DWord Co<br>5:0 – DWord Co<br>5:0 – DWord Co | endent Data<br>unt<br>unt |  |

| Reserved                    | 001, 010 |                                                                                                                               |    |                                                                                         |                           |  |

| ТҮРЕ                           | 31:29 | 28:27                                               | 26:24                   | 23:21           | 20:16           | 15:12    | 11:0           |

|--------------------------------|-------|-----------------------------------------------------|-------------------------|-----------------|-----------------|----------|----------------|

| VEBOX (Parallel<br>Video Pipe) | 011   | 10: Pipeline 00: Reserved 01: Reserved 11: Reserved | Command Opcode –<br>100 | Sub Opcode<br>A | Sub Opcode<br>B | Reserved | Dword<br>Count |

## **Blitter Command Header Format**

|                             | Bits     |                                                                                                                                    |    |                                                                                         |                             |  |  |

|-----------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------------------------------------------------------------|-----------------------------|--|--|

| TYPE                        | 31:29    | 28:24                                                                                                                              | 23 | 22                                                                                      | 21:0                        |  |  |

| Memory<br>Interface<br>(MI) | 000      | Opcode  00h – NOP  0Xh – Single DWord Commands  1Xh – Two+ DWord Commands  2Xh – Store Data Commands  3Xh – Ring/Batch Buffer Cmds |    | Identification No<br>Command Depe<br>5:0 – DWord Co<br>5:0 – DWord Co<br>5:0 – DWord Co | endent Data<br>ount<br>ount |  |  |

| Reserved                    | 001, 011 |                                                                                                                                    |    |                                                                                         |                             |  |  |

| ТҮРЕ         | 31:29 | 28:22          | 21:9                   | 8:0         |

|--------------|-------|----------------|------------------------|-------------|

| Blitter (2D) | 010   | Command Opcode | Command Dependent Data | Dword Count |

## **Memory Interface Commands**

Memory Interface (MI) commands are basically those commands which do not require processing by the 2D or 3D Rendering/Mapping engines. The functions performed by these commands include:

- Control of the command stream (e.g., Batch Buffer commands, breakpoints, ARB On/Off, etc.)

- Hardware synchronization (e.g., flush, wait-for-event)

- Software synchronization (e.g., Store DWORD, report head)

- Graphics buffer definition (e.g., Display buffer, Overlay buffer)

- Miscellaneous functions

All of the following commands are defined in *Memory Interface Commands*.

#### **Memory Interface Commands for RCP**

| Opcode<br>(28:23) | Command                          | Pipes              |  |

|-------------------|----------------------------------|--------------------|--|

|                   | 1 DWord                          |                    |  |

| 00h               | MI_NOOP                          | All                |  |

| 01h               | MI_SET_PREDICATE                 | Render             |  |

| 02h               | MI_USER_INTERRUPT                | All                |  |

| 03h               | MI_WAIT_FOR_EVENT                | All                |  |

| 05h               | MI_ARB_CHECK                     | All                |  |

| 06h               | MI_RS_CONTROL                    | Render             |  |

| 07h               | MI_REPORT_HEAD                   | All                |  |

| 08h               | MI_ARB_ON_OFF All except Blitter |                    |  |

| 09h               | MI_URB_ATOMIC_ALLOC Render       |                    |  |

| 0Ah               | MI_BATCH_BUFFER_END All          |                    |  |

| 0Bh               | MI_SUSPEND_FLUSH All             |                    |  |

| 0Ch               | MI_PREDICATE Render              |                    |  |

| 0Fh               | MI_RS_CONTEXT                    | Render             |  |

|                   | 2+ DWord                         |                    |  |

| 10h               | Reserved                         |                    |  |

| 14h               | MI_DISPLAY_FLIP                  | Render and Blitter |  |

| 15h               | Reserved                         |                    |  |

| 16h               | MI_SEMAPHORE_MBOX All            |                    |  |

| 17h               | Reserved                         |                    |  |

| 18h               | MI_SET_CONTEXT Render            |                    |  |

| 1Ah               | MI_MATH                          | All                |  |

| 1Bh               | MI_SEMAPHORE_SIGNAL              | All                |  |

| Opcode  |                                 |                   |

|---------|---------------------------------|-------------------|

| (28:23) | Command                         | Pipes             |

|         | 1 DWord                         | 1                 |

| 1Ch     | MI_SEMAPHORE_WAIT               | All               |

| 1Dh     | MI_FORCE_WAKEUP                 | All except Render |

| 1Fh     | Reserved                        |                   |

|         | Store Data                      |                   |

| 20h     | MI_STORE_DATA_IMM               | All               |

| 21h     | MI_STORE_DATA_INDEX             | All               |

| 22h     | MI_LOAD_REGISTER_IMM            | All               |

| 23h     | MI_UPDATE_GTT                   | All               |

| 24h     | MI_STORE_REGISTER_MEM           | All               |

| 26h     | MI_FLUSH_DW                     | All except Render |

| 27h     | MI_CLFLUSH                      | Render            |

| 29h     | MI_LOAD_REGISTER_MEM            | All               |

| 2Ah     | MI_LOAD_REGISTER_REG            | All               |

| 2Bh     | MI_RS_STORE_DATA_IMM            | Render            |

| 2Ch     | MI_LOAD_URB_MEM                 | Render            |

| 2Dh     | MI_STORE_URB_MEM                | Render            |

| 2Eh     | MI_MEM_TO_MEM                   | All               |

| 2Fh     | MI_ATOMIC                       | All               |

|         | Ring/Batch Buffer               |                   |

| 30h     | Reserved                        |                   |

| 31h     | MI_BATCH_BUFFER_START           | Render            |

| 32h-35h | Reserved                        |                   |

| 36h     | MI_CONDITIONAL_BATCH_BUFFER_END | All               |

| 37h-38h | Reserved                        |                   |

| 39h-3Fh | Reserved                        |                   |

#### **2D Commands**

The 2D commands include various flavors of BLT operations, along with commands to set up BLT engine state without actually performing a BLT. Most commands are of fixed length, though there are a few commands that include a variable amount of "inline" data at the end of the command.

All the following commands are defined in *Blitter Instructions*.

## **2D Command Map**

| Opcode (28:22) | Command                           |

|----------------|-----------------------------------|

| 00h            | Reserved                          |

| 01h            | XY_SETUP_BLT                      |

| 02h            | Reserved                          |

| 03h            | XY_SETUP_CLIP_BLT                 |

| 04h-10h        | Reserved                          |

| 11h            | XY_SETUP_MONO_PATTERN_SL_BLT      |

| 12h-23h        | Reserved                          |

| 24h            | XY_PIXEL_BLT                      |

| 25h            | XY_SCANLINES_BLT                  |

| 26h            | XY_TEXT_BLT                       |

| 27h-30h        | Reserved                          |

| 31h            | XY_TEXT_IMMEDIATE_BLT             |

| 32h-3Fh        | Reserved                          |

| 40h            | COLOR_BLT                         |

| 41h            | Reserved                          |

| 42h            | XY_FAST_COPY_BLT                  |

| 43h            | SRC_COPY_BLT                      |

| 44h            | Reserved                          |

| 45h-4Fh        | Reserved                          |

| 50h            | XY_COLOR_BLT                      |

| 51h            | XY_PAT_BLT                        |

| 52h            | XY_MONO_PAT_BLT                   |

| 53h            | XY_SRC_COPY_BLT                   |

| 54h            | XY_MONO_SRC_COPY_BLT              |

| 55h            | XY_FULL_BLT                       |

| 56h            | XY_FULL_MONO_SRC_BLT              |

| 57h            | XY_FULL_MONO_PATTERN_BLT          |

| 58h            | XY_FULL_MONO_PATTERN_MONO_SRC_BLT |

| 59h            | XY_MONO_PAT_FIXED_BLT             |

| Opcode (28:22) | Command                                |

|----------------|----------------------------------------|

| 5Ah-70h        | Reserved                               |

| 71h            | XY_MONO_SRC_COPY_IMMEDIATE_BLT         |

| 72h            | XY_PAT_BLT_IMMEDIATE                   |

| 73h            | XY_SRC_COPY_CHROMA_BLT                 |

| 74h            | XY_FULL_IMMEDIATE_PATTERN_BLT          |

| 75h            | XY_FULL_MONO_SRC_IMMEDIATE_PATTERN_BLT |

| 76h            | XY_PAT_CHROMA_BLT                      |

| 77h            | XY_PAT_CHROMA_BLT_IMMEDIATE            |

| 78h-7Fh        | Reserved                               |

## **3D Commands**

The 3D commands are used to program the graphics pipelines for 3D operations.

Refer to the 3D chapter for a description of the 3D state and primitive commands and the *Media* chapter for a description of the media-related state and object commands.

For all commands listed in **3D Command Map**, the Pipeline Type (bits 28:27) is 3h, indicating the 3D Pipeline.

#### **3D Command Map**

| Opcode<br>Bits 26:24 | Sub Opcode<br>Bits 23:16 | Command                         | Definition Chapter |

|----------------------|--------------------------|---------------------------------|--------------------|

| 0h                   | 01h                      | Reserved                        | 3D Pipeline        |

| 0h                   | 02h                      | Reserved                        | 3D Pipeline        |

| 0h                   | 03h                      | Reserved                        |                    |

| 0h                   | 04h                      | 3DSTATE_CLEAR_PARAMS            | 3D Pipeline        |

| 0h                   | 05h                      | 3DSTATE_DEPTH_BUFFER            | 3D Pipeline        |

| 0h                   | 06h                      | 3DSTATE_STENCIL_BUFFER          | 3D Pipeline        |

| 0h                   | 07h                      | 3DSTATE_HIER_DEPTH_BUFFER       | 3D Pipeline        |

| 0h                   | 08h                      | 3DSTATE_VERTEX_BUFFERS          | Vertex Fetch       |

| 0h                   | 09h                      | 3DSTATE_VERTEX_ELEMENTS         | Vertex Fetch       |

| 0h                   | 0Ah                      | 3DSTATE_INDEX_BUFFER            | Vertex Fetch       |

| 0h                   | 0Bh                      | 3DSTATE_VF_STATISTICS           | Vertex Fetch       |

| 0h                   | 0Ch                      | 3DSTATE_VF                      | Vertex Fetch       |

| 0h                   | 0Dh                      | 3DSTATE_VIEWPORT_STATE_POINTERS | 3D Pipeline        |

| 0h                   | 0Eh                      | 3DSTATE_CC_STATE_POINTERS       | 3D Pipeline        |

| 0h                   | 10h                      | 3DSTATE_VS                      | Vertex Shader      |

| 0h                   | 11h                      | 3DSTATE_GS                      | Geometry Shader    |

| Opcode<br>Bits 26:24 | Sub Opcode<br>Bits 23:16 | Command                                 | Definition Chapter |  |  |  |  |  |

|----------------------|--------------------------|-----------------------------------------|--------------------|--|--|--|--|--|

| 0h                   | 12h                      | 3DSTATE_CLIP                            | Clipper            |  |  |  |  |  |

| 0h                   | 13h                      | 3DSTATE_SF                              | Strips & Fans      |  |  |  |  |  |

| 0h                   | 14h                      | 3DSTATE_WM                              | Windower           |  |  |  |  |  |

| 0h                   | 15h                      | 3DSTATE_CONSTANT_VS                     | Vertex Shader      |  |  |  |  |  |

| 0h                   | 16h                      | 3DSTATE_CONSTANT_GS                     | Geometry Shader    |  |  |  |  |  |

| 0h                   | 17h                      | 3DSTATE_CONSTANT_PS                     | Windower           |  |  |  |  |  |

| 0h                   | 18h                      | 3DSTATE_SAMPLE_MASK                     | Windower           |  |  |  |  |  |

| 0h                   | 19h                      | 3DSTATE_CONSTANT_HS                     | Hull Shader        |  |  |  |  |  |

| 0h                   | 1Ah                      | 3DSTATE_CONSTANT_DS                     | Domain Shader      |  |  |  |  |  |

| 0h                   | 1Bh                      | 3DSTATE_HS                              | Hull Shader        |  |  |  |  |  |

| 0h                   | 1Ch                      | 3DSTATE_TE                              | Tesselator         |  |  |  |  |  |

| 0h                   | 1Dh                      | 3DSTATE_DS                              | Domain Shader      |  |  |  |  |  |

| 0h                   | 1Eh                      | 3DSTATE_STREAMOUT                       | HW Streamout       |  |  |  |  |  |

| 0h                   | 1Fh                      | 3DSTATE_SBE                             | Setup              |  |  |  |  |  |

| 0h                   | 20h                      | 3DSTATE_PS                              | Pixel Shader       |  |  |  |  |  |

| 0h                   | 21h                      | 3DSTATE_VIEWPORT_STATE_POINTERS_SF_CLIP | Strips & Fans      |  |  |  |  |  |

| 0h                   | 23h                      | 3DSTATE_VIEWPORT_STATE_POINTERS_CC      | Windower           |  |  |  |  |  |

| 0h                   | 24h                      | 3DSTATE_BLEND_STATE_POINTERS            | Pixel Shader       |  |  |  |  |  |

| 0h                   | 25h                      | 3DSTATE_DEPTH_STENCIL_STATE_POINTERS    | Pixel Shader       |  |  |  |  |  |

| 0h                   | 26h                      | 3DSTATE_BINDING_TABLE_POINTERS_VS       | Vertex Shader      |  |  |  |  |  |

| 0h                   | 27h                      | 3DSTATE_BINDING_TABLE_POINTERS_HS       | Hull Shader        |  |  |  |  |  |

| 0h                   | 28h                      | 3DSTATE_BINDING_TABLE_POINTERS_DS       | Domain Shader      |  |  |  |  |  |

| 0h                   | 29h                      | 3DSTATE_BINDING_TABLE_POINTERS_GS       | Geometry Shader    |  |  |  |  |  |

| 0h                   | 2Ah                      | 3DSTATE_BINDING_TABLE_POINTERS_PS       | Pixel Shader       |  |  |  |  |  |

| 0h                   | 2Bh                      | 3DSTATE_SAMPLER_STATE_POINTERS_VS       | Vertex Shader      |  |  |  |  |  |

| 0h                   | 2Ch                      | 3DSTATE_SAMPLER_STATE_POINTERS_HS       | Hull Shader        |  |  |  |  |  |

| 0h                   | 2Dh                      | 3DSTATE_SAMPLER_STATE_POINTERS_DS       | Domain Shader      |  |  |  |  |  |

| 0h                   | 2Eh                      | 3DSTATE_SAMPLER_STATE_POINTERS_GS       | Geometry Shader    |  |  |  |  |  |

| 0h                   | 2Fh                      | 3DSTATE_SAMPLER_STATE_POINTERS_PS       | Pixel Shader       |  |  |  |  |  |

| 0h                   | 30h                      | 3DSTATE_URB_VS                          | Vertex Shader      |  |  |  |  |  |

| 0h                   | 31h                      | 3DSTATE_URB_HS                          | Hull Shader        |  |  |  |  |  |

| 0h                   | 32h                      | 3DSTATE_URB_DS                          | Domain Shader      |  |  |  |  |  |

| 0h                   | 33h                      | 3DSTATE_URB_GS                          | Geometry Shader    |  |  |  |  |  |

| 0h                   | 34h                      | 3DSTATE_GATHER_CONSTANT_VS              | Vertex Shader      |  |  |  |  |  |

| 0h                   | 35h                      | 3DSTATE_GATHER_CONSTANT_GS Geometry S   |                    |  |  |  |  |  |

| Opcode<br>Bits 26:24 | Sub Opcode<br>Bits 23:16 | Command                                              | Definition Chapter |  |  |  |  |

|----------------------|--------------------------|------------------------------------------------------|--------------------|--|--|--|--|

| 0h                   | 36h                      | 3DSTATE_GATHER_CONSTANT_HS                           | Hull Shader        |  |  |  |  |

| 0h                   | 37h                      | 3DSTATE_GATHER_CONSTANT_DS                           | Domain Shader      |  |  |  |  |

| 0h                   | 38h                      | 3DSTATE_GATHER_CONSTANT_PS                           | Pixel Shader       |  |  |  |  |

| 0h                   | 39h                      | 3DSTATE_DX9_CONSTANTF_VS                             | Vertex Shader      |  |  |  |  |

| 0h                   | 3Ah                      | 3DSTATE_DX9_CONSTANTF_PS                             | Pixel Shader       |  |  |  |  |

| 0h                   | 3Bh                      | 3DSTATE_DX9_CONSTANTI_VS                             | Vertex Shader      |  |  |  |  |

| 0h                   | 3Ch                      | 3DSTATE_DX9_CONSTANTI_PS                             | Pixel Shader       |  |  |  |  |

| 0h                   | 3Dh                      | 3DSTATE_DX9_CONSTANTB_VS                             | Vertex Shader      |  |  |  |  |

| 0h                   | 3Eh                      | 3DSTATE_DX9_CONSTANTB_PS                             | Pixel Shader       |  |  |  |  |

| 0h                   | 3Fh                      | 3DSTATE_DX9_LOCAL_VALID_VS                           | Vertex Shader      |  |  |  |  |

| 0h                   | 40h                      | 3DSTATE_DX9_LOCAL_VALID_PS                           | Pixel Shader       |  |  |  |  |

| 0h                   | 41h                      | 3DSTATE_DX9_GENERATE_ACTIVE_VS                       | Vertex Shader      |  |  |  |  |

| 0h                   | 42h                      | 3DSTATE_DX9_GENERATE_ACTIVE_PS                       | Pixel Shader       |  |  |  |  |

| 0h                   | 43h                      | 3DSTATE_BINDING_TABLE_EDIT_VS                        | Vertex Shader      |  |  |  |  |

| 0h                   | 44h                      | 3DSTATE_BINDING_TABLE_EDIT_GS                        | Geometry Shader    |  |  |  |  |

| 0h                   | 45h                      | 3DSTATE_BINDING_TABLE_EDIT_HS                        | Hull Shader        |  |  |  |  |

| 0h                   | 46h                      | 3DSTATE_BINDING_TABLE_EDIT_DS                        | Domain Shader      |  |  |  |  |

| 0h                   | 47h                      | 3DSTATE_BINDING_TABLE_EDIT_PS                        | Pixel Shader       |  |  |  |  |

| 0h                   | 48h                      | 3DSTATE_VF_HASHING                                   | Vertex Fetch       |  |  |  |  |

| 0h                   | 49h                      | 3DSTATE_VF_INSTANCING                                | Vertex Fetch       |  |  |  |  |

| 0h                   | 4Ah                      | 3DSTATE_VF_SGVS                                      | Vertex Fetch       |  |  |  |  |

| 0h                   | 4Bh                      | 3DSTATE_VF_TOPOLOGY                                  | Vertex Fetch       |  |  |  |  |

| 0h                   | 4Ch                      | 3DSTATE_WM_CHROMA_KEY                                | Windower           |  |  |  |  |

| 0h                   | 4Dh                      | 3DSTATE_PS_BLEND                                     | Windower           |  |  |  |  |

| 0h                   | 4Eh                      | 3DSTATE_WM_DEPTH_STENCIL                             | Windower           |  |  |  |  |

| 0h                   | 4Fh                      | 3DSTATE_PS_EXTRA                                     | Windower           |  |  |  |  |

| 0h                   | 50h                      | 3DSTATE_RASTER                                       | Strips & Fans      |  |  |  |  |

| 0h                   | 51h                      | 3DSTATE_SBE_SWIZ                                     | Strips & Fans      |  |  |  |  |

| 0h                   | 52h                      | 3DSTATE_WM_HZ_OP                                     | Windower           |  |  |  |  |

| 0h                   | 53h                      | 3DSTATE_INT (internally generated state) 3D Pipeline |                    |  |  |  |  |

| 0h                   | 54h                      | 3DSTATE_RS_CONSTANT_POINTER Resource S               |                    |  |  |  |  |

| 0h                   | 55h                      | 3DSTATE_VF_COMPONENT_PACKING                         | Vertex Fetch       |  |  |  |  |

| 0h                   | 58h                      | Reserved                                             |                    |  |  |  |  |

| 0h                   | 59h                      | Reserved                                             |                    |  |  |  |  |

| 0h                   | 5Ah                      | Reserved                                             |                    |  |  |  |  |

| Opcode<br>Bits 26:24 | Sub Opcode<br>Bits 23:16 | Command                          | <b>Definition Chapter</b> |

|----------------------|--------------------------|----------------------------------|---------------------------|

| 0h                   | 5Bh                      | Reserved                         |                           |

| 0h                   | 5Ch                      | Reserved                         |                           |

| 0h                   | 5Dh-69h                  | Reserved                         |                           |

| 0h                   | 56h                      | Reserved                         |                           |

| 0h                   | 57h-59h                  | Reserved                         |                           |

| 0h                   | 60h-68h                  | Reserved                         |                           |

| 0h                   | 69h                      | Reserved                         |                           |

| 0h                   | 6Ah-6Bh                  | Reserved                         |                           |

| 0h                   | 6Ch                      | Reserved                         |                           |

| 0h                   | 6Dh                      | Reserved                         |                           |

| 0h                   | 6Eh-FFh                  | Reserved                         |                           |

| 1h                   | 00h                      | 3DSTATE_DRAWING_RECTANGLE        | Strips & Fans             |

| 1h                   | 02h                      | 3DSTATE_SAMPLER_PALETTE_LOAD0    | Sampling Engine           |

| 1h                   | 03h                      | Reserved                         |                           |

| 1h                   | 04h                      | 3DSTATE_CHROMA_KEY               | Sampling Engine           |

| 1h                   | 05h                      | Reserved                         |                           |

| 1h                   | 06h                      | 3DSTATE_POLY_STIPPLE_OFFSET      | Windower                  |

| 1h                   | 07h                      | 3DSTATE_POLY_STIPPLE_PATTERN     | Windower                  |

| 1h                   | 08h                      | 3DSTATE_LINE_STIPPLE             | Windower                  |

| 1h                   | 0Ah                      | 3DSTATE_AA_LINE_PARAMS           | Windower                  |

| 1h                   | 0Bh                      | 3DSTATE_GS_SVB_INDEX             | Geometry Shader           |

| 1h                   | 0Ch                      | 3DSTATE_SAMPLER_PALETTE_LOAD1    | Sampling Engine           |

| 1h                   | 0Dh                      | 3DSTATE_MULTISAMPLE              | Windower                  |

| 1h                   | 0Eh                      | 3DSTATE_STENCIL_BUFFER           | Windower                  |

| 1h                   | 0Fh                      | 3DSTATE_HIER_DEPTH_BUFFER        | Windower                  |

| 1h                   | 10h                      | 3DSTATE_CLEAR_PARAMS             | Windower                  |

| 1h                   | 11h                      | 3DSTATE_MONOFILTER_SIZE          | Sampling Engine           |

| 1h                   | 12h                      | 3DSTATE_PUSH_CONSTANT_ALLOC_VS   | Vertex Shader             |

| 1h                   | 13h                      | 3DSTATE_PUSH_CONSTANT_ALLOC_HS   | Hull Shader               |

| 1h                   | 14h                      | 3DSTATE_PUSH_CONSTANT_ALLOC_DS   | Domain Shader             |

| 1h                   | 15h                      | 3DSTATE_PUSH_CONSTANT_ALLOC_GS   | Geometry Shader           |

| 1h                   | 16h                      | 3DSTATE_PUSH_CONSTANT_ALLOC_PS   | Pixel Shader              |

| 1h                   | 17h                      | 3DSTATE_SO_DECL_LIST             | HW Streamout              |

| 1h                   | 18h                      | 3DSTATE_SO_BUFFER                | HW Streamout              |

| 1h                   | 19h                      | 3DSTATE_BINDING_TABLE_POOL_ALLOC | Resource Streamer         |

| Opcode<br>Bits 26:24 | Sub Opcode<br>Bits 23:16 | Command                                | <b>Definition Chapter</b> |

|----------------------|--------------------------|----------------------------------------|---------------------------|

| 1h                   | 1Ah                      | 3DSTATE_GATHER_POOL_ALLOC              | Resource Streamer         |

| 1h                   | 1Bh                      | 3DSTATE_DX9_CONSTANT_BUFFER_POOL_ALLOC | Resource Streamer         |

| 1h                   | 1Ch                      | 3DSTATE_SAMPLE_PATTERN                 | Windower                  |

| 1h                   | 1Dh                      | 3DSTATE_URB_CLEAR                      | 3D Pipeline               |

| 1h                   | 1Eh-FFh                  | Reserved                               |                           |

| 2h                   | 00h                      | PIPE_CONTROL                           | 3D Pipeline               |

| 2h                   | 01h-FFh                  | Reserved                               |                           |

| 3h                   | 00h                      | 3DPRIMITIVE                            | Vertex Fetch              |

| 3h                   | 01h-FFh                  | Reserved                               |                           |

| 4h-7h                | 00h-FFh                  | Reserved                               |                           |

| Pipeline Type (28:27)  | Opcode     | Sub Opcode | Command                | <b>Definition Chapter</b>  |

|------------------------|------------|------------|------------------------|----------------------------|

| Common (pipelined)     | Bits 26:24 | Bits 23:16 |                        |                            |

| 0h                     | 0h         | 03h        | STATE_PREFETCH         | Graphics Processing Engine |

| 0h                     | 0h         | 04h-FFh    | Reserved               |                            |

| Common (non-pipelined) | Bits 26:24 | Bits 23:16 |                        |                            |

| 0h                     | 1h         | 00h        | Reserved               | N/A                        |

| 0h                     | 1h         | 01h        | STATE_BASE_ADDRESS     | Graphics Processing Engine |

| 0h                     | 1h         | 02h        | STATE_SIP              | Graphics Processing Engine |

| 0h                     | 1h         | 03h        | Reserved               | 3D Pipeline                |

| 0h                     | 1h         | 04h        | GPGPU CSR BASE ADDRESS | Graphics Processing Engine |

| 0h                     | 1h         | 05h-1Dh    | Reserved               |                            |

| 0h                     | 1h         | 1Eh        | Reserved               |                            |

| 0h                     | 1h         | 1Fh-20h    | Reserved               |                            |

| 0h                     | 1h         | 21h-24h    | Reserved               |                            |

| 0h                     | 1h         | 25h-FFh    | Reserved               | N/A                        |

| Reserved               | Bits 26:24 | Bits 23:16 |                        |                            |

| 0h                     | 2h-7h      | XX         | Reserved               | N/A                        |

#### **VEBOX Commands**

The VEBOX commands are used to program the Video Enhancement engine attached to the Video Enhancement Command Parser.

#### **VEBOX Command Map**

| Pipeline Type (28:27) | Opcode (26:24) | SubopA (23:21) | SubopB (20:16) | Command              |

|-----------------------|----------------|----------------|----------------|----------------------|

| 2h                    | 4h             | 0h             | 0h             | VEBOX_SURFACE_STATE  |

| 2h                    | 4h             | 0h             | 2h             | VEBOX_STATE          |

| 2h                    | 4h             | 0h             | 3h             | VEBOX_DI_IECP        |

| 2h                    | 4h             | 0h             | 1h             | VEBOX_TILING_CONVERT |

#### **MFX Commands**

The MFX (MFD for decode and MFC for encode) commands are used to program the multi-format codec engine attached to the Video Codec Command Parser. See the *MFD* and *MFC* chapters for a description of these commands.

MFX state commands support direct state model and indirect state model. Recommended usage of indirect state model is provided here (as a software usage guideline).

| Pipeline<br>Type   |         | SubopA  | SubopB  |                                |                                 | Recommended Indirect State |                |  |  |  |  |

|--------------------|---------|---------|---------|--------------------------------|---------------------------------|----------------------------|----------------|--|--|--|--|

| (28:27)            | (26:24) | (23:21) | (20:16) | Command                        | Chapter                         | <b>Pointer Map</b>         | Interruptable? |  |  |  |  |

| MFX Common (State) |         |         |         |                                |                                 |                            |                |  |  |  |  |

| 2h                 | 0h      | 0h      | 0h      | MFX_PIPE_MODE_SELECT MFX IMAGE |                                 |                            |                |  |  |  |  |

| 2h                 | 0h      | 0h      | 1h      | MFX_SURFACE_STATE              | X_SURFACE_STATE MFX IMAGE       |                            |                |  |  |  |  |

| 2h                 | 0h      | 0h      | 2h      | MFX_PIPE_BUF_ADDR_STATE        | X_PIPE_BUF_ADDR_STATE MFX IMAGE |                            |                |  |  |  |  |

| 2h                 | 0h      | 0h      | 3h      | MFX_IND_OBJ_BASE_ADDR_STATE    | N/A                             |                            |                |  |  |  |  |

| 2h                 | 0h      | 0h      | 4h      | MFX_BSP_BUF_BASE_ADDR_STATE    | N/A                             |                            |                |  |  |  |  |

| 2h                 | 0h      | 0h      | 6h      | MFX_ STATE_POINTER             | MFX_STATE_POINTER MFX IMAGE     |                            |                |  |  |  |  |

| 2h                 | 0h      | 0h      | 7-8h    | Reserved                       | N/A                             | N/A                        | N/A            |  |  |  |  |

|                    |         |         |         | MFX Common (Object)            |                                 |                            |                |  |  |  |  |

| 2h                 | 0h      | 1h      | 9h      | MFD_ IT_OBJECT                 | MFX                             | N/A                        | Yes            |  |  |  |  |

| 2h                 | 0h      | 0h      | 4-1Fh   | Reserved                       | N/A                             | N/A                        | N/A            |  |  |  |  |

|                    |         |         |         | AVC Common (State)             |                                 |                            |                |  |  |  |  |

| 2h                 | 1h      | 0h      | 0h      | MFX_AVC_IMG_STATE              | MFX                             | IMAGE                      | N/A            |  |  |  |  |

| 2h                 | 1h      | 0h      | 1h      | MFX_AVC_QM_STATE               | MFX                             | IMAGE                      | N/A            |  |  |  |  |

| 2h                 | 1h      | 0h      | 2h      | MFX_AVC_DIRECTMODE_STATE       | MFX                             | SLICE                      | N/A            |  |  |  |  |

| 2h                 | 1h      | 0h      | 3h      | MFX_AVC_SLICE_STATE            | MFX                             | SLICE                      | N/A            |  |  |  |  |

| Pipeline |         |         |         |                                 |                                     | Recommended        |                |  |  |  |  |  |

|----------|---------|---------|---------|---------------------------------|-------------------------------------|--------------------|----------------|--|--|--|--|--|

| Туре     | Opcode  | SubopA  | SubopB  |                                 |                                     | Indirect State     |                |  |  |  |  |  |

| (28:27)  | (26:24) | (23:21) | (20:16) | Command                         | Chapter                             | <b>Pointer Map</b> | Interruptable? |  |  |  |  |  |

| 2h       | 1h      | 0h      | 4h      | MFX_AVC_REF_IDX_STATE           | MFX                                 | SLICE              | N/A            |  |  |  |  |  |

| 2h       | 1h      | 0h      | 5h      | MFX_AVC_WEIGHTOFFSET_STATE      | FX_AVC_WEIGHTOFFSET_STATE MFX SLICE |                    |                |  |  |  |  |  |

| 2h       | 1h      | 0h      | 6-1Fh   | Reserved                        | eserved N/A N/A                     |                    |                |  |  |  |  |  |

| AVC Dec  |         |         |         |                                 |                                     |                    |                |  |  |  |  |  |

| 2h       | 1h      | 1h      | 0-7h    | Reserved                        | erved N/A N/A                       |                    |                |  |  |  |  |  |

| 2h       | 1h      | 1h      | 8h      | MFD_AVC_BSD_OBJECT              | MFX                                 | N/A                | No             |  |  |  |  |  |

| 2h       | 1h      | 1h      | 9-1Fh   | Reserved                        | N/A                                 | N/A                | N/A            |  |  |  |  |  |

|          |         |         |         | AVC Enc                         |                                     |                    |                |  |  |  |  |  |

| 2h       | 1h      | 2h      | 0-1h    | Reserved                        | N/A                                 | N/A                | N/A            |  |  |  |  |  |

| 2h       | 1h      | 2h      | 2h      | MFC_AVC_FQM_STATE               | MFX                                 | IMAGE              | N/A            |  |  |  |  |  |

| 2h       | 1h      | 2h      | 3-7h    | Reserved                        | N/A                                 | N/A                | N/A            |  |  |  |  |  |

| 2h       | 1h      | 2h      | 8h      | MFC_AVC_PAK_INSERT_OBJECT       | MFX                                 | N/A                | N/A            |  |  |  |  |  |

| 2h       | 1h      | 2h      | 9h      | MFC_AVC_PAK_OBJECT              | FC_AVC_PAK_OBJECT MFX N/A           |                    |                |  |  |  |  |  |

| 2h       | 1h      | 2h      | A-1Fh   | Reserved                        | served N/A N/A                      |                    |                |  |  |  |  |  |

| 2h       | 1h      | 2h      | 0-1Fh   | Reserved                        | N/A                                 |                    |                |  |  |  |  |  |

|          |         |         |         | VC1 Common                      |                                     |                    |                |  |  |  |  |  |

| 2h       | 2h      | 0h      | 0h      | MFX_VC1_PIC_STATE               | MFX                                 | IMAGE              | N/A            |  |  |  |  |  |

| 2h       | 2h      | 0h      | 1h      | MFX_VC1_PRED_PIPE_STATE         | MFX                                 | IMAGE              | N/A            |  |  |  |  |  |

| 2h       | 2h      | 0h      | 2h      | MFX_VC1_DIRECTMODE_STATE        | MFX                                 | SLICE              | N/A            |  |  |  |  |  |

| 2h       | 2h      | 0h      | 2-1Fh   | Reserved                        | N/A                                 | N/A                | N/A            |  |  |  |  |  |

|          |         |         |         | VC1 Dec                         |                                     |                    |                |  |  |  |  |  |

| 2h       | 2h      | 1h      | 0-7h    | Reserved                        | N/A                                 | N/A                | N/A            |  |  |  |  |  |

| 2h       | 2h      | 1h      | 8h      | MFD_VC1_BSD_OBJECT              | MFX                                 | N/A                | Yes            |  |  |  |  |  |

| 2h       | 2h      | 1h      | 9-1Fh   | Reserved                        | N/A                                 | N/A                | N/A            |  |  |  |  |  |

|          |         |         |         | VC1 Enc                         |                                     |                    |                |  |  |  |  |  |

| 2h       | 2h      | 2h      | 0-1Fh   | Reserved                        | N/A                                 | N/A                | N/A            |  |  |  |  |  |

|          |         |         |         | MPEG2 Common                    |                                     |                    |                |  |  |  |  |  |

| 2h       | 3h      | 0h      | 0h      | MFX_MPEG2_PIC_STATE             | MFX                                 | IMAGE              | N/A            |  |  |  |  |  |

| 2h       | 3h      | 0h      | 1h      | MFX_MPEG2_QM_STATE              | N/A                                 |                    |                |  |  |  |  |  |

| 2h       | 3h      | 0h      | 2-1Fh   | Reserved                        | N/A                                 |                    |                |  |  |  |  |  |

|          |         |         |         | MPEG2 Dec                       |                                     |                    |                |  |  |  |  |  |

| 2h       | 3h      | 1h      | 1-7h    | Reserved                        | N/A                                 | N/A                | N/A            |  |  |  |  |  |

| 2h       | 3h      | 1h      | 8h      | MFD_MPEG2_BSD_OBJECT MFX N/A Ye |                                     |                    |                |  |  |  |  |  |

| 2h       | 3h      | 1h      | 9-1Fh   | Reserved N/A N/A                |                                     |                    |                |  |  |  |  |  |

| Pipeline<br>Type<br>(28:27) |             | SubopA<br>(23:21) |       |           | Chapter | Recommended<br>Indirect State<br>Pointer Map | Interruptable? |

|-----------------------------|-------------|-------------------|-------|-----------|---------|----------------------------------------------|----------------|

|                             |             |                   |       | MPEG2 Enc |         |                                              |                |

| 2h                          | 3h          | 2h                | 0-1Fh | Reserved  | N/A     | N/A                                          | N/A            |

|                             |             |                   |       | The Rest  |         |                                              |                |

| 2h                          | 4-5h,<br>7h | Х                 | Х     | Reserved  | N/A     | N/A                                          | N/A            |

## **Scheduling**

## **RINGBUF** — Ring Buffer Registers

See the "Device Programming Environment" chapter for detailed information on these registers.

RING\_BUFFER\_TAIL - Ring Buffer Tail

RING\_BUFFER\_HEAD - Ring Buffer Head

RING\_BUFFER\_START - Ring Buffer Start

RING\_BUFFER\_CTL - Ring Buffer Control

**UHPTR - Pending Head Pointer Register**

## **Command Stream Virtual Memory Control**

Per-Process GTT (PPGTT) is setup for an engine (Render, Blitter, Video and Video Enhancement) by programming corresponding Page Directory Pointer (PDP) registers listed below. Refer "Graphics Translation Tables" in "Memory Overview" for more details on Per-Process page table entries and related translations.

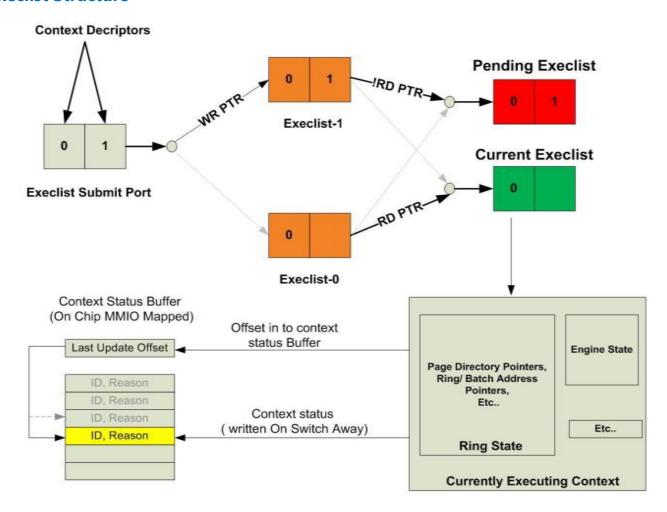

#### **Execlists**

Execlists are the method by which new contexts are submitted for execution. Note that this mechanism cannot be used when the **Execlist Enable** bit in the corresponding engines MODE register is not set, i.e GFX\_MODE register for Render Engine, BLT\_MODE register for Blitter Engine, VCS\_MODE register for Video Engine, or VECS\_MODE register for Video Enhancement Engine. If this bit is not set in the engine's MODE register, writing to the registers in this section is UNDEFINED.

Broadwell implements two execlists. Each execlist can have up to two context descriptors in it, each describing a context to run. SW assembles an execlist by writing each of the context descriptor elements to the Execlist Submit Port register. Writing the final DWord triggers the submission. It is the responsibility of SW to keep track of when an empty execlist entry is available to receive a new execlist submitted via the Submit Port. Submitting a new execlist when there is already a pending execlist (in addition to the current execlist) is UNDEFINED. In general, the interrupt indicating that the pending execlist has become the current execlist should always be observed before a new pending execlist is

submitted. This includes the case where the ring is idle and the very first execlist is submitted; it should not be assumed that this execlist becomes the current list instantaneously.

The submission of a new execlist (known as a preemption request) is interpreted as a request to switch execlists as soon as possible. This is the only trigger for an execlist switch. Within an execlist, a switch from one element (context) to the next can be triggered for several reasons, all of which are synchronous to what the running context itself is doing. Once a context is switched out, the relevant context state and context descriptor doesn't exist in HW, only way the context can be brought back in to HW is by SW resubmitting the context through Execlist Submit Port.

SW must ensure the contexts submitted to both the context descriptors in the execlist are different; i.e SW must not submit the same context descriptor to both the elements of the execlist.

The following are Execlist Registers:

**Execlist Submit Port Register**

**Execlist 1 Contents**

**EXECLIST\_STATUS - Execlist Status Register**

#### **Execlist Structure**

Before submitting a context for the first time, the context image must be properly initialized. Proper initialization includes the ring context registers (ring location, head/tail pointers, etc.) and the page directory.

Render CS Only: Render state need not be initialized; the **Render Context Restore Inhibit** bit in the Context/Save <u>image</u> in memory should be set to prevent restoring garbage render context. See the Logical Ring Context Format section for details.

#### **Context Descriptor Format Structure**

### **Overall Context Layout**

#### **Context Layout**

When Execlists are enabled, the Context Image for the rendering engine consists of 20 4K pages:

Per-Process HW Status Page (4K) Register State Context

When Execlists are disabled, the context image doesn't consist the Per-Process HW status page.

Register State context is explained in detail in "Register State Context" Section.

### **Ring Context**

Ring Context starts at 4K offset from LRCA. Ring context contains all the details that are needed to be initialized by SW for submitting a context to HW for execution (Ring Buffer Details, Page Directory Information ..etc). Ring context is five cachelines in size. Note that the last cacheline of the ring context is specific for a given Engine and hence SW needs to populate it accordingly.

Ring Context comprises of the EXECLIST CONTEXT, EXECLIST CONTEXT (PPGTT Base) of the register state context. In Ring Buffer mode of scheduling EXECLIST CONTEXT contents are save/restored as NOOPS by HW.

EXECLIST CONTEXT

EXECLIST CONTEXT(PPGTT Base)

## **Ring Buffer**

Ring Buffer can exist anywhere in memory mapped via Global GTT. Ring buffer details are mentioned in the ring context area of LRCA (Ring Buffer - Start Address, Head Offset, Tail Pointer & Control Register) in Execution List mode of scheduling. Ring Buffer registers are directly programmed in Ring Buffer mode of scheduling.

#### **Context Descriptor Format**

#### **Context Descriptor Format**

Before submitting a context for the first time, the context image must be properly initialized. Proper initialization includes the ring context registers (ring location, head/tail pointers, etc.) and the page directory.

Render CS Only: Render state need not be initialized; the **Render Context Restore Inhibit** bit in the Context/Save <u>image</u> in memory should be set to prevent restoring garbage render context. See the Logical Ring Context Format section for details.

#### **Programming Note on Context ID field in the Context Descriptor**

This section describes the current usage by SW.

#### Layout:

| 6                     | 6  | 6 | 6 | 5 | 5 | 5  | 5             | 5 | 5 | 5 | 5 | 5 | 5 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 4 | 3 | 3 | 3 | 3 | 3 | 3 | 3 | 3 |

|-----------------------|----|---|---|---|---|----|---------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 3                     | 2  | 1 | 0 | 9 | 8 | 7  | 6             | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 |

| 3                     | 3  | 2 | 2 | 2 | 2 | 2  | 2             | 2 | 2 | 2 | 2 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1                     | 0  | 9 | 8 | 7 | 6 | 5  | 4             | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|                       | HW |   |   |   |   | W  |               |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| Eng. ID SW Counter Us |    |   |   |   |   | se | SW Context ID |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

## **Logical Ring Context Format**

Context descriptor has the graphics virtual address pointing to the logical context in memory. Logical context has all the details required for an engine to execute a context. This is the only means through which software can pass on all the required information to hardware for executing a context. Engine first step on selecting a context for execution is to restore (fetch-context save) the logical context from memory to setup the appropriate state in the hardware. Engine on switching out the context from execution saves (store- context restore) the latest updated state to logical context in memory, the updated state is result of the command buffer execution.

When execution lists are enabled, the Logical Context of each engine (Render, Video, Blitter, Video Enhancement, etc.) primarily consists of the following sections:

- Per-Process HW Status Page (4K)

- Ring Context (Ring Buffer Control Registers, Page Directory Pointers, etc.)

- Engine Context ( PipelineState, Non-pipelineState, Statistics, MMIO)

#### Per-Process of HW status Page (PPHWSP)

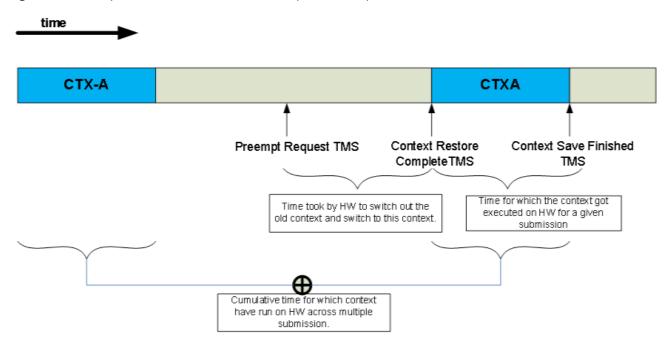

This is a 4KB scratch space memory allocated for each of the context in global address space. First few cachelines are used by the engine for implicit reports like auto-report of head pointer, timestamp statistics associated with a context execution, rest of the space is available for software as scratch space for reporting fences through MI commands. Context descriptor points to the base of Per-Process HW status page. See the PPHWSP format in **PPHWSP\_LAYOUT**.

#### **Logical Ring Context**

Logical Ring Context starts immediately following the PPHWSP in memory. Logical ring context is five cachelines in size. This is the minimal set of hardware state required to be programmed by SW for setting up memory access and the ring buffer for a context to be executed on an engine. Memory setup is required for appropriate address translation in the memory interface. Ring buffer details the location of the ring buffer in global graphics virtual address space with its corresponding head pointer and the tail pointer. Ring context also has "Context Save/Restore Control Register-CTXT\_SR\_CTL" which details the engine context save/restore format. Engine first restores the Logical Ring Context and upon processing CTXT\_SR\_CTL it further decides the due course of Engine Context restore. Logical Ring Context is mostly identical across all engines. Logical ring context is saved to memory with the latest up to date state when a context is switched out.

#### **Engine Context**