# Intel<sup>®</sup> OpenSource HD Graphics Programmer's Reference Manual (PRM) Volume 4 Part 2: Shared Functions – Message Gateway, URB, Video Motion Estimation, Pixel Interpolator (Ivy Bridge)

For the 2012 Intel<sup>®</sup> Core<sup>™</sup> Processor Family

May 2012

**Revision 1.0**

**NOTICE:**

This document contains information on products in the design phase of development, and Intel reserves the right to add or remove product features at any time, with or without changes to this open source documentation.

# **Creative Commons License**

You are free to Share — to copy, distribute, display, and perform the work

#### Under the following conditions:

**Attribution**. You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

No Derivative Works. You may not alter, transform, or build upon this work.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2012, Intel Corporation. All rights reserved.

# Contents

| 1. Sha         | red Functions - Message Gateway                       | 5  |

|----------------|-------------------------------------------------------|----|

| 1.1 Me         | essages                                               | 5  |

| 1.1.1          | Message Descriptor                                    |    |

| 1.1.2          | OpenGateway Message                                   | 7  |

| 1.1.3          | CloseGateway Message                                  |    |

| 1.1.4          | GetTimeStamp Message                                  |    |

| 1.1.5          | BarrierMsg Message                                    |    |

| 1.1.6          | MMIOReadWrite Message                                 | 15 |

|                | red Functions - Unified Return Buffer (URB)           |    |

|                | RB Size                                               |    |

|                | RB Access                                             |    |

|                | ate                                                   |    |

|                | RB Messages                                           |    |

| 2.4.1          | Execution Mask                                        |    |

| 2.4.2          | Message Descriptor                                    |    |

| 2.4.3          | URB_WRITE* and URB_READ*                              |    |

| 2.4.4          |                                                       |    |

|                | red Functions – Video Motion Estimation               |    |

|                | eory of Operation                                     |    |

| 3.1.1          | Shape Decision                                        |    |

| 3.1.2          | Integer Motion Estimation                             |    |

| 3.1.3          | Fractional Motion Estimation                          |    |

| 3.1.4          | BME and Weighted Prediction                           |    |

| 3.1.5          | Skip Check                                            |    |

| 3.1.6<br>3.1.7 | Intra Prediction Estimation<br>Transform Adjusted SAD |    |

| 3.1.7          | Early Decisions                                       |    |

| 3.1.0          | Performance Information                               |    |

|                | VME Changes                                           |    |

|                | Infaces                                               |    |

|                | ate                                                   |    |

| 3.3.1          | BINDING_TABLE_STATE                                   |    |

| 3.3.2          | SURFACE STATE                                         |    |

| 3.3.3          | VME_STATE                                             |    |

|                | hange Details                                         |    |

| 3.4.1          | Record Stream-out and Stream-in                       |    |

| 3.4.2          | MV Definitions and Precision                          |    |

| 3.4.3          | Expanded MV Costs                                     | 58 |

| 3.4.4          | Remove Skip MV Restriction                            | 59 |

| 3.4.5          | Bilinear Interpolation                                |    |

| 3.4.6          | AVC Intra Mode Mask                                   |    |

|                | essages                                               |    |

| 3.5.1          | VME Motion Search Request                             |    |

| 3.5.2          | Message Descriptor                                    |    |

| 3.5.3          | Input Message                                         |    |

| 3.5.4          | Writeback Message                                     |    |

| 3.5.5          | Stream-in/Stream-out Message                          |    |

| 4. Sha         | red Functions Pixel Interpolater                      | 93 |

| 4.1 | Messages              | 93 |

|-----|-----------------------|----|

|     | .1 Initiating Message |    |

|     | .2 Writeback Message  |    |

# 1. Shared Functions - Message Gateway

The Message Gateway shared function provides a mechanism for active thread-to-thread communication. Such thread-to-thread communication is based on direct register access. One thread, a **requester thread**, is capable of writing into the GRF register space of another thread, a **recipient thread**. Such direct register access between two threads in a multi-processor environment some time is referred to as **remote register access**. Remote register access may include read or write. The architecture supports **remote register write**, but not remote register read (natively). Message Gateway facilitates such remote register write via message passing. The requester thread sends a message to Message Gateway requesting a write to the recipient thread's GRF register space. Message Gateway sends a writeback message to the recipient thread to complete the register write on behave of the requester. The requester thread and the recipient thread may be on the same EU or on different EUs.

When Bypass Gateway Control is set to 1, commands OpenGateway and CloseGateway are no longer used, the gateway parameters are taking the default values as the following:

- **RegBase** = 0

- Gateway Size check and Key check are bypassed.

- Gateway Open (an internal signal that is used to be set by OpenGateway message) check is bypassed

A separate Gateway exists per half-slice in the architecture. For ForwardMsg this is handled transparently, but barriers can only be accessed by threads in the local half-slice. This means that all threads that access a shared barrier need to use the half-slice select in GPGPU\_OBJECT and MEDIA\_OBJECT to stay on a single half-slice. GPGPU\_WALKER handles this automatically.

# 1.1 Messages

Message Gateway supports such thread-to-thread communication with the following three messages:

- **OpenGateway:** opens a gateway for a requester thread. Once a thread successfully opens its gateway, it can be a recipient thread to receive remote register write.

- **CloseGateway:** closes the gateway for a requester thread. Once a thread successfully closes its gateway, Message Gateway will block any future remote register writes to this thread.

- ForwardMsg: forwards a formatted message (remote register write) from a requester thread to a recipient thread.

- GetTimeStamp: reads absolute and relative timestamps for a requester thread.

- **BarrierMsg:** A set of threads sends this message to the Gateway. When all threads in a group have sent the message, a reply (both a register write and an N0 notification) is sent to each member of the group.

- UpdateGatewayState: updates the internal state of the Message Gateway.

One example usage is to allow a control thread to change Barrier Byte to convey dynamic state information. This may be used to support interrupt when persistent compute/worker threads are synchronized using Barrier.

• **MMIO Read/Write:** allows a message to read or write an MMIO register. The MEDIA\_VFE\_STATE command has a field which limits the accesses for security.

# 1.1.1 Message Descriptor

The following message descriptor applies to all messages supported by Message Gateway.

| Bit   | Description                                                                                                                                                                                                                                                                                                                                                                           |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 19    | Header Present                                                                                                                                                                                                                                                                                                                                                                        |  |

|       | This bit must be set to <b>zero</b> for all Message Gateway messages.                                                                                                                                                                                                                                                                                                                 |  |

|       | (this bit is not part of the shared function specific message descriptor)                                                                                                                                                                                                                                                                                                             |  |

| 18:17 | <sup>17</sup> Ignored (these bits are not part of the shared function specific message descriptor)                                                                                                                                                                                                                                                                                    |  |

| 16:15 | Notify. Send Notification Signal.                                                                                                                                                                                                                                                                                                                                                     |  |

|       | This is a two-bit field indicating which notify event is sent.                                                                                                                                                                                                                                                                                                                        |  |

|       | 00: No notify                                                                                                                                                                                                                                                                                                                                                                         |  |

|       | 01: Increment recipient thread's N0 notification counter                                                                                                                                                                                                                                                                                                                              |  |

|       | 10: Increment recepient thread's N2 notification counter                                                                                                                                                                                                                                                                                                                              |  |

|       | 11: Reserved                                                                                                                                                                                                                                                                                                                                                                          |  |

|       | This field is only valid for a ForwardMsg message. It is ignored for other messages. The BarrierMsg message always increments the N0 notification counter.                                                                                                                                                                                                                            |  |

| 14    | <b>AckReq.</b> Acknowledgment Required. When this bit is set, an acknowledgment return message is required. Message Gateway will send a writeback message containing the error code to the requester thread using the post destination register address. When this bit is not set, no writeback message is sent to the requesting thread by Message Gateway, even if an error occurs. |  |

|       | This field is valid for OpenGateway, CloseGateway, ForwardMsg and BarrierMsg messages.                                                                                                                                                                                                                                                                                                |  |

|       | When this bit is set, post destination register must be valid and the response length must be 1.                                                                                                                                                                                                                                                                                      |  |

|       | When this bit is not set, post destination register must be <i>null</i> and the response length must be 0.                                                                                                                                                                                                                                                                            |  |

|       | This bit cannot be set when EOT is set; otherwise, hardware behavior is undefined.                                                                                                                                                                                                                                                                                                    |  |

|       | 0 = No Acknowledgement is required.                                                                                                                                                                                                                                                                                                                                                   |  |

|       | 1 = Acknowledgement is required.                                                                                                                                                                                                                                                                                                                                                      |  |

| 13:3  | Reserved: MBZ                                                                                                                                                                                                                                                                                                                                                                         |  |

| 2:0   | SubFuncID. Identify the supported sub-functions by Message Gateway. Encodings are:                                                                                                                                                                                                                                                                                                    |  |

|       | 000 = <b>OpenGateway.</b> Open the gateway for the requester thread.                                                                                                                                                                                                                                                                                                                  |  |

|       | 001 = <b>CloseGateway.</b> Close the gateway for the requester thread.                                                                                                                                                                                                                                                                                                                |  |

|       | 010 = <b>ForwardMsg.</b> Forward the formatted message to the recipient thread with the given offset from the recipient's register base.                                                                                                                                                                                                                                              |  |

|       | 011 = GetTimeStamp. Read absolute and relative timestamps.                                                                                                                                                                                                                                                                                                                            |  |

|       | 100 = <b>BarrierMsg.</b> Record an additional thread reaching the barrier.                                                                                                                                                                                                                                                                                                            |  |

|       | 101 = <b>UpdateGatewayState.</b> Update the barrier byte for a barrier.                                                                                                                                                                                                                                                                                                               |  |

|       | 110 = MMIO Read/Write                                                                                                                                                                                                                                                                                                                                                                 |  |

|       | Others are reserved                                                                                                                                                                                                                                                                                                                                                                   |  |

# 1.1.2 OpenGateway Message

The OpenGateway message opens a communication channel between the requesting thread and other threads. It specifies a key for other threads to access its gateway, as well as the GRF register range allowed to be written. The message consists of a single 256-bit message payload.

If the AckReq bit is set, a single 256-bit payload writeback message is sent back to the requesting thread after completion of the OpenGateway function. Only the least significant DWord in the post destination register is overwritten.

If the EOT is set for this message, Message Gateway will ignore this message; instead, it will close the gateway for the requesting thread regardless of the previous state of the gateway.

It is software's policy to determine how to generate the key.

| DWord                                                                                                                     | Bit   |                                                                                                                                                                                                                                       |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| M0.7                                                                                                                      | 31:0  | Reserved                                                                                                                                                                                                                              |  |  |  |

| M0.6                                                                                                                      | 31:0  | Reserved                                                                                                                                                                                                                              |  |  |  |

| M0.5                                                                                                                      | 31:29 | Reserved: MBZ                                                                                                                                                                                                                         |  |  |  |

|                                                                                                                           | 28:21 | <b>RegBase:</b> The register base address to be stored in the Message Gateway. It is used to compute the destination GRF register address from the offset field in ForwardMsg. RegBase contains 256-bit GRF aligned register address. |  |  |  |

|                                                                                                                           |       | Note 1: This field aligns with bits [28:21] of the Offset field of the message payload for ForwardMsg.                                                                                                                                |  |  |  |

|                                                                                                                           |       | Note 2: the most significant bit of this field must be zero.                                                                                                                                                                          |  |  |  |

|                                                                                                                           |       | Format = U8                                                                                                                                                                                                                           |  |  |  |

|                                                                                                                           |       | Range = [0,127]                                                                                                                                                                                                                       |  |  |  |

|                                                                                                                           | 20:11 | Reserved: MBZ                                                                                                                                                                                                                         |  |  |  |

| 10:8 <b>Gateway Size:</b> The range limit for messages through the Message Gateway. The Gateway Size is 32 GRF registers. |       | Gateway Size: The range limit for messages through the Message Gateway. The maximal allowed Gateway Size is 32 GRF registers.                                                                                                         |  |  |  |

|                                                                                                                           |       | 000: 1 GRF Register                                                                                                                                                                                                                   |  |  |  |

|                                                                                                                           |       | 001: 2 GRF Registers                                                                                                                                                                                                                  |  |  |  |

|                                                                                                                           |       | 010: 4 GRF Registers                                                                                                                                                                                                                  |  |  |  |

|                                                                                                                           |       | 011: 8 GRF Registers                                                                                                                                                                                                                  |  |  |  |

|                                                                                                                           |       | 100: 16 GRF Registers                                                                                                                                                                                                                 |  |  |  |

|                                                                                                                           |       | 101: 32 GRF Registers                                                                                                                                                                                                                 |  |  |  |

|                                                                                                                           | 7:0   | <b>Dispatch ID:</b> This ID is assigned by the fixed function unit and is a unique identifier for the thread. It is used to free up resources used by the thread upon thread completion.                                              |  |  |  |

|                                                                                                                           |       | This field is ignored by Message Gateway                                                                                                                                                                                              |  |  |  |

|                                                                                                                           |       | This field is only required for a thread that is created by a fixed function (therefore, not a child thread) and EOT bit is set for the message.                                                                                      |  |  |  |

## 1.1.2.1 Message Payload

| DWord  | Bit   | Description   |

|--------|-------|---------------|

| M0.4   | 31:16 | Reserved: MBZ |

|        | 15:0  | Reserved: MBZ |

| M0.3:0 |       | Ignored       |

## 1.1.2.2 Writeback Message to Requester Thread

The writeback message is only sent if the **AckReq** bit in the message descriptor is set.

| DWord  | Bit   | Description                                                                         |  |  |

|--------|-------|-------------------------------------------------------------------------------------|--|--|

| W0.7:1 |       | Reserved (not overwritten)                                                          |  |  |

| W0.0   | 31:20 | Reserved                                                                            |  |  |

|        | 19:16 | Shared Function ID: Contains the message gateway's shared function ID.              |  |  |

|        | 15:3  | Reserved                                                                            |  |  |

|        | 2:0   | Error Code                                                                          |  |  |

|        |       | 000: Successful. No Error (Normal)                                                  |  |  |

|        |       | 101: Opcode Error. Attempt to send a message which is not either open/close/forward |  |  |

|        |       | other codes: Reserved                                                               |  |  |

# 1.1.3 CloseGateway Message

The CloseGateway message closes a communication channel for the requesting thread that was previously opened with OpenGateway. Each thread is allowed to have only one open gateway at a time, thus no additional information in the message payload is required to close the gateway. The message consists of a single 256-bit message payload.is

If the AckReq bit is set, a single 256-bit payload writeback message is sent back to the requesting thread after completion of the CloseGateway function. Only the least significant DWord in the post destination register is overwritten.

## 1.1.3.1 Message Payload

| DWord  | Bit  | Description                                                                                                                                                                              |

|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M0.7:6 |      | Ignored                                                                                                                                                                                  |

| M0.5   | 31:8 | Ignored                                                                                                                                                                                  |

| 10.0   | 7:0  | <b>Dispatch ID:</b> This ID is assigned by the fixed function unit and is a unique identifier for the thread. It is used to free up resources used by the thread upon thread completion. |

|        |      | This field is ignored by Message Gateway                                                                                                                                                 |

|        |      | This field is only required for a thread that is created by a fixed function (therefore, not a child thread) and EOT bit is set for the message.                                         |

| M0.4:0 |      | Ignored                                                                                                                                                                                  |

## 1.1.3.2 Writeback Message to Requester Thread

The writeback message is only sent if the **AckReq** bit in the message descriptor is set.

| DWord  | Bit   | Description                                                                         |  |

|--------|-------|-------------------------------------------------------------------------------------|--|

| W0.7:1 |       | Reserved (not overwritten)                                                          |  |

| W0.0   | 31:20 | Reserved                                                                            |  |

|        | 19:16 | Shared Function ID: Contains the message gateway's shared function ID.              |  |

|        | 15:3  | Reserved                                                                            |  |

|        | 2:0   | Error Code                                                                          |  |

|        |       | 000: Successful. No Error (Normal)                                                  |  |

|        |       | 101: Opcode Error. Attempt to send a message which is not either open/close/forward |  |

|        |       | other codes: Reserved                                                               |  |

## 1.1.3.3 ForwardMsg Message

The ForwardMsg message gives the ability for a requester thread to write a **data segment** in the form of a byte, a dword, 2 dwords, or 4 dwords to a GRF register in a recipient thread. The message consists of a single 256-bit message payload, which contains the specially formatted data segment.

The ForwardMsg message utilizes a communication channel previously opened by the recipient thread. The recipient thread has communicated its EUID, TID, and key to the requester thread previously via some other mechanism. Generally, this is done through the thread spawn message from parent to child thread, allowing each child (requester) to then communicate with its parent through a gateway opened by the parent (recipient). The child could then use ForwardMsg message to communicate its own EUID, TID, and key back to the parent to enable bi-directional communication after opening its own gateway.

If the AckReq bit is set, a single 256-bit payload writeback message is sent back to the requester thread after completion of the ForwardMsg function. Only the least significant DWord in the post destination register is overwritten.

If the Notify bit in the message descriptor is set, a 'notification' is sent to the recipient thread in order to increment the recipient thread's notification counter. This allows multiple messages to be sent to the recipient without waking up the recipient thread. The last message, having this bit set, will then wake up the recipient thread.

| DWord  | Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Description |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| M0.7   | 31:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reserved    |  |  |

| M0.6   | 31:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Reserved    |  |  |

| IVI0.5 | 31:29 Reserved: MBZ         28:16         Offset: It provides the destination register position in the recipient thread GRF register space as the offset from the RegBase stored in the recipient thread's gateway entry. The offset is in unit of byte, such that bits [28:21] is the 256-bit aligned register offset and bits [4:0] is the sub-register offset. The sub-register offset must be aligned to the Length field in bits [10:8]. The subfields of Offset are further |             |  |  |

#### 1.1.3.4 Message Payload

| DWord                                                           | Bit                                                                                                                                             | t Description                                                                                                                       |                                                                                 |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|

|                                                                 |                                                                                                                                                 | illustrated as the following.                                                                                                       |                                                                                 |  |

|                                                                 | Offset[28:21]: Register offset from the gateway base (Range [0, 127]: bit 12 MBZ)                                                               |                                                                                                                                     |                                                                                 |  |

|                                                                 |                                                                                                                                                 | Offset[20:18]: DW offset                                                                                                            |                                                                                 |  |

| Offset[17:16]: Byte offset (must be 00 for all DW length cases) |                                                                                                                                                 |                                                                                                                                     |                                                                                 |  |

|                                                                 | <b>Programming restriction:</b> R0 can not be used as destination GRF register for ForwardMsg. N register is also not allowed as destination.   |                                                                                                                                     |                                                                                 |  |

|                                                                 | 15:11                                                                                                                                           | Reserved: MBZ                                                                                                                       |                                                                                 |  |

|                                                                 | 10:8                                                                                                                                            | Length: The length of the data segment.                                                                                             |                                                                                 |  |

|                                                                 |                                                                                                                                                 | 000: 1 byte                                                                                                                         |                                                                                 |  |

|                                                                 |                                                                                                                                                 | 001: 1 word                                                                                                                         |                                                                                 |  |

|                                                                 |                                                                                                                                                 | 010: 1 dword                                                                                                                        |                                                                                 |  |

|                                                                 |                                                                                                                                                 | 011: 2 dwords                                                                                                                       |                                                                                 |  |

|                                                                 |                                                                                                                                                 | 100: 4 dwords                                                                                                                       |                                                                                 |  |

|                                                                 |                                                                                                                                                 |                                                                                                                                     |                                                                                 |  |

|                                                                 |                                                                                                                                                 | 101-111: Reserved                                                                                                                   |                                                                                 |  |

|                                                                 | 7:0                                                                                                                                             | <b>Dispatch ID:</b> This ID is assigned by the fixed function unit and used to free up resources used by the thread upon thread com |                                                                                 |  |

|                                                                 |                                                                                                                                                 | This field is ignored by Message Gateway                                                                                            |                                                                                 |  |

|                                                                 | This field is only required for a thread that is created by a fixed function (therefore, not a child thread and EOT bit is set for the message. |                                                                                                                                     |                                                                                 |  |

| NO 4                                                            | 31:30                                                                                                                                           | Ignored                                                                                                                             |                                                                                 |  |

| M0.4                                                            | 29                                                                                                                                              |                                                                                                                                     |                                                                                 |  |

|                                                                 | 28<br>31:30                                                                                                                                     |                                                                                                                                     |                                                                                 |  |

|                                                                 | 29:28                                                                                                                                           |                                                                                                                                     |                                                                                 |  |

|                                                                 | 27:24                                                                                                                                           | <b>EUID:</b> The Execution Unit ID as part of the Recipient field is us whom the message is forwarded.                              | sed to identify the recipient thread to                                         |  |

|                                                                 |                                                                                                                                                 | Ignored                                                                                                                             |                                                                                 |  |

|                                                                 | 18:16                                                                                                                                           | <b>TID:</b> The Thread ID as part of the Recipient field is used to identify the recipient thread to whom the message is forwarded. |                                                                                 |  |

|                                                                 | 15:0                                                                                                                                            | Кеу                                                                                                                                 |                                                                                 |  |

|                                                                 |                                                                                                                                                 | The key to match with the one stored in the recipient thread's e                                                                    | entry in Message Gateway.                                                       |  |

|                                                                 |                                                                                                                                                 | Ignored                                                                                                                             |                                                                                 |  |

| M0.3                                                            | 31:0                                                                                                                                            | Data Segment DWord 3: valid only for the 4-DWord data segment length                                                                |                                                                                 |  |

| M0.2                                                            | 31:0                                                                                                                                            | Data Segment DWord 2: valid only for the 4-DWord data segment length                                                                |                                                                                 |  |

| M0.1                                                            | 31:0                                                                                                                                            | Data Segment Dword 1: valid only for the 2- and 4-DWord data segment lengths                                                        |                                                                                 |  |

| M0.0                                                            | 31:24                                                                                                                                           | <b>Data Segment Byte 0:</b> the same byte must be copied to all four positions within this DWord. Valid only for the 1-Byte         | <b>Data Segment Dword 0:</b> valid only for the 1-, 2- and 4-Dword data segment |  |

| DWord | Bit   | Description          |         |

|-------|-------|----------------------|---------|

|       |       | data segment length. | lengths |

|       | 23:16 | Data Segment Byte 0  |         |

|       | 15:8  | Data Segment Byte 0  |         |

|       | 7:0   | Data Segment Byte 0  |         |

## 1.1.3.5 Writeback Message to Requester Thread

The writeback message is only sent if the **AckReq** bit in the message descriptor is set.

| DWord  | Bit   | Description                                                                           |  |  |

|--------|-------|---------------------------------------------------------------------------------------|--|--|

| W0.7:1 |       | Reserved (not overwritten)                                                            |  |  |

| W0.0   | 31:20 | Reserved                                                                              |  |  |

|        | 19:16 | Shared Function ID: Contains the message gateway's shared function ID.                |  |  |

|        | 15:3  | Reserved                                                                              |  |  |

|        | 2:0   | Error Code                                                                            |  |  |

|        |       | 000: Successful. No Error (Normal)                                                    |  |  |

|        |       | 001: Reserved                                                                         |  |  |

|        |       | 010: Gateway Closed. Attempt to send a message through a closed gateway               |  |  |

|        |       | 101: Opcode Error. Attempt to send a message which is not either open/close/forward   |  |  |

|        |       | 110: Invalid Message Size. Attempt to forward a message with length greater than 4 DW |  |  |

|        |       | 111: Reserved                                                                         |  |  |

## 1.1.3.6 Writeback Message to Recipient Thread

This message contains the byte or dwords data segment indicated in the message written to the GRF register offset indicated. Only the byte/dword(s) will be enabled, all other data in the GRF register is untouched.

# 1.1.4 GetTimeStamp Message

The GetTimeStamp message gives the ability for a requester thread to read the timestamps back from the message gateway. The message consists of a single 256-bit message payload.

AbsoluteTimeLap is based on an absolute wall clock in unit of nSec/uSec that is independent of context switch or GPU frequency adjustment. Message Gateway shares the same GPU timestamp. Details can be found in the TIMESTAMP register section in *vol1c Memory Interface and Command Stream*.

RelativeTimeLap is based on a relative time count that is counting the GPU clocks for the context. The relative time count is saved/restored during context switch.

## 1.1.4.1 Message Payload

| DWord | Bit  | Description                                                                                                                                                                              |  |  |

|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| M0.7  | 31:0 | Reserved                                                                                                                                                                                 |  |  |

| M0.6  | 31:0 | Reserved                                                                                                                                                                                 |  |  |

| M0.5  | 31   | Return to High GRF:                                                                                                                                                                      |  |  |

|       |      | 0: the return 128-bit data goes to the first half of the destination GRF register                                                                                                        |  |  |

|       |      | 1: the return 128-bit data goes to the second half of the destination GRF register                                                                                                       |  |  |

|       | 30:8 | Reserved : MBZ                                                                                                                                                                           |  |  |

|       | 7:0  | <b>Dispatch ID:</b> This ID is assigned by the fixed function unit and is a unique identifier for the thread. It is used to free up resources used by the thread upon thread completion. |  |  |

|       |      | This field is ignored by Message Gateway                                                                                                                                                 |  |  |

|       |      | This field is only required for a thread that is created by a fixed function (therefore, not a child thread) and EOT bit is set for the message.                                         |  |  |

| M0.4  | 31:0 | Ignored                                                                                                                                                                                  |  |  |

| M0.3  | 31:0 | Ignored                                                                                                                                                                                  |  |  |

| M0.2  | 31:0 | Ignored                                                                                                                                                                                  |  |  |

| M0.1  | 31:0 | Olgnored                                                                                                                                                                                 |  |  |

| M0.0  | 31:0 | Ignored                                                                                                                                                                                  |  |  |

## 1.1.4.2 Writeback Message to Requester Thread

As the writeback message is only sent if the **AckReq** bit in the message descriptor is set, **AckReq** bit must be set for this message.

Only half of the destination GRF register is updated (via write-enables). The other half of the register is not changed. This is determined by the **Return to High GRF** control field.

| DWord  | Bit   | Description                                                                                                                                                                                                                                                             |  |  |  |

|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| W0.7:4 |       | Reserved (not overwritten)                                                                                                                                                                                                                                              |  |  |  |

| W0.3   | 31:0  | RelativeTimeLapHigh: This field returns the MSBs of time lap for the relative clock since the previous reset. This field represents 1.024 uSec increment of the time stamp. Hardware handles the wraparound (over 64 bit boundary) of the timestamp.<br>Format: U12     |  |  |  |

| W0.2   | 31:20 | <b>RelativeTimeLapLow:</b> This field returns the LSBs of time lap for the relative clock since the previous reset. This field represents 1/4 nSec increment of the time stamp. Hardware handles the wraparound (over 64 bit boundary) of the timestamp.<br>Format: U12 |  |  |  |

|        | 19:0  | Reserved : MBZ                                                                                                                                                                                                                                                          |  |  |  |

| W0.1   | 31:0  | AbsoluteTimeLapHigh: This field returns the MSBs of time lap for the absolute clock since the previous reset. This field represents 1.024 uSec increment of the time stamp. Hardware handles the wraparound (over 64 bit boundary) of the timestamp.<br>Format: U12     |  |  |  |

Writeback Message if Return to High GRF is set to 0:

| DWord | Bit   | Description                                                                                                                                                                                                                                                             |  |  |  |

|-------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| W0.0  | 31:20 | <b>AbsoluteTimeLapLow:</b> This field returns the LSBs of time lap for the absolute clock since the previous reset. This field represents 1/4 nSec increment of the time stamp. Hardware handles the wraparound (over 64 bit boundary) of the timestamp.<br>Format: U12 |  |  |  |

|       | 19:0  | Reserved : MBZ                                                                                                                                                                                                                                                          |  |  |  |

Writeback Message if Return to High GRF is set to 1:

| DWord  | Bit   | Description         |  |  |  |

|--------|-------|---------------------|--|--|--|

| W0.7   | 31:0  | RelativeTimeLapHigh |  |  |  |

| W0.6   | 31:20 | RelativeTimeLapLow  |  |  |  |

|        | 19:0  | Reserved : MBZ      |  |  |  |

| W0.5   | 31:0  | AbsoluteTimeLapHigh |  |  |  |

| W0.4   | 31:20 | AbsoluteTimeLapLow  |  |  |  |

|        | 19:0  | Reserved : MBZ      |  |  |  |

| W0.3:0 |       | Reserved : MBZ      |  |  |  |

# 1.1.5 BarrierMsg Message

The BarrierMsg message gives the ability for multiple threads to synchronize their progress. This is useful when there are data shared between threads. The message consists of a single 256-bit message payload.

Upon receiving one such message, Message Gateway increments the Barrier counter and mark the Barrier requester thread. There is no immediate response from the Message Gateway. When the counter value equates **Barrier Thread Count**, Message Gateway will send response back to all the Barrier requesters.

## 1.1.5.1 Message Payload

| DWord | Bit                                                       | Description                                                                                                                                                                                                                                                                             |  |  |  |  |

|-------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| M0.7  | 31:0                                                      | served                                                                                                                                                                                                                                                                                  |  |  |  |  |

| M0.6  | 31:0                                                      | eserved                                                                                                                                                                                                                                                                                 |  |  |  |  |

| M0.5  | 31:0                                                      | Ignored                                                                                                                                                                                                                                                                                 |  |  |  |  |

| M0.4  | 31:0                                                      | Ignored                                                                                                                                                                                                                                                                                 |  |  |  |  |

| M0.3  | 31:0                                                      | Ignored                                                                                                                                                                                                                                                                                 |  |  |  |  |

| M0.2  | 31:28                                                     | gnored BarrierID. This field indicates which one from the 16 Barrier States is updated.                                                                                                                                                                                                 |  |  |  |  |

| 10.2  | 27:24                                                     |                                                                                                                                                                                                                                                                                         |  |  |  |  |

|       |                                                           | Format: U4                                                                                                                                                                                                                                                                              |  |  |  |  |

|       | Note: this field location matches with that of R0 header. |                                                                                                                                                                                                                                                                                         |  |  |  |  |

|       | 23:16                                                     | <b>Barrier.Offset.</b> This is the offset for the Barrier to indicate the offset from the requester's RegBase.<br>Regbase is 0 if Bypass Gateway Control is 1. Barrier.Offset + RegBase must be in the valid GRF range, but not point to r0. Otherwise, hardware behavior is undefined. |  |  |  |  |

| DWord | Bit  | Description                                          |  |  |

|-------|------|------------------------------------------------------|--|--|

|       |      | It is in unit of 256-bit GRF register.               |  |  |

|       |      | The most significant bit of this field must be zero. |  |  |

|       |      | Format = U8                                          |  |  |

|       |      | Range = [0,127]                                      |  |  |

|       | 15:0 | Ignored                                              |  |  |

| M0.1  | 31:0 | Ignored                                              |  |  |

| M0.0  | 31:4 | Ignored                                              |  |  |

# 1.1.5.2 Message Payload

| DWord | Bit   | Description                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| M0.7  | 31:0  | Ignored                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| M0.6  | 31:0  | Ignored                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| M0.5  | 31:0  | gnored                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| M0.4  |       | Ignored                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| M0.3  | 31:0  | Ignored                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| M0.2  | 31    | Ignored                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|       | 30:28 | Ignored                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|       | 27:24 | <b>BarrierID</b> . This field indicates which one from the 16 Barrier States is updated.<br>Format: U4                                                                                                                                                                                                                                                                                                                                |  |  |  |

|       |       | Note: this field location matches with that of R0 header.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|       | 23:16 | gnored                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|       | 15    | Barrier Count Enable: Allows the message to reprogram the barrier count.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|       |       | If set, the current value of the barrier state is compared to the Barrier Count field (below). If these values are equal, the barrier is considered satisfied, barrier responses are sent to the waiting thread(s) including the sending thread, and the barrier state is reset to 0. If these values are not equal, the barrier state is incremented and the sending thread is added to the list of threads waiting on this barrier. |  |  |  |

|       |       | If clear, the Message Gateway increments the Barrier counter and marks the Barrier requester thread. There is no immediate response from the Gateway. When the counter value equates Barrier Thread Count, Gateway will send response back to all the Barrier requesters.                                                                                                                                                             |  |  |  |

|       |       | Format: Enable                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

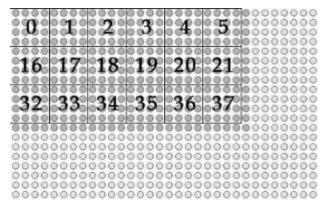

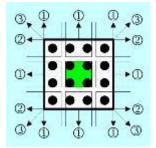

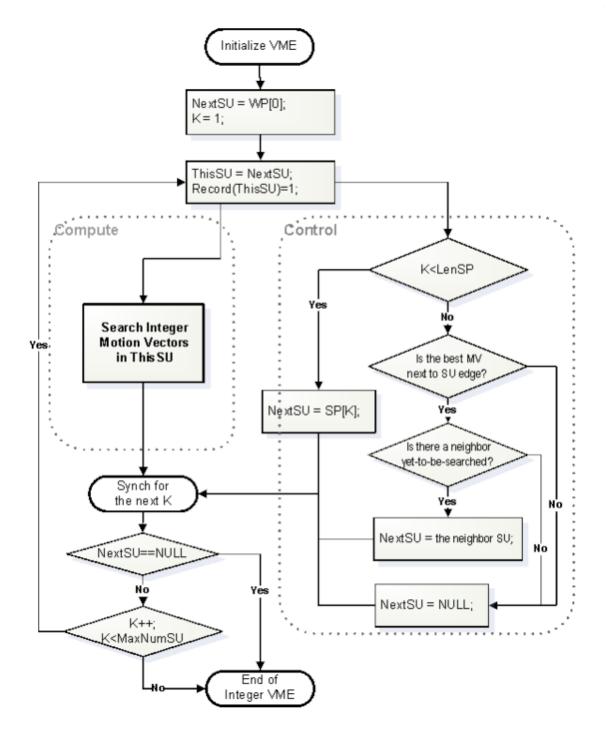

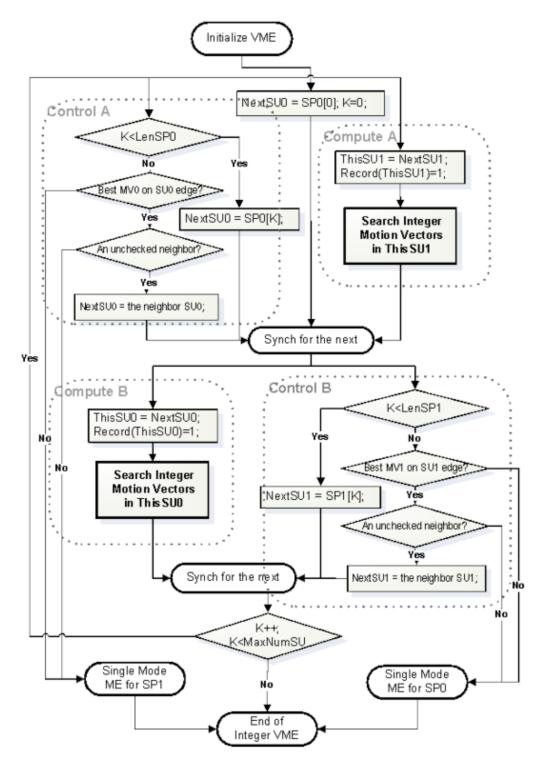

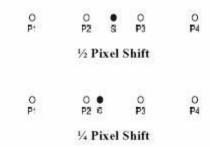

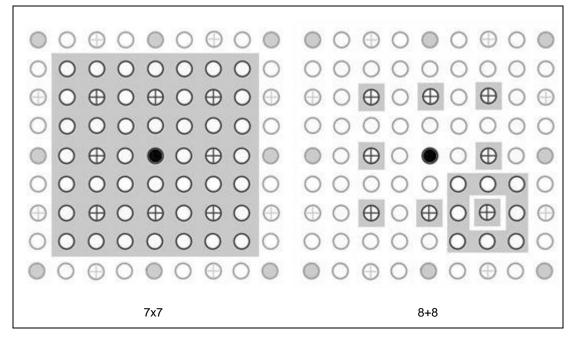

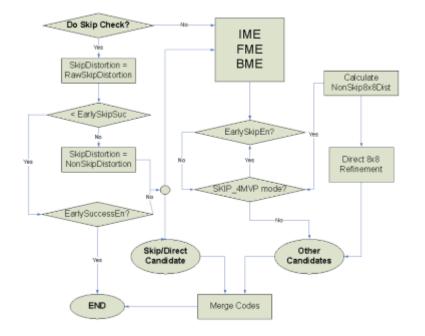

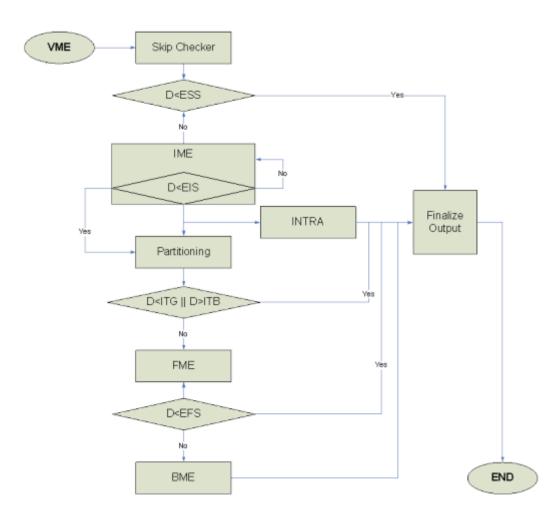

|       | 14:9  | Barrier Count:                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |