# Intel® OpenSource HD Graphics PRM

**Volume 3 Part 3: PCH Display Registers [DevIBX]**

For the all new 2010 Intel Core Processor Family Programmer's Reference Manual (PRM)

March 2010

Revision 1.0

#### **Creative Commons License**

#### You are free:

to Share — to copy, distribute, display, and perform the work

#### Under the following conditions:

**Attribution**. You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

No Derivative Works. You may not alter, transform, or build upon this work.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Sandy Bridge chipset family, Havendale/Auburndale chipset family, Intel® 965 Express Chipset Family, Intel® G35 Express Chipset, and Intel® 965GMx Chipset Mobile Family Graphics Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel and the Intel are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2010, Intel Corporation. All rights reserved.

Doc Ref #: IHD OS V3Pt3 3 10

# **Revision History**

| Document Number   | Rev-<br>Number | Description Re  | vision Date |

|-------------------|----------------|-----------------|-------------|

| IHD_OS_V3Pt3_3_10 | 1.0            | Initial release | March 2010  |

**§§**

| 1. PCH Display Registers [DevIBX]                                           | 6   |

|-----------------------------------------------------------------------------|-----|

| 1.1 Introduction and Register Summary                                       |     |

| 1.1.1 Display Diagram                                                       |     |

| 1.1.2 Terminology                                                           |     |

| 1.1.3 Display Mode Set Sequence                                             | 8   |

| 1.1.4 Simultaneous Display Capabilities on a Single Display Pipe/Transcoder | g   |

|                                                                             |     |

| 2. South Shared Functions (C0000h-CFFFh)                                    | 10  |

| 2.1 Interrupt Control Registers                                             |     |

| 2.1.1 South Display Engine Interrupt Registers Bit Definition               |     |

| 2.2 GMBUS and I/O Control Registers (C5000h–C5FFFh)                         |     |

| 2.2.1 GPIO Pin Usage (By Functions)                                         |     |

| 2.2.2 GPIO Pin Usage (By Device)                                            |     |

|                                                                             |     |

| 2.3 Display Clock Control Registers (C6000h–C6FFFH)                         |     |

| 2.4 Panel Power Sequencing Registers                                        |     |

| 2.5 Backlight Control Registers                                             |     |

| 3. South Transcoder and Port Controls (E0000h–EFFFFh)                       | 63  |

| 3.1 Transcoder A Timing                                                     | 63  |

| 3.2 Transcoder A M/N Values                                                 | 70  |

| 3.3 Transcoder A Video DIP                                                  | 75  |

| 3.4 Transcoder B Timing                                                     | 82  |

| 3.5 Transcoder B M/N Values                                                 | 86  |

| 3.6 Transcoder B Video DIP                                                  |     |

| 3.7 CRT DAC                                                                 |     |

| 3.8 HDMI port C                                                             |     |

| 3.9 HDMI port D                                                             |     |

| 3.9.1 HDMID—Digital Display Port D Register                                 |     |

| 3.10 LVDS                                                                   | 105 |

| 4. South FDI Rx and Transcoder Control (F0000h-FBFFFh)                      | 111 |

| 4.1.1 Display Transcoder A Control                                          |     |

| 4.1.2 Display Transcoder B Control                                          |     |

| 4.1.3 FDI A Receiver Control                                                |     |

| 4.1.4 FDI B Receiver Control                                                |     |

| 4.2 HD Audio Registers (E2000h–E2FFFh)                                      |     |

| 4.2.1 Audio Configuration                                                   |     |

| 4.2.2 AUD_CONFIG_A—Audio Configuration – Transcoder A                       |     |

| 4.2.3 AUD_CONFIG_B—Audio Configuration – Transcoder B                       |     |

| 4.2.4 AUD_MISC_CTRL_A—Audio MISC Control for Transcoder A                   |     |

| 4.2.5 AUD_MISC_CTRL_B—Audio MISC Control for Transcoder B                   |     |

| 4.2.6 AUD_VID_DID—Audio Vendor ID / Device ID                               | 135 |

| 4.2.7 AUD_RID—Audio Revision ID                                             |     |

| 4.2.8 AUD_PWRST—Audio Power State (Function Group, Convertor, Pin Widget)   | 137 |

| 4.2.9 AUD_PORT_EN_HD_CFG — Audio Port Enable HDAudio Config                 |     |

| 4.2.10 AUD_OUT_DIG_CNVT_A—Audio Digital Converter – Conv A                  | 141 |

| 4.2.11 AUD_OUT_DIG_CNVT_B—Audio Digital Converter – Conv                    | 143 |

| 4.2.12 AUD_OUT_CH_STR—Audio Channel ID and Stream ID                        |     |

| 4.2.13 AUD OUT STR DESC A—Audio Stream Descriptor Format – Cony A           | 146 |

5

| 4.6 | DP_BUFTRANS—DisplayPort Buffer Translation        |          |     |

|-----|---------------------------------------------------|----------|-----|

|     | 5.3 DPD_AUX_CH_DATA—Display Port D AUX Data Ro    | egisters | 186 |

| 4.  | 5.2 DPD_AUX_CH_CTL—Display Port D AUX Channel     |          |     |

|     | 5.1 DPD—DisplayPort D Control Register            |          |     |

| 4.5 | DPD Control and Aux Channel                       |          |     |

|     | 4.3 DPC_AUX_CH_DATA—Display Port C AUX Data Ro    |          |     |

|     | 4.2 DPC_AUX_CH_CTL—Display Port C AUX Channel     |          |     |

|     | 4.1 DPC—Display Port C Control Register           |          |     |

|     | DPC Control and Aux Channel                       |          |     |

|     | 3.3 DPB_AUX_CH_DATA—Display Port B AUX Data Re    |          |     |

|     | 3.2 DPB_AUX_CH_CTL—Display Port B AUX Channel     |          |     |

|     | 3.1 DPB—DisplayPort B Control Register            |          |     |

|     | DPB Control and Aux Channel                       |          |     |

|     | 2.22                                              |          |     |

|     | 2.21                                              |          |     |

|     | 2.20                                              |          |     |

|     | 2.19 AUD_HDMIW_STATUS—Audio HDMI Status           |          |     |

|     | 2.18 AUD_CNTL_ST2— Audio Control State 2          |          |     |

|     | 2.17 AUD_CNTL_ST_B—Audio Control State Register - |          |     |

|     | 2.16 AUD_CNTL_ST_A—Audio Control State Register - |          |     |

|     | 2.15 AUD_PINW_CONNLNG_SEL—Audio Connection S      |          |     |

| • • | 2.14 AUD_OUT_STR_DESC_B—Audio Stream Descrip      |          |     |

6

## 1. PCH Display Registers [DevIBX]

## 1.1 Introduction and Register Summary

This chapter contains the register descriptions for the display portion of a family of integrated graphics devices. These registers do vary by devices within the family of devices so special attention needs to be paid to which devices use which registers and register fields.

Different devices within the family may add, modify, or delete registers or register fields relative to another device in the same family based on the supported functions of that device. Additional information on the use and programming of these registers can be found in the display chapter.

The following table contains the sections break down where the register information is contained within this chapter:

| Address Range | Description                    |

|---------------|--------------------------------|

| C0000h-CFFFFh | Shared Functions               |

| D0000h-DFFFFh | Messages                       |

| E0000h-EFFFFh | Transcoder and Port Controls   |

| F0000h-FBFFFh | Transcoder and FDI Rx Controls |

| FC000h-FFFFFh | AFE Registers                  |

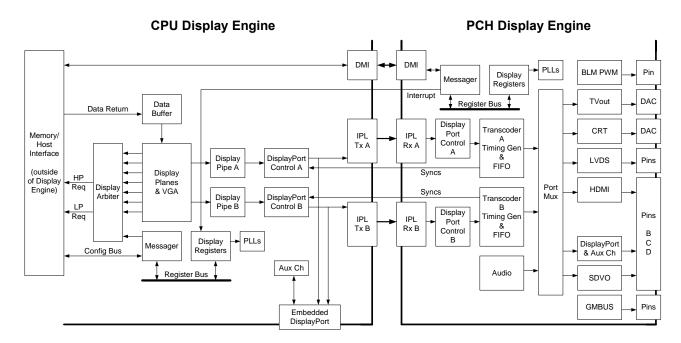

## 1.1.1 Display Diagram

The display engine plane and pipe functions are in the CPU and most of the port functions are in the PCH.

FDI transfers pixel data from the CPU Display Engine (Tx - transmit side) to the PCH Display Engine (Rx - receive side). Sync signals control the pixel flow over FDI.

A pipe in the CPU Display Engine connects to a transcoder in the PCH Display Engine through the FDI interface.

The CPU Display Engine is also called the "North Display".

The PCH Display Engine is also called the "South Display".

## 1.1.2 Terminol ogy

| Description                                   | Software Use                                                                                                                                                                                                                                                                                                                                       | Should be implemented as                                                                                                                                                                                                                                                                    |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read/Write                                    | This bit can be read or written.                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                             |

| Reserved:                                     | Don't assume a value for these bits. Writes have no effect.                                                                                                                                                                                                                                                                                        | Writes are ignored. Reads return zero.                                                                                                                                                                                                                                                      |

| Reserved: write as zero, must be zero, or MBZ | Software must always write a zero to these bits. This allows new features to be added using these bits that will be disabled when using old software and as the default case.                                                                                                                                                                      | Writes are ignored. Reads return zero. Maybe be connected as Read/Write in future projects.                                                                                                                                                                                                 |

| Reserved: software must preserve contents     | Software must write the original value back to this bit. This allows new features to be added using these bits.                                                                                                                                                                                                                                    | Read only Read/Write.                                                                                                                                                                                                                                                                       |

| Read Only                                     | This bit is read only. The read value is determined by hardware. Writes to this bit have no effect.                                                                                                                                                                                                                                                | According to each specific bit. The bit value is determined by hardware and not affected by register writes to the actual bit.                                                                                                                                                              |

| Read/Clear                                    | This bit can be read and writes to it with a one cause the bit to clear.                                                                                                                                                                                                                                                                           | Hardware events cause the bit to be set and the bit will be cleared on a write operation where the corresponding bit has a one for a value.                                                                                                                                                 |

| Double Buffered                               | Write when desired. Read gives the unbuffered value (written value) unless specified otherwise. Written values will update to take effect after a certain point.  Some have a specific arming sequence where a write to another register is required before the update can take place. This is used to ensure atomic updates of several registers. | Two stages of registers used. First stage is written into and used for readback (unless specified otherwise). First stage value is transferred into second stage at the update point. Second stage value is used to control hardware. Arm/disarm flag needed for specific arming sequences. |

## 1.1.3 Display Mode Set Sequence

See the CPU Display Registers Bspec.

# 1.1.4 Simultaneous Display Capabilities on a Single Display Pipe/Transcoder

| Embe                 | dded<br>DP (on<br>CPU) | Inte-<br>grated<br>LVDS | DP CRT      |           |

|----------------------|------------------------|-------------------------|-------------|-----------|

| Embedded<br>DP (CPU) |                        | No (6)                  | No (6)      | No (6)    |

| Integrated LVDS      |                        |                         | No (2, 7)   | No (3, 7) |

| DP                   |                        |                         | No(3, 5, 7) | No (4, 7) |

| CRT                  |                        |                         |             |           |

Shading: Rose = Does not work, Yellow = Some cases work, Green = works

- 2) No internal LVDS, HDMI. DP optionally has SSC.

- 6) Digital ports are multiplexed on the same pins, only works if ports are different.

- 7) Embedded DP is on the CPU; can not share the link.

- 8) Dithering, range correction, and gamma are done in the CPU; the display with lower bpp can truncate or the display with higher bpp can lose bits. One of the displays dictates range and gamma.

- 9) No DisplayPort allowed with other port on the same pipe/transcoder.

- 10) No HDMI allowed with another HDMI on the same transcoder.

# 2. South Shared Functions (C0000h-CFFFFh)

## 2.1 Interrupt Control Registers

## 2.1.1 South Display Engine Interrupt Registers Bit Definition

| South D                           | isplay Er                     | ngine Int                 | errupt Cont                                                | rol Reg                   | isters                  | Bit Defi                  | nition                                  |                   |                                            |

|-----------------------------------|-------------------------------|---------------------------|------------------------------------------------------------|---------------------------|-------------------------|---------------------------|-----------------------------------------|-------------------|--------------------------------------------|

| Project:                          | All                           |                           | Project:                                                   | All                       |                         |                           |                                         |                   |                                            |

| South Disp together to Registers. | lay Engine (s<br>generate the | SDE) interrue<br>South/PC | upt bits come fro<br>H Display Interru                     | m events v<br>ipt Event w | vithin the<br>hich will | south disp<br>appear in t | lay engine<br>he Display                | e. The<br>/ Engin | SDEIIR is ORed<br>e Interrupt Control      |

| hit to be se                      | t šo all PCH                  | l Display Int             | splay interrupt w<br>errupts, includin<br>use the DEIIR to | a back to h               | e North [<br>ack inter  | Display IIR<br>rupts, mus | (DEIIR) Potential (DEIIR) to be cleared | CH Dised in th    | splay Interrupt event<br>e SDEIIR before a |

| The South                         | Display Engi                  | ine Interrup              | t Control Registe                                          | ers all shar              | e the sam               | ne bit defin              | itions from                             | this ta           | ıble.                                      |

| Bit Des                           | on cripti                     | Bit                       | Description                                                |                           |                         |                           |                                         |                   |                                            |

| 31:28                             | Reserved                      | l                         |                                                            |                           |                         |                           | Project:                                | All               | Format:                                    |

| 27                                | audio_Po                      | wer_State                 | _change_Port_l                                             | D                         |                         |                           | Project:                                | All               | Format:                                    |

|                                   | This is an                    | active high               | pulse when ther                                            | e is a pow                | er state c              | hange for                 | audio for p                             | ort D.            |                                            |

| 26                                | audio_Po                      | wer_State                 | _change_Port_0                                             | С                         |                         |                           | Project:                                | All               | Format:                                    |

|                                   | This is an                    | active high               | pulse when ther                                            | e is a pow                | er state c              | hange for                 | audio for p                             | ort C.            |                                            |

| 25                                | audio_Po                      | wer_State                 | _change_Port_l                                             | В                         |                         |                           | Project:                                | All               | Format:                                    |

|                                   | This is an                    | active high               | pulse when ther                                            | e is a pow                | er state c              | hange for                 | audio for p                             | ort B.            |                                            |

| 24                                | Gmbus                         |                           |                                                            |                           |                         |                           | Project:                                | All               | Format:                                    |

|                                   | This is an register or        | •                         | pulse when any                                             | of the eve                | nts unma                | sked even                 | ts in GMB                               | US4 In            | terrupt Mask                               |

| 23                                | Reserved                      |                           |                                                            |                           | _                       |                           | Project:                                | All               | Format:                                    |

| 22                                | Reserved                      | I                         |                                                            |                           |                         |                           |                                         |                   |                                            |

| 21                                | audio_Tra                     | anscoder_l                | В                                                          |                           |                         |                           | Project:                                | All               | Format:                                    |

|                                   | This is an                    | active high               | level caused wh                                            | en audio p                | rotection               | is turned of              | on for trans                            | scoder            | B.                                         |

|                                   |                               |                           |                                                            | •                         |                         |                           |                                         |                   |                                            |

| This is an active high level caused when audio protection is  Poison | turned on for trans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Poison                                                               | tarriod orr for traine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | scoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                      | Project:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Format:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| This is an active high pulse on receiving the poison messag          | je.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Reserved                                                             | Project:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Format:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FDI_RXB(combined)                                                    | Project:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Format:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| This is an active high level while any of the FDI_RXB_IIR bi         | ts are set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FDI_RXA(combined)                                                    | Project:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | All                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Format:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |