# Intel® Iris® Plus Graphics and UHD Graphics Open Source

# **Programmer's Reference Manual**

For the 2019 10th Generation Intel Core™ Processors based on the "Ice Lake" Platform

Volume 5: Memory Data Formats

January 2020, Revision 1.0

#### **Creative Commons License**

**You are free to Share** - to copy, distribute, display, and perform the work under the following conditions:

- **Attribution.** You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

- No Derivative Works. You may not alter, transform, or build upon this work.

#### **Notices and Disclaimers**

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\* Other names and brands may be claimed as the property of others.

**Copyright © 2020, Intel Corporation. All rights reserved.**

# **Table of Contents**

| Memory Data Formats             |    |

|---------------------------------|----|

| Unsigned Normalized (UNORM)     | 1  |

| Gamma Conversion (SRGB)         | 1  |

| Signed Normalized (SNORM)       | 1  |

| Unsigned Integer (UINT/USCALED) | 1  |

| Signed Integer (SINT/SSCALED)   | 2  |

| Floating Point (FLOAT)          | 2  |

| 64-bit Floating Point           | 2  |

| 32-bit Floating Point           | 2  |

| 16-bit Floating Point           | 3  |

| 11-bit Floating Point           | 4  |

| 10-bit Floating Point           | 4  |

| Shared Exponent                 | 5  |

| Common Surface Formats          | 5  |

| Non-Video Surface Formats       | 5  |

| Surface Format Naming           | 5  |

| Intensity Formats               | 6  |

| Luminance Formats               | 6  |

| R1_UNORM                        | 6  |

| Palette Formats                 | 6  |

| P4A4_UNORM                      | 7  |

| A4P4_UNORM                      | 7  |

| P8A8_UNORM                      | 8  |

| A8P8_UNORM                      | 8  |

| P8_UNORM                        | 9  |

| P2_UNORM                        | 9  |

| Compressed Surface Formats      | 9  |

| ETC1_RGB8                       | 9  |

| ETC2_RGB8 and ETC2_SRGB8        | 12 |

| T mode                          | 12 |

| H mode                          |    |

| Planar mode                                              | 17 |

|----------------------------------------------------------|----|

| EAC_R11 and EAC_SIGNED_R11                               | 18 |

| ETC2_RGB8_PTA and ETC2_SRGB8_PTA                         | 19 |

| Differential Mode                                        | 20 |

| T and H Modes                                            | 20 |

| Planar Mode                                              | 20 |

| ETC2_EAC_RGBA8 and ETC2_EAC_SRGB8_A8                     | 20 |

| EAC_RG11 and EAC_SIGNED_RG11                             | 21 |

| DXT/BC1-3 Texture Formats                                | 22 |

| Opaque and One-bit Alpha Textures (DXT1/BC1)             | 23 |

| Opaque Textures (DXT1_RGB)                               | 25 |

| Compressed Textures with Alpha Channels (DXT2-5 / BC2-3) | 26 |

| BC4                                                      | 28 |

| BC5                                                      | 29 |

| BC6H                                                     | 30 |

| Field Definition                                         | 31 |

| Endpoint Computation                                     | 43 |

| Palette Color Computation                                | 43 |

| Texel Selection                                          | 44 |

| ONE Mode                                                 | 44 |

| TWO Mode                                                 | 44 |

| BC7                                                      | 46 |

| Field Definition                                         | 46 |

| Endpoint Computation                                     | 52 |

| Palette Color Computation                                | 52 |

| Texel Selection                                          | 53 |

| ONE Mode                                                 | 53 |

| TWO Mode                                                 | 53 |

| THREE Mode                                               | 55 |

| Adaptive Scalable Texture Compression (ASTC)             | 57 |

| ASTC Fundamentals                                        | 57 |

| Background                                               | 57 |

| New Surface Formats for ASTC Texture                     | 50 |

| ASTC File Format and Memory Layout                 | 64  |

|----------------------------------------------------|-----|

| ASTC Header Data Structure and Amendment           | 64  |

| Data Layout in ASTC Compression File               | 65  |

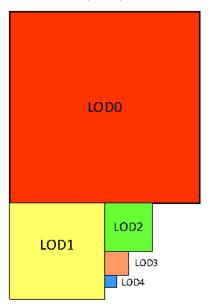

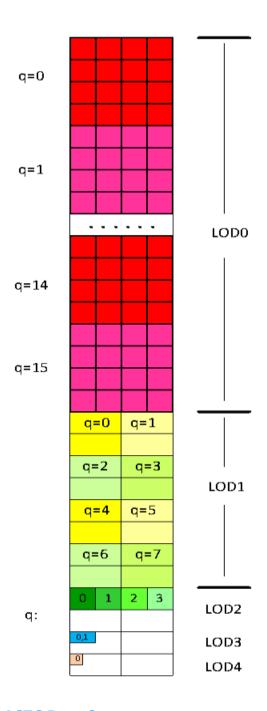

| Total ASTC Data Block Layout in All Mipmap Levels  | 66  |

| Data Layout in Memory for All Mipmap Levels        | 67  |

| ASTC Data Structure                                | 69  |

| Layout and Description of Block Data               | 69  |

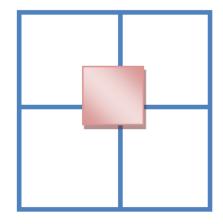

| Partitioning                                       | 70  |

| Index Mode                                         | 70  |

| Index Planes                                       | 74  |

| Index Infill Procedure                             | 74  |

| Color Endpoint Mode                                | 75  |

| Color Endpoint Data Size Determination             | 77  |

| Void-Extent Blocks                                 | 78  |

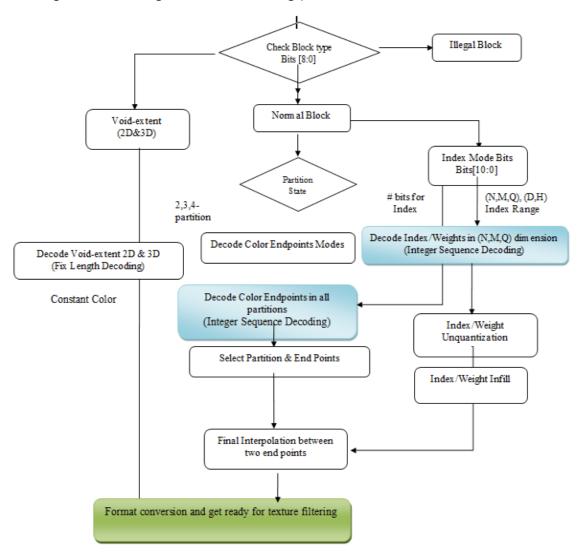

| Decoding Process                                   | 79  |

| Overview Decoding Flow                             | 79  |

| Integer Sequence Encoding                          | 81  |

| Endpoint Unquantization                            | 83  |

| LDR Endpoint Decoding                              | 84  |

| HDR Endpoint Decoding                              | 87  |

| HDR Endpoint Mode 2 (HDR Luminance, Large Range)   | 87  |

| HDR Endpoint Mode 3 (HDR Luminance, Small Range)   | 88  |

| HDR Endpoint Mode 7 (HDR RGB, Base+Scale)          | 88  |

| HDR Endpoint Mode 11 (HDR RGB, Direct)             | 91  |

| HDR Endpoint Mode 14 (HDR RGB, Direct + LDR Alpha) | 94  |

| HDR Endpoint Mode 15 (HDR RGB, Direct + HDR Alpha) | 95  |

| Restrictions on Number of Partitions Per Block     | 96  |

| Index Decoding                                     | 96  |

| Index Unquantization                               | 96  |

| Infill Process                                     | 98  |

| Index Application                                  | 99  |

| Dual-Plane Decoding                                | 100 |

| Partition Pattern Generation                       | 101 |

| Data Size Determination                | 103 |

|----------------------------------------|-----|

| 3D Void-Extent Blocks                  | 104 |

| Illegal Encodings                      | 104 |

| Profile Support                        | 105 |

| Video Pixel/Texel Formats              | 106 |

| Packed Memory Organization             | 106 |

| Planar Memory Organization             | 106 |

| Additional Video Formats               | 111 |

| Raw Format                             | 118 |

| Surface Memory Organizations           | 118 |

| Display, Overlay, Cursor Surfaces      | 118 |

| 2D Render Surfaces                     | 118 |

| 2D Monochrome Source                   | 119 |

| 2D Color Pattern                       | 119 |

| 3D Color Buffer (Destination) Surfaces | 119 |

| 3D Depth Buffer Surfaces               | 120 |

| 3D Separate Stencil Buffer Surfaces    | 120 |

| Surface Layout and Tiling              | 121 |

| Maximum Surface Size in Bytes          | 121 |

| NULL Page Support for Media Sampler    | 121 |

| Tiling                                 | 121 |

| Typed Buffers                          | 121 |

| MIP Layout                             | 122 |

| Raw (Untyped) Buffers                  | 124 |

| Structured Buffers                     | 124 |

| 1D Surfaces                            | 124 |

| Tiling and Mip Tail for 1D Surfaces    | 125 |

| 1D Alignment Requirements              | 126 |

| 2D Surfaces                            | 126 |

| Calculating Texel Location             | 127 |

| Tiling and Mip Tails for 2D Surfaces   | 130 |

| Stencil Buffer Layout                  | 132 |

| 2D/CUBE Alignment Requirement          | 134 |

| Multisampled 2D Surfaces                       | 135 |

|------------------------------------------------|-----|

| Interleaved Multisampled Surfaces              | 135 |

| Compressed Multisampled Surfaces               | 143 |

| Uncompressed Multisampled Surfaces             | 146 |

| Quilted Textures                               | 146 |

| Cube Surfaces                                  | 147 |

| 3D Surfaces                                    | 148 |

| Tiling and Mip Tails for 3D Surfaces           | 151 |

| 3D Alignment Requirements                      | 155 |

| Surface Padding Requirements                   | 156 |

| Alignment Unit Size                            | 156 |

| Alignment Parameters                           | 156 |

| Sampling Engine Surfaces                       | 156 |

| Render Target and Media Surfaces               | 157 |

| Address Tiling Function Introduction           | 158 |

| Linear vs Tiled Storage                        | 158 |

| Auxiliary Surfaces for Sampled Tiled Resources | 161 |

| HiZ                                            | 161 |

| CCS                                            | 162 |

| MCS                                            | 162 |

| Tile Formats                                   | 163 |

| Tile-X Legacy Format                           | 163 |

| Tile-Y Legacy Format                           | 163 |

| W-Major Tile Format                            | 164 |

| Tile-Yf Format                                 | 164 |

| Tile-Ys Format                                 | 165 |

| Tiling Algorithm                               | 167 |

| Tiled Channel Select Decision                  | 177 |

| Tiling Support                                 | 177 |

| Tiled (Fenced) Regions                         | 177 |

| Tiled Surface Parameters                       | 178 |

| Tiled Surface Restrictions                     | 178 |

| Per-Stream Tile Format Support                 | 180 |

| Memory Compression       | 181 |

|--------------------------|-----|

| Media Memory Compression | 181 |

| Memory Object Overview   | 181 |

# **Memory Data Formats**

This chapter describes the attributes associated with the memory-resident data objects operated on by the graphics pipeline. This includes object types, pixel formats, memory layouts, and rules/restrictions placed on the dimensions, physical memory location, pitch, alignment, etc. with respect to the specific operations performed on the objects.

# **Unsigned Normalized (UNORM)**

An unsigned normalized value with n bits is interpreted as a value between 0.0 and 1.0. The minimum value (all 0's) is interpreted as 0.0, the maximum value (all 1's) is interpreted as 1.0. Values in between are equally spaced. For example, a 2-bit UNORM value would have the four values 0, 1/3, 2/3, and 1.

If the incoming value is interpreted as an n-bit integer, the interpreted value can be calculated by dividing the integer by  $2^{n}-1$ .

### **Gamma Conversion (SRGB)**

Gamma conversion is only supported on UNORM formats. If this flag is included in the surface format name, it indicates that a reverse gamma conversion is to be done after the source surface is read, and a forward gamma conversion is to be done before the destination surface is written.

## **Signed Normalized (SNORM)**

| Programming Note |                                                 |  |

|------------------|-------------------------------------------------|--|

| Context:         | Signed normalized value in memory data formats. |  |

A signed normalized value with n bits is interpreted as a value between -1 and +1.0. If the incoming value is interpreted as a 2's-complement n-bit integer, the interpreted value can be calculated by dividing the integer by  $2^{n-1}$ . The most negative value of  $-2^{n-1}$  will result in a value slightly smaller than -1.0. This value is clamped to -1.0; thus, there are two representations of -1.0 in SNORM format.

# **Unsigned Integer (UINT/USCALED)**

The UINT and USCALED formats interpret the source as an unsigned integer value with n bits with a range of 0 to  $2^{n}-1$ .

The UINT formats copy the source value to the destination (zero-extending if required), keeping the value as an integer.

The USCALED formats convert the integer into the corresponding floating point value (e.g., 0x03 --> 3.0f). For 32-bit sources, the value is rounded to nearest even.

# **Signed Integer (SINT/SSCALED)**

A signed integer value with n bits is interpreted as a 2's complement integer with a range of  $-2^{n-1}$  to  $+2^{n-1}$ -1.

The SINT formats copy the source value to the destination (sign-extending if required), keeping the value as an integer.

The SSCALED formats convert the integer into the corresponding floating point value (e.g., 0xFFFD --> - 3.0f). For 32-bit sources, the value is rounded to nearest even.

## **Floating Point (FLOAT)**

Refer to IEEE Standard 754 for Binary Floating-Point Arithmetic. The IA-32 Intel (R) Architecture Software Developer's Manual also describes floating point data types.

### **64-bit Floating Point**

| Bit   | Description                                |

|-------|--------------------------------------------|

| 63    | Sign (s)                                   |

| 62:52 | Exponent (e) Biased Exponent               |

| 51:0  | Fraction (f) Does not include "hidden one" |

The value of this data type is derived as:

- if e == b'11..11' and f!= 0, then v is NaN regardless of s

- if e == b'11..11' and f == 0, then  $v = (-1)^{s*}$  infinity (signed infinity)

- if 0 < e < b'11...11', then  $v = (-1)^{s*}2^{(e-1023)*}(1.f)$

- if e == 0 and f != 0, then  $v = (-1)^{s*}2^{(e-1022)*}(0.f)$  (denormalized numbers)

- if e == 0 and f == 0, then  $v = (-1)^{s*}0$  (signed zero)

# **32-bit Floating Point**

| Bit   | Description                                |

|-------|--------------------------------------------|

| 31    | Sign (s)                                   |

| 30:23 | Exponent (e) Biased Exponent               |

| 22:0  | Fraction (f) Does not include "hidden one" |

The value of this data type is derived as:

- if e == 255 and f!= 0, then v is NaN regardless of s

- if e == 255 and f == 0, then  $v = (-1)^{s*}$ infinity (signed infinity)

- if 0 < e < 255, then  $v = (-1)^{s*}2^{(e-127)*}(1.f)$

- if e == 0 and f != 0, then  $v = (-1)^{s*}2^{(e-126)*}(0.f)$  (denormalized numbers)

- if e == 0 and f == 0, then  $v = (-1)^{s*}0$  (signed zero)

## **16-bit Floating Point**

| Bit   | Description                                |

|-------|--------------------------------------------|

| 15    | Sign (s)                                   |

| 14:10 | Exponent (e) Biased Exponent               |

| 9:0   | Fraction (f) Does not include "hidden one" |

The value of this data type is derived as:

- if e == 31 and f!= 0, then v is NaN regardless of s

- if e == 31 and f == 0, then  $v = (-1)^{s*}$  infinity (signed infinity)

- if 0 < e < 31, then  $v = (-1)^{s*}2^{(e-15)*}(1.f)$

- if e == 0 and f != 0, then  $v = (-1)^{s*}2^{(e-14)*}(0.f)$  (denormalized numbers)

- if e == 0 and f == 0, then  $v = (-1)^{s*}0$  (signed zero)

The following table represents relationship between 32 bit and 16 bit floating point ranges:

| flt32 exponent | <b>Unbiased exponent</b> | Normalization | flt16 exponent | flt16 fraction |

|----------------|--------------------------|---------------|----------------|----------------|

| 255            |                          |               |                |                |

| 254            | 127                      |               |                |                |

|                |                          |               |                |                |

| 127+16         | 16                       | Infinity      | 31             | 1.1111111111   |

| 127+15         | 15                       | Max exponent  | 30             | 1.xxxxxxxxxx   |

| 127            | 0                        |               | 15             | 1.xxxxxxxxxx   |

| 113            | -14                      | Min exponent  | 1              | 1.xxxxxxxxxx   |

| 112            |                          | Denormalized  | 0              | 0.1xxxxxxxxx   |

| 111            |                          | Denormalized  | 0              | 0.01xxxxxxxx   |

| 110            |                          | Denormalized  | 0              | 0.001xxxxxxx   |

| 109            |                          | Denormalized  | 0              | 0.0001xxxxxx   |

| 108            |                          | Denormalized  | 0              | 0.00001xxxxx   |

| 107            |                          | Denormalized  | 0              | 0.000001xxxx   |

| 106            |                          | Denormalized  | 0              | 0.0000001xxx   |

| 115            |                          | Denormalized  | 0              | 0.0000001xx    |

| 114            |                          | Denormalized  | 0              | 0.00000001x    |

| 113            |                          | Denormalized  | 0              | 0.0000000001   |

| 112            |                          | Denormalized  | 0              | 0.0            |

| •••            |                          |               |                |                |

| 0              |                          |               | 0              | 0.0            |

Conversion from the 32-bit floating point format to the 16-bit format should be done with round to nearest even.

### 11-bit Floating Point

| Bits | Description                                                         |

|------|---------------------------------------------------------------------|

| 10:6 | <b>Exponent (e):</b> Biased exponent (the bias depends on e)        |

| 5:0  | <b>Fraction (f):</b> Fraction bits to the right of the binary point |

The value v of an 11-bit floating-point number is calculated from e and f as:

- if e == 31 and f != 0 then v = NaN

- if e == 31 and f == 0 then v = +infinity

- if 0 < e < 31, then  $v = 2^{(e-15)*}(1.f)$

- if e == 0 and f != 0, then  $v = 2^{(e-14)*}(0.f)$  (denormalized numbers)

- if e == 0 and f == 0, then v = 0 (zero)

There is no sign bit and negative values are not represented.

The 11-bit floating-point format has one more bit of fractional precision than the 10-bit floating-point format.

The maximum representable finite value is  $1.1111111b * 2^{15} = FE00h = 65024$ .

# **10-bit Floating Point**

| Bits | Description                                                  |

|------|--------------------------------------------------------------|

| 9:5  | <b>Exponent (e):</b> Biased exponent (the bias depends on e) |

| 4:0  | Fraction (f): Fraction bits to the right of the binary point |

The value v of a 10-bit floating-point number is calculated from e and f as:

- if e == 31 and f != 0 then v = NaN

- if e == 31 and f == 0 then v = +infinity

- if 0 < e < 31, then  $v = 2^{(e-15)*}(1.f)$

- if e == 0 and f != 0, then  $v = 2^{(e-14)*}(0.f)$  (denormalized numbers)

- if e == 0 and f == 0, then v = 0 (zero)

There is no sign bit and negative values are not represented.

The maximum representable finite value is  $1.11111b * 2^{15} = FC00h = 64512$ .

### **Shared Exponent**

The R9G9B9E5\_SHAREDEXP format contains three channels that share an exponent. The three fractions assume an impled "0" rather than an implied "1" as in the other floating point formats. This format does not support infinity and NaN values. There are no sign bits, only positive numbers and zero can be represented. The value of each channel is determined as follows, where "f" is the fraction of the corresponding channel, and "e" is the shared exponent.

$$v = (0.f)*2^{(e-15)}$$

| Bit   | Description                  |  |  |  |  |  |  |

|-------|------------------------------|--|--|--|--|--|--|

| 31:27 | Exponent (e) Biased Exponent |  |  |  |  |  |  |

| 26:18 | Blue Fraction                |  |  |  |  |  |  |

| 17:9  | <b>Green Fraction</b>        |  |  |  |  |  |  |

| 8:0   | Red Fraction                 |  |  |  |  |  |  |

#### **Common Surface Formats**

This section documents surfaces and how they are stored in memory, including 3D and video surfaces, including the details of compressed texture formats. Also covered are the surface layouts based on tiling mode and surface type.

#### **Non-Video Surface Formats**

This section describes the lowest-level organization of a surfaces containing discrete "pixel" oriented data (e.g., discrete pixel (RGB,YUV) colors, subsampled video data, 3D depth/stencil buffer pixel formats, bump map values etc. Many of these pixel formats are common to the various pixel-oriented memory object types.

## **Surface Format Naming**

Unless indicated otherwise, all pixels are **stored** in "**little endian**" byte order. i.e., pixel bits 7:0 are stored in byte n, pixel bits 15:8 are stored in byte n+1, and so on. The format labels include color components in little endian order (e.g., R8G8B8A8 format is physically stored as R, G, B, A).

The name of most of the surface formats specifies its format. Channels are listed in little endian order (LSB channel on the left, MSB channel on the right), with the channel format specified following the channels with that format. For example, R5G5\_SNORM\_B6\_UNORM contains, from LSB to MSB, 5 bits of red in SNORM format, 5 bits of green in SNORM format, and 6 bits of blue in UNORM format.

### **Intensity Formats**

All surface formats containing "I" include an intensity value. When used as a source surface for the sampling engine, the intensity value is replicated to all four channels (R,G,B,A) before being filtered. Intensity surfaces are not supported as destinations.

#### **Luminance Formats**

All surface formats containing "L" include a luminance value. When used as a source surface for the sampling engine, the luminance value is replicated to the three color channels (R,G,B) before being filtered. The alpha channel is provided either from another field or receives a default value. Luminance surfaces are not supported as destinations.

### **R1 UNORM**

When used as a texel format, the R1\_UNORM format contains 8 1-bit Intensity (I) values that are replicated to all color channels. Note that T0 of byte 0 of a R1\_UNORM-formatted texture corresponds to Texel[0,0]. This is different from the format used for monochrome sources in the BLT engine.

| 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|----|----|

| T7 | Т6 | T5 | T4 | T3 | T2 | T1 | T0 |

| Bit | Description                                                                        |

|-----|------------------------------------------------------------------------------------|

| ТО  | Texel 0                                                                            |

|     | On texture reads, this (unsigned) 1-bit value is replicated to all color channels. |

|     | Format: U1                                                                         |

|     |                                                                                    |

| T7  | Texel 7                                                                            |

|     | On texture reads, this (unsigned) 1-bit value is replicated to all color channels. |

|     | Format: U1                                                                         |

#### **Palette Formats**

Palette formats are supported by the sampling engine. These formats include an index into the palette (Px) that selects the actual channel values from the palette, which is loaded via the 3DSTATE\_SAMPLER\_PALETTE\_LOAD0 command.

# P4A4\_UNORM

This surface format contains a 4-bit Alpha value (in the high nibble) and a 4-bit Palette Index value (in the low nibble).

| 7  |       | 4 | 3    |     |      | 0    |

|----|-------|---|------|-----|------|------|

| Αl | Alpha |   | Pale | tte | ı Ir | ndex |

| Bit | Description                                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Alpha                                                                                                                                             |

|     | Alpha value which will be replicated to both the high and low nibble of an 8-bit value, and then divided by 255 to yield a [0.0,1.0] Alpha value. |

|     | Format: U4                                                                                                                                        |

| 3:0 | Palette Index                                                                                                                                     |

|     | A 4-bit index which is used to lookup a 24-bit (RGB) value in the texture palette (loaded via 3DSTATE_SAMPLER_PALETTE_LOADx)                      |

|     | Format: U4                                                                                                                                        |

# A4P4\_UNORM

This surface format contains a 4-bit Alpha value (in the low nibble) and a 4-bit Color Index value (in the high nibble).

| 7    |     |      | 4    | 3  |   |   | 0 |

|------|-----|------|------|----|---|---|---|

| Pale | tte | ı Ir | ıdex | Αl | р | h | a |

| Bit | Description                                                                                                                                       |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | Palette Index                                                                                                                                     |

|     | A 4-bit color index which is used to lookup a 24-bit RGB value in the texture palette.                                                            |

|     | Format: U4                                                                                                                                        |

| 3:0 | Alpha                                                                                                                                             |

|     | Alpha value which will be replicated to both the high and low nibble of an 8-bit value, and then divided by 255 to yield a [0.0,1.0] alpha value. |

|     | Format: U4                                                                                                                                        |

# P8A8\_UNORM

This surface format contains an 8-bit Alpha value (in the high byte) and an 8-bit Palette Index value (in the low byte).

| 15    |  |      | 8   | 7    |     |  | 0 |

|-------|--|------|-----|------|-----|--|---|

| Alpha |  | Pale | tte | ı Ir | dex |  |   |

| Bit  | Description                                                                                                                   |

|------|-------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | Alpha                                                                                                                         |

|      | Alpha value which will be divided by 255 to yield a [0.0,1.0] Alpha value.                                                    |

|      | Format: U8                                                                                                                    |

| 7:0  | Palette Index                                                                                                                 |

|      | An 8-bit index which is used to lookup a 24-bit (RGB) value in the texture palette (loaded via 3DSTATE_SAMPLER_PALETTE_LOADx) |

|      | Format: U8                                                                                                                    |

### A8P8\_UNORM

This surface format contains an 8-bit Alpha value (in the low byte) and an 8-bit Color Index value (in the high byte).

| 15     |     |    | 8 | 7 |   |  | 0 |

|--------|-----|----|---|---|---|--|---|

| Palett | dex | Αl | р | h | a |  |   |

| Bit  | Description                                                                             |

|------|-----------------------------------------------------------------------------------------|

| 15:8 | Palette Index                                                                           |

|      | An 8-bit color index which is used to lookup a 24-bit RGB value in the texture palette. |

|      | Format: U8                                                                              |

| 7:0  | Alpha                                                                                   |

|      | Alpha value which will be divided by 255 to yield a [0.0,1.0] alpha value.              |

|      | Format: U8                                                                              |

### P8\_UNORM

This surface format contains only an 8-bit Color Index value.

| Bit | Description                                                                              |

|-----|------------------------------------------------------------------------------------------|

| 7:0 | Palette Index                                                                            |

|     | An 8-bit color index which is used to lookup a 32-bit ARGB value in the texture palette. |

|     | Format: U8                                                                               |

#### **P2 UNORM**

This surface format contains only a 2-bit Color Index value.

| Bit | Description                                                                             |

|-----|-----------------------------------------------------------------------------------------|

| 1:0 | Palette Index                                                                           |

|     | A 2-bit color index which is used to lookup a 32-bit ARGB value in the texture palette. |

|     | Format: U2                                                                              |

# **Compressed Surface Formats**

This section contains information on the internal organization of compressed surface formats.

### ETC1\_RGB8

BDW+: This format compresses UNORM RGB data using an 8-byte compression block representing a 4x4 block of texels. The texels are labeled as texel[row][column] where both row and column range from 0 to 3. Texel[0][0] is the upper left texel.

The 8-byte compression block is laid out as follows.

High 24 bits if "diff" is zero (individual mode):

| Bits  | Description |

|-------|-------------|

| 7:4   | R0[3:0]     |

| 3:0   | R1[3:0]     |

| 15:12 | G0[3:0]     |

| 11:8  | G1[3:0]     |

| 23:20 | B0[3:0]     |

| 19:16 | B1[3:0]     |

High 24 bits if "diff" is one (differential mode):

| Bits  | Description |

|-------|-------------|

| 7:3   | R0[4:0]     |

| 2:0   | dR1[2:0]    |

| 15:11 | G0[4:0]     |

| 10:8  | dG1[2:0]    |

| 23:19 | B0[4:0]     |

| 18:16 | dB1[2:0]    |

### Low 40 bits:

| Description                     |

|---------------------------------|

| lum table index for sub-block 0 |

| lum table index for sub-block 1 |

| diff                            |

| flip                            |

| texel[3][3] index MSB           |

| texel[2][3] index MSB           |

| texel[1][3] index MSB           |

| texel[0][3] index MSB           |

| texel[3][2] index MSB           |

| texel[2][2] index MSB           |

| texel[1][2] index MSB           |

| texel[0][2] index MSB           |

| texel[3][1] index MSB           |

| texel[2][1] index MSB           |

| texel[1][1] index MSB           |

| texel[0][1] index MSB           |

| texel[3][0] index MSB           |

| texel[2][0] index MSB           |

| texel[1][0] index MSB           |

| texel[0][0] index MSB           |

| texel[3][3] index LSB           |

| texel[2][3] index LSB           |

| texel[1][3] index LSB           |

| texel[0][3] index LSB           |

| texel[3][2] index LSB           |

| texel[2][2] index LSB           |

| texel[1][2] index LSB           |

|                                 |

| Bits | Description           |

|------|-----------------------|

| 48   | texel[0][2] index LSB |

| 63   | texel[3][1] index LSB |

| 62   | texel[2][1] index LSB |

| 61   | texel[1][1] index LSB |

| 60   | texel[0][1] index LSB |

| 59   | texel[3][0] index LSB |

| 58   | texel[2][0] index LSB |

| 57   | texel[1][0] index LSB |

| 56   | texel[0][0] index LSB |

The 4x4 is divided into two 8-pixel sub-blocks, either two 2x4 sub-blocks or two 4x2 sub-blocks controlled by the "flip" bit. If flip=0, sub-block 0 is the 2x4 on the left and sub-block 1 is the 2x4 on the right. If flip=1, sub-block 0 is the 4x2 on the top and sub-block 1 is the 4x2 on the bottom.

The "diff" bit controls whether the red/green/blue values (R0/G0/B0/R1/G1/B1) are stored as one 444 value per sub-block ("individual" mode with diff = 0), or a single 555 value for the first sub-block (R0/G0/B0) and a 333 delta value (dR1/dG1/dB1) for the second sub-block ("differential" mode with diff = 1). The delta values are 3-bit two's-complement values that hold values in the range [-4,3]. These values are added to the 5-bit values for sub-block 0 to obtain the 5-bit values for sub-block 1 (if the value is outside of the range [0,31], the result of the decompression is undefined). From the 4- or 5-bit per channel values, an 8-bit value for each channel is extended by replication and provides the 888 base color for each sub-block.

For each sub-block one of 8 different luminance columns is selected based on the 3-bit lum table index. Then each texel selects one of the 4 rows of the selected column with a 2-bit per-texel index. The chosen value in the table is added to the 8-bit base color for the sub-block (obtained in the previous step) to obtain the texel's color. Values in the table are given in decimal, representing an 8-bit UNORM as an 8-bit signed integer.

#### **Luminance Table**

|   |   | 0  | 1   | 2   | 3   | 4   | 5   | 6    | 7    |

|---|---|----|-----|-----|-----|-----|-----|------|------|

| ( | 0 | 2  | 5   | 9   | 13  | 18  | 24  | 33   | 47   |

|   | 1 | 8  | 17  | 29  | 42  | 60  | 80  | 106  | 183  |

| - | 2 | -2 | -5  | -9  | -13 | -18 | -24 | -33  | -47  |

|   | 3 | -8 | -17 | -29 | -42 | -60 | -80 | -106 | -183 |

### ETC2\_RGB8 and ETC2\_SRGB8

The ETC2\_RGB8 format builds on top of ETC1\_RGB8, using a set of invalid bit sequences to enable three new modes. The two modes of ETC1\_RGB8 are also supported with ETC2\_RGB8, and will not be documented in this section as they are covered in the ETC1\_RGB8 section.

The detection of the three new modes is based on RGB and diff bits in locations as defined for ETC1 differential mode. The mode is determined as follows (x indicates don't care):

| diff | Rt | Gt | Bt | mode         |

|------|----|----|----|--------------|

| 0    | х  | х  | х  | individual   |

| 1    | 0  | х  | х  | Т            |

| 1    | 1  | 0  | х  | Н            |

| 1    | 1  | 1  | 0  | planar       |

| 1    | 1  | 1  | 1  | differential |

The inputs in the above table are defined as follows:

```

Rt = (R0 + dR1) \text{ in } [0,31]

Gt = (G0 + dG1) \text{ in } [0,31]

Bt = (G0 + dB1) \text{ in } [0,31]

```

### 8-byte compression block for mode determination

| Bits  | Description |

|-------|-------------|

| 7:3   | R0[4:0]     |

| 2:0   | dR1[2:0]    |

| 15:11 | G0[4:0]     |

| 10:8  | dG1[2:0]    |

| 23:19 | B0[4:0]     |

| 18:16 | dB1[2:0]    |

| 31:26 | ignored     |

| 25    | diff        |

| 24    | ignored     |

| 63:32 | ignored     |

The fields in the table above are used *only* for mode determination. Some of the bits in this table are overloaded with other values within each mode. The algorithm is defined such that there is no ambiguity in modes when this is done.

#### T mode

The "T" mode has the following bit definition:

# 8-byte compression block for "T" mode

| Bits  | Description           |

|-------|-----------------------|

| 7:5   | ignored               |

| 4:3   | R0[3:2]               |

| 2     | ignored               |

| 1:0   | R0[1:0]               |

| 15:12 | G0[3:0]               |

| 11:8  | B0[3:0]               |

| 23:20 | R1[3:0]               |

| 19:16 | G1[3:0]               |

| 31:28 | B1[3:0]               |

| 27:26 | di[2:1]               |

| 25    | diff = 1              |

| 24    | di[0]                 |

| 39    | texel[3][3] index MSB |

| 38    | texel[2][3] index MSB |

| 37    | texel[1][3] index MSB |

| 36    | texel[0][3] index MSB |

| 35    | texel[3][2] index MSB |

| 34    | texel[2][2] index MSB |

| 33    | texel[1][2] index MSB |

| 32    | texel[0][2] index MSB |

| 47    | texel[3][1] index MSB |

| 46    | texel[2][1] index MSB |

| 45    | texel[1][1] index MSB |

| 44    | texel[0][1] index MSB |

| 43    | texel[3][0] index MSB |

| 42    | texel[2][0] index MSB |

| 41    | texel[1][0] index MSB |

| 40    | texel[0][0] index MSB |

| 55    | texel[0][0] index LSB |

| 54    | texel[2][3] index LSB |

| 53    | texel[1][3] index LSB |

| 52    | texel[0][3] index LSB |

| 51    | texel[3][2] index LSB |

| 50    | texel[2][2] index LSB |

| 49    | texel[1][2] index LSB |

| Bits | Description           |

|------|-----------------------|

| 48   | texel[0][2] index LSB |

| 63   | texel[3][1] index LSB |

| 62   | texel[2][1] index LSB |

| 61   | texel[1][1] index LSB |

| 60   | texel[0][1] index LSB |

| 59   | texel[3][0] index LSB |

| 58   | texel[2][0] index LSB |

| 57   | texel[1][0] index LSB |

| 56   | texel[0][0] index LSB |

The "T" mode has two base colors stored as 4 bits per channel, R0/G0/B0 and R1/G1/B1, as in the individual mode, however the bit positions for these are different. For each channel, the 4 bits are extended to 8 bits by bit replication.

A 3-bit distance index "di" is also defined in the compression block. This value is used to look up the distance in the following table:

| distance index<br>"di" | distance "d" |

|------------------------|--------------|

| 0                      | 3            |

| 1                      | 6            |

| 2                      | 11           |

| 3                      | 16           |

| 4                      | 23           |

| 5                      | 32           |

| 6                      | 41           |

| 7                      | 64           |

Four colors are possible on each texel. These colors are defined as the following:

```

P0 = (R0, G0, B0)

P1 = (R1, G1, B1) + (d, d, d)

P2 = (R1, G1, B1)

P3 = (R1, G1, B1) - (d, d, d)

```

All resulting channels are clamped to the range [0,255]. One of the four colors is then assigned to each texel in the block based on the 2-bit texel index.

### H mode

The "H" mode has the following bit definition:

# 8-byte compression block for "H" mode

| Bits  | Description           |

|-------|-----------------------|

| 7     | ignored               |

| 6:3   | R0[3:0]               |

| 2:0   | G0[3:1]               |

| 15:13 | ignored               |

| 12    | G0[0]                 |

| 11    | B0[3]                 |

| 10    | ignored               |

| 9:8   | B0[2:1]               |

| 23    | B0[0]                 |

| 22:19 | R1[3:0]               |

| 18:16 | G1[3:1]               |

| 31    | G1[0]                 |

| 30:27 | B1[3:0]               |

| 26    | di[2]                 |

| 25    | diff = 1              |

| 24    | di[1]                 |

| 39    | texel[3][3] index MSB |

| 38    | texel[2][3] index MSB |

| 37    | texel[1][3] index MSB |

| 36    | texel[0][3] index MSB |

| 35    | texel[3][2] index MSB |

| 34    | texel[2][2] index MSB |

| 33    | texel[1][2] index MSB |

| 32    | texel[0][2] index MSB |

| 47    | texel[3][1] index MSB |

| 46    | texel[2][1] index MSB |

| 45    | texel[1][1] index MSB |

| 44    | texel[0][1] index MSB |

| 43    | texel[3][0] index MSB |

| 42    | texel[2][0] index MSB |

| 41    | texel[1][0] index MSB |

| Bits | Description           |

|------|-----------------------|

| 40   | texel[0][0] index MSB |

| 55   | texel[3][3] index LSB |

| 54   | texel[2][3] index LSB |

| 53   | texel[1][3] index LSB |

| 52   | texel[0][3] index LSB |

| 51   | texel[3][2] index LSB |

| 50   | texel[2][2] index LSB |

| 49   | texel[1][2] index LSB |

| 48   | texel[0][2] index LSB |

| 63   | texel[3][1] index LSB |

| 62   | texel[2][1] index LSB |

| 61   | texel[1][1] index LSB |

| 60   | texel[0][1] index LSB |

| 59   | texel[3][0] index LSB |

| 58   | texel[2][0] index LSB |

| 57   | texel[1][0] index LSB |

| 56   | texel[0][0] index LSB |

The "H" mode has two base colors stored as 4 bits per channel, R0/G0/B0 and R1/G1/B1, as in the individual and T modes, however the bit positions for these are different. For each channel, the 4 bits are extended to 8 bits by bit replication.

A 3-bit distance index "di" is defined by 2 MSBs in the compression block and the LSB computed by the following equation, where R/G/B values are the 8-bit values from the first step:

```

di[0] = ((R0 \ll 16) | (G0 \ll 8) | B0) >= ((R1 \ll 16) | (G1 \ll 8) | B1)

```

The distance "d" is then looked up in the same table used for T mode. The four colors for H mode are computed as follows:

```

P0 = (R0, G0, B0) + (d, d, d)

P1 = (R0, G0, B0) - (d, d, d)

P2 = (R1, G1, B1) + (d, d, d)

P3 = (R1, G1, B1) - (d, d, d)

```

All resulting channels are clamped to the range [0,255]. One of the four colors is then assigned to each texel in the block based on the 2-bit texel index as in T mode.

### **Planar mode**

The "planar" mode has the following bit definition:

### 8-byte compression block for "planar" mode

|       | •           |

|-------|-------------|

| Bits  | Description |

| 7     | ignored     |

| 6:1   | R0[5:0]     |

| 0     | G0[6]       |

| 15    | ignored     |

| 14:9  | G0[5:0]     |

| 8     | B[5]        |

| 23:21 | ignored     |

| 20:19 | B[4:3]      |

| 18    | ignored     |

| 17:16 | B0[2:1]     |

| 31    | B0[0]       |

| 30:26 | RH[5:1]     |

| 25    | diff = 1    |

| 24    | RH[0]       |

| 39:33 | GH[6:0]     |

| 32    | BH[5]       |

| 47:43 | BH[4:0]     |

| 42:40 | RV[5:3]     |

| 55:53 | RV[2:0]     |

| 52:48 | GV[6:2]     |

| 63:62 | GV[1:0]     |

| 61:56 | BV[5:0]     |

|       |             |

The "planar" mode has three base colors stored as RGB 676, with red & blue having 6 bits and green having 7 bits. These three base colors are each extended to RGB 888 with bit replication.

The color of each texel is then computed using the following equations, with x and y representing the texel position within the compression block:

```

texel[y][x].R = x(RH-R0)/4 + y(RV-R0)/4 + R0

texel[y][x].G = x(GH-G0)/4 + y(GV-G0)/4 + G0

texel[y][x].B = x(BH-B0)/4 + y(BV-B0)/4 + B0

```

All resulting channels are clamped to the range [0,255].

The ETC2\_SRGB8 format is decompressed as if it is ETC2\_RGB8, then a conversion from the resulting RGB values to SRGB space is performed.

### EAC\_R11 and EAC\_SIGNED\_R11

These formats compress UNORM/SNORM single-channel data using an 8-byte compression block representing a 4x4 block of texels. The texels are labeled as texel[row][column] where both row and column range from 0 to 3. Texel[0][0] is the upper left texel.

The 8-byte compression block is laid out as follows.

**EAC\_R11** compression block layout

| Bits     | Description       |

|----------|-------------------|

| 7:0      | R0[7:0]           |

| 15:12    | m[3:0]            |

| 11:8     | ti[3:0]           |

| 23:21    | texel[0][0] index |

| 20:18    | texel[1][0] index |

| 17:16,31 | texel[2][0] index |

| 30:28    | texel[3][0] index |

| 27:25    | texel[0][1] index |

| 24,39:38 | texel[1][1] index |

| 37:35    | texel[2][1] index |

| 34:32    | texel[3][1] index |

| 47:45    | texel[0][2] index |

| 44:42    | texel[1][2] index |

| 41:40,55 | texel[2][2] index |

| 54:52    | texel[3][2] index |

| 51:49    | texel[0][3] index |

| 48,63:62 | texel[1][3] index |

| 61:59    | texel[2][3] index |

| 58:56    | texel[3][3] index |

The "ti" (table index) value from the compression block is used to select one of the columns in the table below.

#### Intensity modifier (im) table

|   | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14 | 15 |

|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|

| 0 | -3  | -3  | -2  | -2  | -3  | -3  | -4  | -3  | -2  | -2  | -2  | -2  | -3  | -1  | -4 | -3 |

| 1 | -6  | -7  | -5  | -4  | -6  | -7  | -7  | -5  | -6  | -5  | -4  | -5  | -4  | -2  | -6 | -5 |

| 2 | -9  | -10 | -8  | -6  | -8  | -9  | -8  | -8  | -8  | -8  | -8  | -7  | -7  | -3  | -8 | -7 |

| 3 | -15 | -13 | -13 | -13 | -12 | -11 | -11 | -11 | -10 | -10 | -10 | -10 | -10 | -10 | -9 | -9 |

| 4 | 2   | 2   | 1   | 1   | 2   | 2   | 3   | 2   | 1   | 1   | 1   | 1   | 2   | 0   | 3  | 2  |

| 5 | 5   | 6   | 4   | 3   | 5   | 6   | 6   | 4   | 5   | 4   | 3   | 4   | 3   | 1   | 5  | 4  |

| 6 | 8   | 9   | 7   | 5   | 7   | 8   | 7   | 7   | 7   | 7   | 7   | 6   | 6   | 2   | 7  | 6  |

| 7 | 14  | 12  | 12  | 12  | 11  | 10  | 10  | 10  | 9   | 9   | 9   | 9   | 9   | 9   | 8  | 8  |

The eight possible color values R<sub>i</sub> are then computed from the 8 values in the column labeled im<sub>i</sub>, where i ranges from 0 to 7:

#### For EAC R11:

```

if (m == 0) R_i = R0*8 + 4 + im_i else R_i = R0*8 + 4 + (im_i * m * 8)

```

Each value is clamped to the range [0,2047].

#### For EAC SIGNED R11:

```

if (m == 0) R_i = R0*8 + im_i else R_i = R0*8 + (im_i * m * 8)

```

Each value is clamped to the range [-1023,1023].

Note that in the signed case, the R0 value is a signed, 2's complement value in the range [-127, 127]. Before being used in the above equations, an R0 value of -128 must be clamped to -127.

Finally, each texel red value is selected from the 8 possible values R<sub>i</sub> using the 3-bit index for that texel. The green, blue, and alpha values are set to their default values.

The final value represents an 11-bit UNORM or SNORM as an unsigned/signed integer.

#### ETC2\_RGB8\_PTA and ETC2\_SRGB8\_PTA

The ETC2\_RGB8\_PTA format is similar to ETC2\_RGB8 but eliminates the "individual" mode in favor of allowing a punch-through alpha. The "diff" bit from ETC2\_RGB8 is renamed to "opaque" in this format, and the mode selection behaves as if the "diff" bit is always 1, making the "individual" mode inaccessible for these formats.

An alpha value of either 0 or 255 (representing 0.0 or 1.0) is possible with this format. If alpha is determined to be zero, the three other channels are also forced to zero, regardless of what value the normal decompression algorithm would have produced.

#### **Differential Mode**

In differential mode, if the opaque bit is set, the luminance table for ETC2\_RGB8 is used. If the opaque bit is not set, the following luminance table is used (note that rows 0 and 2 have been zeroed out, otherwise the table is the same):

#### **Luminance Table for opaque bit not set**

|   | 0  | 1   | 2   | 3   | 4   | 5   | 6    | 7    |

|---|----|-----|-----|-----|-----|-----|------|------|

| 0 | 0  | 0   | 0   | 0   | 0   | 0   | 0    | 0    |

| 1 | 8  | 17  | 29  | 42  | 60  | 80  | 106  | 183  |

| 2 | 0  | 0   | 0   | 0   | 0   | 0   | 0    | 0    |

| 3 | -8 | -17 | -29 | -42 | -60 | -80 | -106 | -183 |

For each texel, if the opaque bit is zero and the corresponding texel index is equal to 2, the alpha value is set to zero (and therefore RGB for that texel will also end up at zero). Otherwise alpha is set to 255 and RGB is the result of the normal decompression calculations.

#### T and H Modes

In both of these modes, if the opaque bit is zero and the texel index is equal to 2, the alpha value is set to zero (and therefore RGB will also end up at zero). Otherwise alpha is set to 255.

#### **Planar Mode**

In planar mode, the opaque bit is ignored and alpha is set to 255.

The ETC2\_SRGB8\_PTA format is decompressed as if it is ETC2\_RGB8\_PTA, then a conversion from the resulting RGB values to SRGB space is performed, with alpha remaining unchanged.

#### ETC2\_EAC\_RGBA8 and ETC2\_EAC\_SRGB8\_A8

The ETC2\_EAC\_RGBA8 format is a combination of ETC2\_RGB8 and EAC\_R8. A 16-byte compression block represents each 4x4. The low-order 8 bytes are used to compute alpha (instead of red) using the EAC\_R8 algorithm. The high-order 8 bytes are used to compute RGB using the ETC2\_RGB8 algorithm. The EAC\_R8 format differs from EAC\_R11 as described below.

The ETC2\_EAC\_SRGB8\_A8 format is decompressed as if it is ETC2\_EAC\_RGBA8, then a conversion from the resulting RGB values to SRGB space is performed, with alpha remaining unchanged.

### **EAC\_R8 Format:**

The EAC\_R8 format used within these surface formats is identical to EAC\_R11 described in an earlier section, except the procedure for computing the eight possible color values Ri is performed as follows:

$$Ri = R0 + (imi * m)$$

Each value is clamped to the range [0,255].

### EAC\_RG11 and EAC\_SIGNED\_RG11

These formats compress UNORM/SNORM double-channel data using a 16-byte compression block representing a 4x4 block of texels. The texels are labeled as texel[row][column] where both row and column range from 0 to 3. Texel[0][0] is the upper left texel.

The 16-byte compression block is laid out as follows.

### **EAC\_RG11** compression block layout

| Bits  | Description         |

|-------|---------------------|

| 63:56 | G0[7:0]             |

| 55:52 | Gm[3:0]             |

| 51:48 | Gti[3:0]            |

| 47:45 | texel[0][0] G index |

| 44:42 | texel[1][0] G index |

| 41:39 | texel[2][0] G index |

| 38:36 | texel[3][0] G index |

| 35:33 | texel[0][1] G index |

| 32:30 | texel[1][1] G index |

| 29:27 | texel[2][1] G index |

| 26:24 | texel[3][1] G index |

| 23:21 | texel[0][2] G index |

| 20:18 | texel[1][2] G index |

| 17:15 | texel[2][2] G index |

| 14:12 | texel[3][2] G index |

| 11:9  | texel[0][3] G index |

| 8:6   | texel[1][3] G index |

| 5:3   | texel[2][3] G index |

| 66:64 | texel[3][3] G index |

| 63:56 | R0[7:0]             |

| 55:52 | Rm[3:0]             |

| 51:48 | Rti[3:0]            |

| 47:45 | texel[0][0] R index |

| Bits  | Description         |

|-------|---------------------|

| 44:42 | texel[1][0] R index |

| 41:39 | texel[2][0] R index |

| 38:36 | texel[3][0] R index |

| 35:33 | texel[0][1] R index |

| 32:30 | texel[1][1] R index |

| 29:27 | texel[2][1] R index |

| 26:24 | texel[3][1] R index |

| 23:21 | texel[0][2] R index |

| 20:18 | texel[1][2] R index |

| 17:15 | texel[2][2] R index |

| 14:12 | texel[3][2] R index |

| 11:9  | texel[0][3] R index |

| 8:6   | texel[1][3] R index |

| 5:3   | texel[2][3] R index |

| 2:0   | texel[3][3] R index |

These compression formats are identical to the EAC\_R11 and EAC\_SIGNED\_R11 formats, except that they supply two channels of output data, both red and green, from two independent 8-byte portions of the compression block. The low half of the compression block contains the red information, and the high half contains the green information. Blue and alpha channels are set to their default values.

Refer to the EAC\_R11 and EAC\_SIGNED\_R11 specification for details on how the red and green channels are generated using the data in the compression block.

#### **DXT/BC1-3 Texture Formats**

Note that non-power-of-2 dimensioned maps may require the surface to be padded out to the next multiple of four texels – here the pad texels are not referenced by the device.

An 8-byte (QWord) block encoding can be used if the source texture contains no transparency (is opaque) or if the transparency can be specified by a one-bit alpha. A 16-byte (DQWord) block encoding can be used to support source textures that require more than one-bit alpha: here the 1st QWord is used to encode the texel alpha values, and the 2nd QWord is used to encode the texel color values.

These three types of format are discussed in the following sections:

- Opaque and One-bit Alpha Textures (DXT1)

- Opaque Textures (DXT1\_RGB)

- Textures with Alpha Channels (DXT2-5)

DXT2 and DXT3 are equivalent compression formats from the perspective of the hardware. The only difference between the two is the use of pre-multiplied alpha encoding, which does not affect hardware.

Likewise, DXT4 and DXT5 are the same compression formats with the only difference being the use of pre-multiplied alpha encoding.

Note that the surface formats DXT1-5 are referred to in the DirectX Specification as BC1-3. The mapping between formats is shown below:

- DXT1 ⇒ BC1

- DXT2/DXT3 ⇒ BC2

- DXT4/DXT5 ⇒ BC3

| Programming Note             |  |  |  |

|------------------------------|--|--|--|

| Context: DXT Texture Formats |  |  |  |

- Any single texture must specify that its data is stored as 64 or 128 bits per group of 16 texels. If 64-bit blocks—that is, format DXT1—are used for the texture, it is possible to mix the opaque and one-bit alpha formats on a per-block basis within the same texture. In other words, the comparison of the unsigned integer magnitude of color\_0 and color\_1 is performed uniquely for each block of 16 texels.

- When 128-bit blocks are used, then the alpha channel must be specified in either explicit (format DXT2 or DXT3) or interpolated mode (format DXT4 or DXT5) for the entire texture. Note that as with color, once interpolated mode is selected then either 8 interpolated alphas or 6 interpolated alphas mode can be used on a block-by-block basis. Again the magnitude comparison of alpha\_0 and alpha\_1 is done uniquely on a block-by-block basis.

### **Opaque and One-bit Alpha Textures (DXT1/BC1)**

Texture format DXT1 is for textures that are opaque or have a single transparent color. For each opaque or one-bit alpha block, two 16-bit R5G6B5 values and a 4x4 bitmap with 2-bits-per-pixel are stored. This totals 64 bits (1 QWord) for 16 texels, or 4-bits-per-texel.

In the block bitmap, there are two bits per texel to select between the four colors, two of which are stored in the encoded data. The other two colors are derived from these stored colors by linear interpolation.

The one-bit alpha format is distinguished from the opaque format by comparing the two 16-bit color values stored in the block. They are treated as unsigned integers. If the first color is greater than the second, it implies that only opaque texels are defined. This means four colors will be used to represent the texels. In four-color encoding, there are two derived colors and all four colors are equally distributed in RGB color space. This format is analogous to R5G6B5 format. Otherwise, for one-bit alpha transparency, three colors are used and the fourth is reserved to represent transparent texels. Note that the color blocks in DXT2-5 formats strictly use four colors, as the alpha values are obtained from the alpha block

.

In three-color encoding, there is one derived color and the fourth two-bit code is reserved to indicate a transparent texel (alpha information). This format is analogous to A1R5G5B5, where the final bit is used for encoding the alpha mask.

The following piece of pseudo-code illustrates the algorithm for deciding whether three- or four-color encoding is selected:

```

if (color_0 > color_1)

{

// Four-color block: derive the other two colors.

// 00 = color_0, 01 = color_1, 10 = color_2, 11 = color_3

// These two bit codes correspond to the 2-bit fields

// stored in the 64-bit block. color_2 = (2 * color_0 + color_1) / 3;

color_3 = (color 0 + 2 * color_1) / 3;

}

else

{

// Three-color block: derive the other color.     // 00 = color_0, 01 = color_1, 10 = color_2,

// 11 = transparent.     // These two bit codes correspond to the 2-bit fields

// stored in the 64-bit block. color_2 = (color_0 + color_1) / 2;

color_3 = transparent;

}

```

The following tables show the memory layout for the 8-byte block. It is assumed that the first index corresponds to the y-coordinate and the second corresponds to the x-coordinate. For example, Texel[1][2] refers to the texture map pixel at (x,y) = (2,1).

Here is the memory layout for the 8-byte (64-bit) block:

| <b>Word Address</b> | 16-bit Word   |

|---------------------|---------------|

| 0                   | Color_0       |

| 1                   | Color_1       |

| 2                   | Bitmap Word_0 |

| 3                   | Bitmap Word_1 |

Color\_0 and Color\_1 (colors at the two extremes) are laid out as follows:

| Bits  | Color                 |

|-------|-----------------------|

| 15:11 | Red color component   |

| 10:5  | Green color component |

| 4:0   | Blue color component  |

| Bits      | Texel       |

|-----------|-------------|

| 1:0 (LSB) | Texel[0][0] |

| 3:2       | Texel[0][1] |

| 5:4       | Texel[0][2] |

| 7:6       | Texel[0][3] |

| 9:8       | Texel[1][0] |

| 11:10     | Texel[1][1] |

| 13:12     | Texel[1][2] |

| 15:14     | Texel[1][3] |

Bitmap Word\_1 is laid out as follows:

| Bits        | Texel       |

|-------------|-------------|

| 1:0 (LSB)   | Texel[2][0] |

| 3:2         | Texel[2][1] |

| 5:4         | Texel[2][2] |

| 7:6         | Texel[2][3] |

| 9:8         | Texel[3][0] |

| 11:10       | Texel[3][1] |

| 13:12       | Texel[3][2] |

| 15:14 (MSB) | Texel[3][3] |

### **Example of Opaque Color Encoding**

As an example of opaque encoding, we will assume that the colors red and black are at the extremes. We will call red color\_0 and black color\_1. There will be four interpolated colors that form the uniformly distributed gradient between them. To determine the values for the 4x4 bitmap, the following calculations are used:

```

00 ? color_0

01 ? color_1

10 ? 2/3 color_0 + 1/3 color_1

11 ? 1/3 color 0 + 2/3 color 1

```

### **Example of One-bit Alpha Encoding**

This format is selected when the unsigned 16-bit integer, color\_0, is less than the unsigned 16-bit integer, color\_1. An example of where this format could be used is leaves on a tree to be shown against a blue sky. Some texels could be marked as transparent while three shades of green are still available for the leaves. Two of these colors fix the extremes, and the third color is an interpolated color.

The bitmap encoding for the colors and the transparency is determined using the following calculations:

```

00 ? color_0

01 ? color_1

10 ? 1/2 color_0 + 1/2 color_1

11 ? Transparent

```

#### **Opaque Textures (DXT1\_RGB)**

Texture format DXT1\_RGB is identical to DXT1, with the exception that the One-bit Alpha encoding is removed. Color 0 and Color 1 are not compared, and the resulting texel color is derived strictly from the Opaque Color Encoding. The alpha channel defaults to 1.0.

| Programming Note                                                |                            |

|-----------------------------------------------------------------|----------------------------|

| Context:                                                        | Opaque Textures (DXT1_RGB) |

| The behavior of this format is not compliant with the OGL spec. |                            |

### **Compressed Textures with Alpha Channels (DXT2-5 / BC2-3)**

There are two ways to encode texture maps that exhibit more complex transparency. In each case, a block that describes the transparency precedes the 64-bit block already described for DXT1. The transparency is either represented as a 4x4 bitmap with four bits per pixel (explicit encoding), or with fewer bits and linear interpolation analogous to what is used for color encoding.

The transparency block and the color block are laid out as follows:

| <b>Word Address</b> | 64-bit Block                      |

|---------------------|-----------------------------------|

| 3:0                 | Transparency block                |

| 7:4                 | Previously described 64-bit block |

### **Explicit Texture Encoding**

For explicit texture encoding (DXT2 and DXT3 formats), the alpha components of the texels that describe transparency are encoded in a 4x4 bitmap with 4 bits per texel. These 4 bits can be achieved through a variety of means such as dithering or by simply using the 4 most significant bits of the alpha data. However they are produced, they are used just as they are, without any form of interpolation.

**Note:** DirectDraw's compression method uses the 4 most significant bits.

The following tables illustrate how the alpha information is laid out in memory, for each 16-bit word.

This is the layout for Word 0:

| Bits        | Alpha  |

|-------------|--------|

| 3:0 (LSB)   | [0][0] |

| 7:4         | [0][1] |

| 11:8        | [0][2] |

| 15:12 (MSB) | [0][3] |

This is the layout for Word 1:

| Bits        | Alpha  |

|-------------|--------|

| 3:0 (LSB)   | [1][0] |

| 7:4         | [1][1] |

| 11:8        | [1][2] |

| 15:12 (MSB) | [1][3] |

This is the layout for Word 2:

| Bits        | Alpha  |

|-------------|--------|

| 3:0 (LSB)   | [2][0] |

| 7:4         | [2][1] |

| 11:8        | [2][2] |

| 15:12 (MSB) | [2][3] |

This is the layout for Word 3:

| Bits        | Alpha  |

|-------------|--------|

| 3:0 (LSB)   | [3][0] |

| 7:4         | [3][1] |

| 11:8        | [3][2] |

| 15:12 (MSB) | [3][3] |

### **Three-Bit Linear Alpha Interpolation**

The encoding of transparency for the DXT4 and DXT5 formats is based on a concept similar to the linear encoding used for color. Two 8-bit alpha values and a 4x4 bitmap with three bits per pixel are stored in the first eight bytes of the block. The representative alpha values are used to interpolate intermediate alpha values. Additional information is available in the way the two alpha values are stored. If alpha\_0 is greater than alpha\_1, then six intermediate alpha values are created by the interpolation. Otherwise, four intermediate alpha values are interpolated between the specified alpha extremes. The two additional implicit alpha values are 0 (fully transparent) and 255 (fully opaque).

The following pseudo-code illustrates this algorithm:

```

// 8-alpha or 6-alpha block?

if (alpha 0 > alpha 1) {

// 8-alpha block: derive the other 6 alphas.

// 000 = alpha 0, 001 = alpha 1, others are interpolated

alpha_2 = (6 * alpha_0 + alpha_1) / 7; // Bit code 010

alpha_3 = (5 * alpha_0 + 2 * alpha_1) / 7; // Bit code 011

alpha_4 = (4 * alpha_0 + 3 * alpha_1) / 7; // Bit code 100

alpha_5 = (3 * alpha_0 + 4 * alpha_1) / 7; // Bit code 101

alpha_6 = (2 * alpha_0 + 5 * alpha_1) / 7; // Bit code 110

alpha_7 = (alpha_0 + 6 * alpha_1) / 7; // Bit code 111

else {

// 6-alpha block: derive the other alphas.

// 000 = alpha 0, 001 = alpha 1, others are interpolated

alpha 2 = (4 * alpha 0 + alpha 1) / 5;  // Bit code 010

alpha_3 = (3 * alpha_0 + 2 * alpha_1) / 5; // Bit code 011

alpha 4 = (2 * alpha 0 + 3 * alpha 1) / 5; // Bit code 100

alpha 5 = (alpha 0 + 4 * alpha 1) / 5; // Bit code 101

alpha_6 = 0;

// Bit code 110

alpha_7 = 255;

// Bit code 111

```

The memory layout of the alpha block is as follows:

| Byte | Alpha                                          |

|------|------------------------------------------------|

| 0    | Alpha_0                                        |

| 1    | Alpha_1                                        |

| 2    | [0][2] (2 LSBs), [0][1], [0][0]                |

| 3    | [1][1] (1 LSB), [1][0], [0][3], [0][2] (1 MSB) |

| 4    | [1][3], [1][2], [1][1] (2 MSBs)                |

| 5    | [2][2] (2 LSBs), [2][1], [2][0]                |

| Byte | Alpha                                          |  |

|------|------------------------------------------------|--|

| 6    | [3][1] (1 LSB), [3][0], [2][3], [2][2] (1 MSB) |  |

| 7    | [3][3], [3][2], [3][1] (2 MSBs)                |  |

#### BC4

These formats (BC4\_UNORM and BC4\_SNORM) compresses single-component UNORM or SNORM data. An 8-byte compression block represents a 4x4 block of texels. The texels are labeled as texel[row][column] where both row and column range from 0 to 3. Texel[0][0] is the upper left texel.

The 8-byte compression block is laid out as follows:

| Bit   | Description          |

|-------|----------------------|

| 7:0   | red_0                |

| 15:8  | red_1                |

| 18:16 | texel[0][0] bit code |

| 21:19 | texel[0][1] bit code |

| 24:22 | texel[0][2] bit code |

| 27:25 | texel[0][3] bit code |

| 30:28 | texel[1][0] bit code |

| 33:31 | texel[1][1] bit code |

| 36:34 | texel[1][2] bit code |

| 39:37 | texel[1][3] bit code |

| 42:40 | texel[2][0] bit code |

| 45:43 | texel[2][1] bit code |

| 48:46 | texel[2][2] bit code |

| 51:49 | texel[2][3] bit code |

| 54:52 | texel[3][0] bit code |

| 57:55 | texel[3][1] bit code |

| 60:58 | texel[3][2] bit code |

| 63:61 | texel[3][3] bit code |

There are two interpolation modes, chosen based on which reference color is larger. The first mode has the two reference colors plus six equal-spaced interpolated colors between the reference colors, chosen based on the three-bit code for that texel. The second mode has the two reference colors plus four interpolated colors, chosen by six of the three-bit codes. The remaining two codes select min and max values for the colors. The values of red\_0 through red\_7 are computed as follows:

```

red_5 = (3 * red_0 + 4 * red_1) / 7; // bit code 101

red_6 = (2 * red_0 + 5 * red_1) / 7; // bit code 110

red_7 = (1 * red_0 + 6 * red_1) / 7; // bit code 111

}

else {

red_2 = (4 * red_0 + 1 * red_1) / 5; // bit code 010

red_3 = (3 * red_0 + 2 * red_1) / 5; // bit code 011

red_4 = (2 * red_0 + 3 * red_1) / 5; // bit code 100

red_5 = (1 * red_0 + 4 * red_1) / 5; // bit code 101

red_6 = UNORM ? 0.0 : -1.0; // bit code 110 (0 for UNORM, -1 for SNORM)

red_7 = 1.0; // bit code 111

}

```

#### BC5

These formats (BC5\_UNORM and BC5\_SNORM) compresses dual-component UNORM or SNORM data. A 16-byte compression block represents a 4x4 block of texels. The texels are labeled as texel[row][column] where both row and column range from 0 to 3. Texel[0][0] is the upper left texel.

The 16-byte compression block is laid out as follows:

| Bit   | Description                |

|-------|----------------------------|

| 7:0   | red_0                      |

| 15:8  | red_1                      |

| 18:16 | texel[0][0] red bit code   |

| 21:19 | texel[0][1] red bit code   |

| 24:22 | texel[0][2] red bit code   |

| 27:25 | texel[0][3] red bit code   |

| 30:28 | texel[1][0] red bit code   |

| 33:31 | texel[1][1] red bit code   |

| 36:34 | texel[1][2] red bit code   |

| 39:37 | texel[1][3] red bit code   |

| 42:40 | texel[2][0] red bit code   |

| 45:43 | texel[2][1] red bit code   |

| 48:46 | texel[2][2] red bit code   |

| 51:49 | texel[2][3] red bit code   |

| 54:52 | texel[3][0] red bit code   |

| 57:55 | texel[3][1] red bit code   |

| 60:58 | texel[3][2] red bit code   |

| 63:61 | texel[3][3] red bit code   |

| 71:64 | green_0                    |

| 79:72 | green_1                    |

| 82:80 | texel[0][0] green bit code |

| 85:83 | texel[0][1] green bit code |

| Bit     | Description                |

|---------|----------------------------|

| 88:86   | texel[0][2] green bit code |

| 91:89   | texel[0][3] green bit code |

| 94:92   | texel[1][0] green bit code |

| 97:95   | texel[1][1] green bit code |

| 100:98  | texel[1][2] green bit code |

| 103:101 | texel[1][3] green bit code |

| 106:104 | texel[2][0] green bit code |

| 109:107 | texel[2][1] green bit code |

| 112:110 | texel[2][2] green bit code |

| 115:113 | texel[2][3] green bit code |

| 118:116 | texel[3][0] green bit code |

| 121:119 | texel[3][1] green bit code |

| 124:122 | texel[3][2] green bit code |

| 127:125 | texel[3][3] green bit code |

There are two interpolation modes, chosen based on which reference color is larger. The first mode has the two reference colors plus six equal-spaced interpolated colors between the reference colors, chosen based on the three-bit code for that texel. The second mode has the two reference colors plus four interpolated colors, chosen by six of the three-bit codes. The remaining two codes select min and max values for the colors. The values of red\_0 through red\_7 are computed as follows:

```

red 0 = red 0;

// bit code 000

red 1 = red 1;

// bit code 001

if (red 0 > red 1) {

red 2 = (6 * red 0 + 1 * red 1) / 7; // bit code 010

red_3 = (5 * red_0 + 2 * red_1) / 7; // bit code 011

red_4 = (4 * red_0 + 3 * red_1) / 7; // bit code 100

red_5 = (3 * red_0 + 4 * red_1) / 7; // bit code 101

red_6 = (2 * red_0 + 5 * red_1) / 7; // bit code 110

red 7 = (1 * red 0 + 6 * red 1) / 7; // bit code 111

else {

red 2 = (4 * red 0 + 1 * red 1) / 5; // bit code 010

red 3 = (3 * red 0 + 2 * red 1) / 5; // bit code 011

red 4 = (2 * red 0 + 3 * red 1) / 5; // bit code 100

red 5 = (1 * red 0 + 4 * red 1) / 5; // bit code 101

red 6 = UNORM ? 0.0 : -1.0;

// bit code 110 (0 for UNORM, -1 for SNORM)

red 7 = 1.0;

// bit code 111

}

```

The same calculations are done for green, using the corresponding reference colors and bit codes.

#### BC6H

For IVB+, these formats (BC6H\_UF16 and BC6H\_SF16) compresses 3-channel images with high dynamic range (> 8 bits per channel). BC6H supports floating point denorms but there is no support for INF and

NaN, other than with BC6H\_SF16 –INF is supported. The alpha channel is not included, thus alpha is returned at its default value.

The BC6H block is 16 bytes and represents a 4x4 block of texels. The texels are labeled as texel[row][column] where both row and column range from 0 to 3. Texel[0][0] is the upper left texel. BC6H has 14 different modes, the mode that the block is in is contained in the least significant bits (either 2 or 5 bits).

The basic scheme consists of interpolating colors along either one or two lines, with per-texel indices indicating which color along the line is chosen for each texel. If a two-line mode is selected, one of 32 partition sets is indicated which selects which of the two lines each texel is assigned to.

#### **Field Definition**

There are 14 possible modes for a BC6H block, the format of each is indicated in the 14 tables below. The mode is selected by the unique mode bits specified in each table. The first 10 modes use two lines ("TWO"), and the last 4 use one line ("ONE"). The difference between the various two-line and one-line modes is with the precision of the first endpoint and the number of bits used to store delta values for the remaining endpoints. Two modes (9 and 10) specify each endpoint as an original value rather than using the deltas (these are indicated as having no delta values).

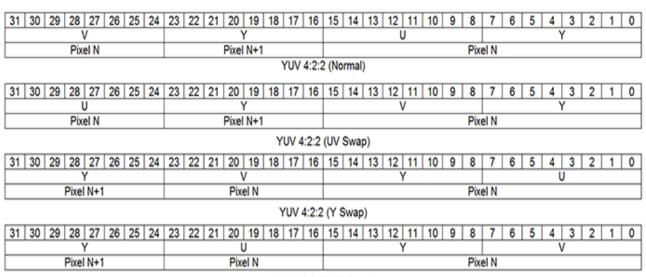

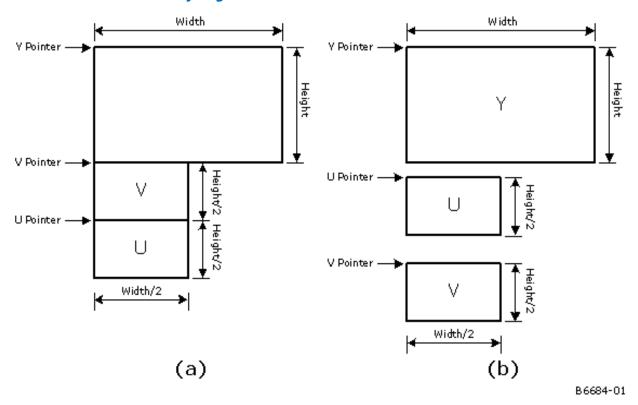

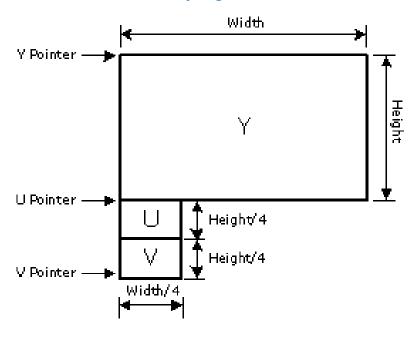

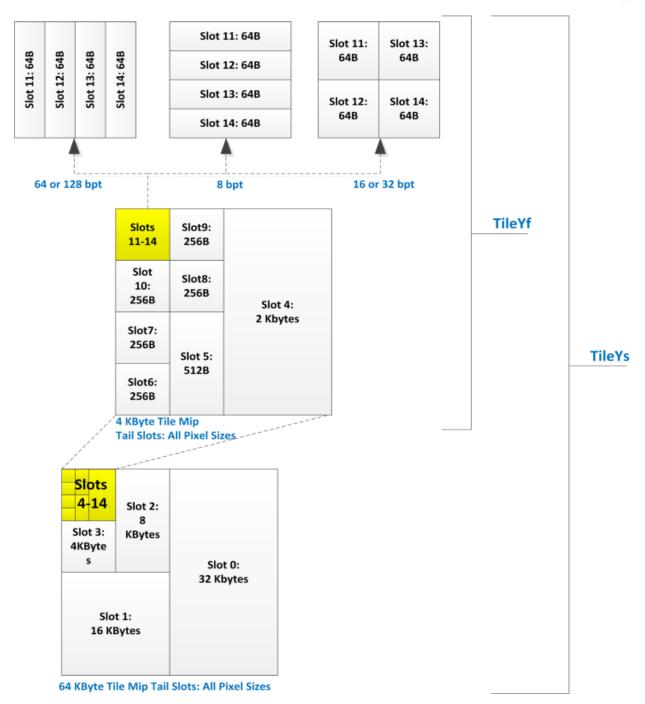

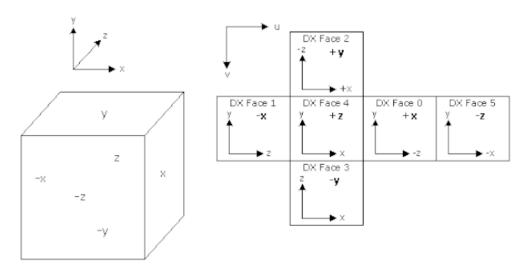

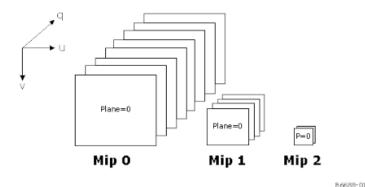

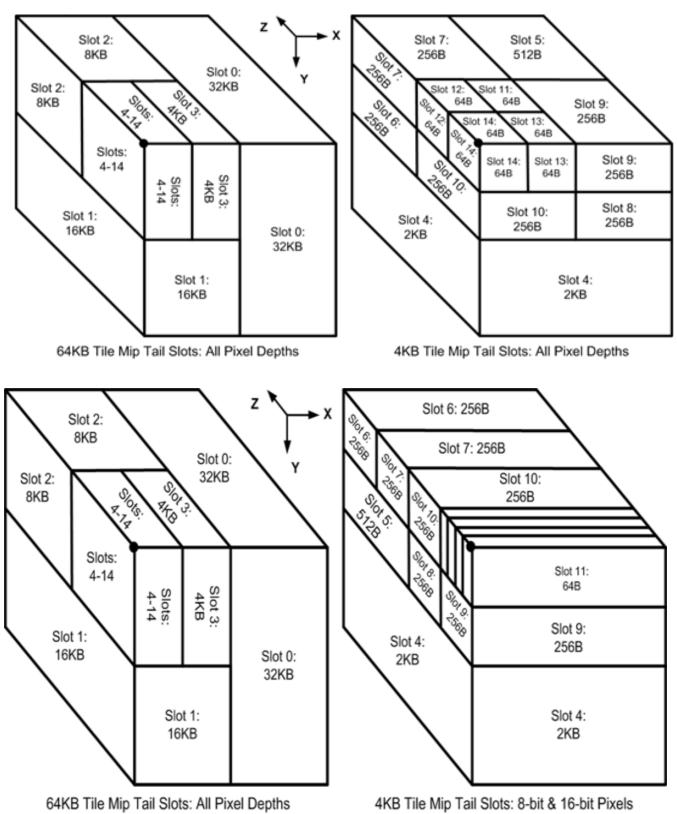

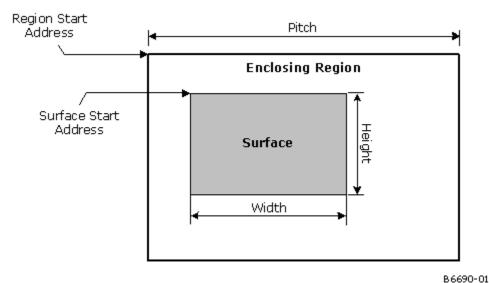

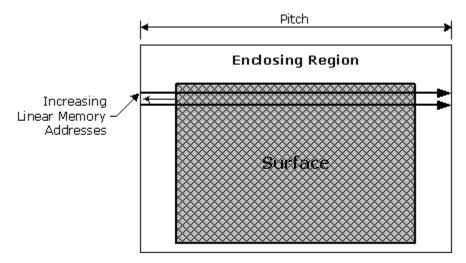

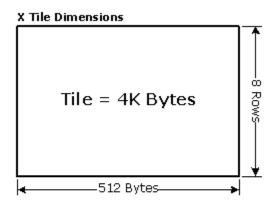

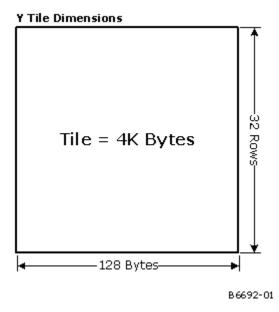

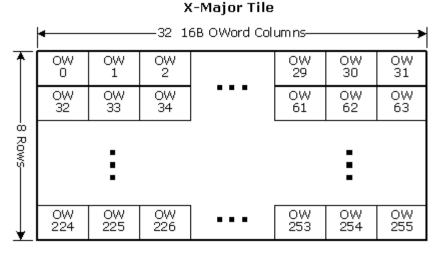

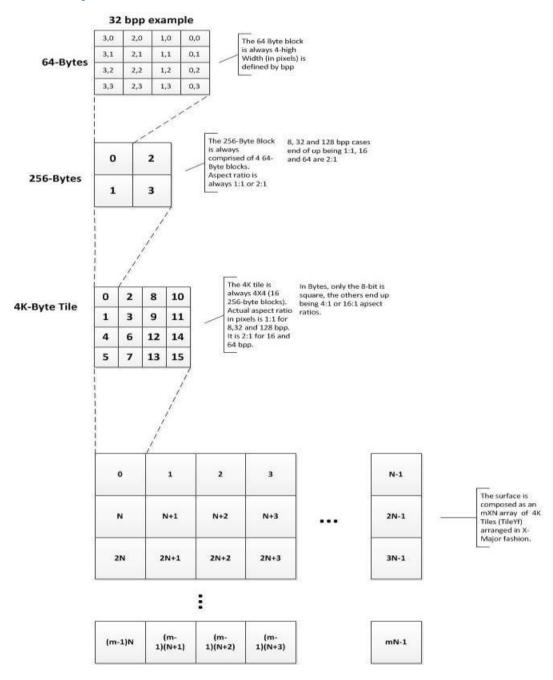

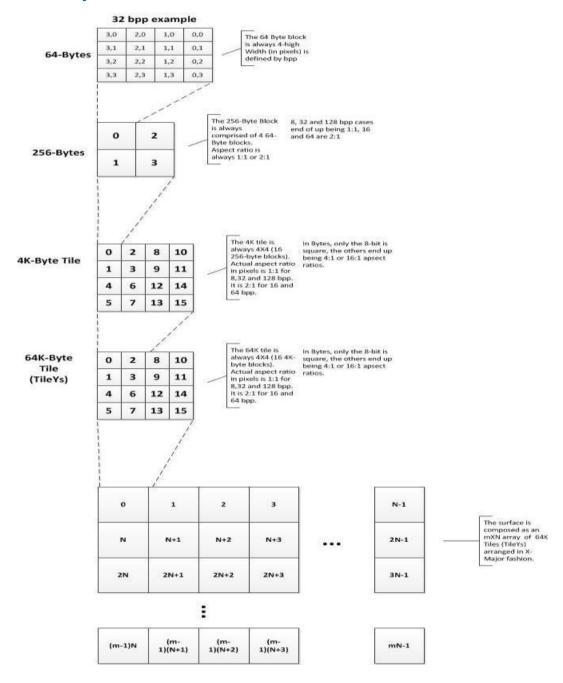

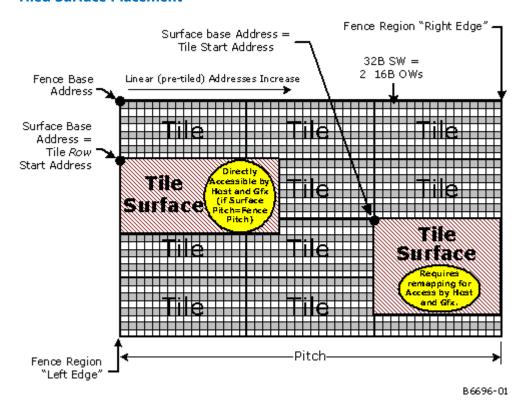

The endpoints values and deltas are indicated in the tables using a two-letter name. The first letter is "r", "g", or "b" indicating the color channel. The second letter is "w", "x", "y", or "z" indicating which of the four endpoints. The first line has endpoints "w" and "x", with "w" being the endpoint that is fully specified (i.e. not as a delta). The second line has endpoints "y" and "z". Modes using ONE mode do not have endpoints "y" and "z" as they have only one line.