# G45: Volume 3: Display Register Intel<sup>®</sup> 965G Express Chipset Family and Intel<sup>®</sup> G35 Express Chipset Graphics Controller

Programmer's Reference Manual (PRM)

January 2009

Revision 2.0a Document Number: 321394-001

Technical queries: ilg@linux.intel.com

www.intellinuxgraphics.org

#### You are free:

to Share — to copy, distribute, display, and perform the work

#### Under the following conditions:

**Attribution**. You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

No Derivative Works. You may not alter, transform, or build upon this work.

You are not obligated to provide Intel with comments or suggestions regarding this document. However, should you provide Intel with comments or suggestions for the modification, correction, improvement, or enhancement of: 9a) this document; or (b) Intel products, which may embody this document, you grant to Intel a non-exclusive, irrevocable, worldwide, royalty-free license, with the right to sublicense Intel's licensees and customers, under Recipient intellectual property rights, to use and disclose such comments and suggestions in any manner Intel chooses and to display, perform, copy, make, have made, use, sell, and otherwise dispose of Intel's and its sublicensee's products embodying such comments and suggestions in any manner and via any media Intel chooses, without reference to the source.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 965 Express Chipset Family and Intel<sup>®</sup> G35 Express Chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

12C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the 12C bus/protocol and was developed by Intel. Implementations of the 12C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2008, Intel Corporation. All rights reserved.

# Contents

| 1 | Introc | luction                                                               | . 11           |

|---|--------|-----------------------------------------------------------------------|----------------|

|   | 1.1    | Notations and Conventions                                             | . 13           |

|   |        | 1.1.1 Reserved Bits and Software Compatibility                        |                |

|   | 1.2    | Terminology                                                           |                |

| 2 | Displa | y Registers                                                           | . 24           |

| _ | 2.1    | Introduction and Register Summary                                     |                |

|   | 2.1    | 2.1.1 Panel Control Register Summary ([DevCL] and [DevCTG] Only)      |                |

|   |        | 2.1.2 Display Pipe and Plane Control Registers                        |                |

|   |        | 2.1.3 Terminology                                                     |                |

|   |        | 2.1.4 Register Protection for Panel Protection                        |                |

|   | 2.2    | Display Mode Set Sequence.                                            |                |

|   | 2.2    | 2.2.1 Pipe register double-buffering                                  |                |

|   |        | 2.2.2 Mode Switch Programming Sequences                               |                |

|   | 2.3    | Display Power Down/Up Register Access Sequence                        |                |

|   | 2.5    | 2.3.1 Power Up/Down for CRT-like Display Devices                      |                |

|   |        | 2.3.1 Power Up/Down for Integrated and External Panel Scaler Driven D |                |

|   |        |                                                                       |                |

|   | 2.4    | GMBUS and I/O Control Registers (05000h–05FFFh)                       | 32             |

|   |        | 2.4.1 GPIO Pin Usage (By Functions)                                   |                |

|   |        | 2.4.2 GPIO Pin Usage (By Device)                                      |                |

|   |        | 2.4.3 GPIO Pin Glue Logic                                             |                |

|   |        | 2.4.4 GPIO Control Registers                                          |                |

|   |        | 2.4.5 GMBUS Controller Programming Interface                          |                |

|   |        | 2.4.6 GMBUSO—GMBUS Clock/Port Select                                  |                |

|   |        | 2.4.7 GMBUS1—GMBUS Command/Status                                     |                |

|   |        | 2.4.8 GMBUS2—GMBUS Status Register                                    |                |

|   |        | 2.4.9 GMBUS3—GMBUS Data Buffer                                        |                |

|   |        | 2.4.10 GMBUS4—GMBUS Interrupt Mask                                    |                |

|   |        | 2.4.11 GMBUS5—2 Byte Index Register                                   |                |

|   | 2.5    | Display Clock Control Registers (06000h–06FFFh)                       |                |

|   |        | 2.5.1 VGA0–VGA 0 Divisor Register (100.8 MHz dot clk, 25.175 MHz pix  | el rate) 47    |

|   |        | 2.5.2 VGA1 — VGA 1 Divisor Register (113.280 MHz dot clk, 28.322 MHz  | pixel rate) 47 |

|   |        | 2.5.3 VGA_PD—VGA Post Divisor Values                                  | . 48           |

|   |        | 2.5.4 DPLLA_CTRL—DPLL A Control Register                              | . 49           |

|   |        | 2.5.5 DPLLB_CTRL—DPLL B Control Registers                             | 52             |

|   |        | 2.5.6 FPA0—DPLL A Divisor Register 0                                  |                |

|   |        | 2.5.7 FPA1—DPLL A Divisor Register 1                                  |                |

|   |        | 2.5.8 FPB0—DPLL B Divisor Register                                    |                |

|   |        | 2.5.9 FPB1—DPLL B Divisor Register 1                                  |                |

|   |        | 2.5.10 DPLL_TEST—DPLLA and DPLLB Test Register                        |                |

|   |        | 2.5.11 DEUC—Dynamic EU Control ([DevCL] only)                         |                |

|   |        | 2.5.12 DEUC—Dynamic EU Control (not for EDS publication ([DevCL] onl  |                |

|   | 2.6    | Display Palette Registers (0A000h-AFFFh)                              |                |

|   |        | 2.6.1 DPALETTE_A—Pipe A Display Palette                               |                |

|   |        | 2.6.2 DPALETTE_B—Pipe B Display Palette                               | 68             |

|   | 2.7    | Display Pipeline / Port Registers (60000h-6FFFh)                      | 69             |

|   |        | 2.7.1 Display Pipeline A                                              | . 69           |

|         | 2.7.2          | Display Pipeline B                                                                    | . 76 |

|---------|----------------|---------------------------------------------------------------------------------------|------|

| 2.8     | Display        | Port Control                                                                          | . 79 |

|         | 2.8.1          | ADPA—Analog Display Port Register                                                     | . 79 |

|         | 2.8.2          | LVDS—Digital Display Port Control ([DevCL and DevCTG])                                |      |

| 2.9     | Panel Re       | egisters                                                                              |      |

|         | 2.9.1          | Panel Power Sequencing Registers ([DevBW], [DevCL], [DevCTG])                         |      |

|         | 2.9.2          | Panel Fitting Registers                                                               |      |

|         | 2.9.3          | Backlight Control and Modulation Histogram Registers ([DevCL])                        | . 93 |

| 2.10    | Display        | and Cursor Registers (70000h-7FFFh)                                                   | . 98 |

|         | 2.10.1         | Display Pipeline A                                                                    |      |

|         | 2.10.2         | Cursor A Plane Control Registers                                                      |      |

|         | 2.10.3         | Cursor B Plane Control Registers                                                      | 125  |

|         | 2.10.4         | Display Pipeline B                                                                    |      |

|         | 2.10.5         | Display A (Primary) Plane Control                                                     |      |

|         | 2.10.6         | Display B (Second Primary or Sprite) Control                                          | 154  |

|         | 2.10.7         | Video BIOS Registers (71400h- 714FFh)                                                 |      |

|         | 2.10.8         | Display C (Sprite or Second Overlay) Control                                          |      |

|         | 2.10.9         | Display C Color Adjustment                                                            |      |

|         |                | Video Sprite A/B Control [DevCTG]                                                     |      |

|         | 2.10.11        | Performance Counters                                                                  | 199  |

| Overlay | / Reaiste      | rs                                                                                    | 202  |

|         |                |                                                                                       |      |

| 3.1     |                | tion and Register Summary                                                             |      |

|         | 3.1.1          | Terminology                                                                           |      |

|         | 3.1.2          | Register Protection in a Trusted Environment                                          |      |

| 3.2     | 5              | Register Definition                                                                   |      |

|         | 3.2.1          | Introduction to Overlay Registers                                                     |      |

|         | 3.2.2          | OVADD—Overlay Register Update Address Register                                        |      |

|         | 3.2.3          | OTEST—Overlay Test Register                                                           |      |

|         | 3.2.4          | DOVSTA—Display/Overlay Status Register                                                |      |

|         | 3.2.5          | DOVSTAEX—Display/Overlay Extended Status Register                                     |      |

|         | 3.2.6          | OGAMC[5:0]—Overlay Dedicated Gamma Correction Registers                               |      |

|         | 3.2.7          | Overlay Sync Lock Registers.                                                          |      |

|         | 3.2.8<br>3.2.9 | Overlay Memory Image Offset Registers                                                 |      |

|         | 3.2.9          | Overlay Initial Phase Registers<br>Overlay Destination Window Position/Size Registers |      |

|         | 3.2.10         | Overlay Source Size Registers                                                         |      |

|         | 3.2.11         | Overlay Scale Factor Registers                                                        |      |

|         | 3.2.12         | Overlay Color Correction Registers                                                    |      |

|         | 3.2.13         | Overlay Destination Color Key Registers                                               |      |

|         | 3.2.15         | Overlay Source Chroma Key Registers                                                   |      |

|         | 3.2.16         | Overlay Scaling Registers                                                             |      |

|         | 3.2.17         | Overlay Polyphase Filter Coefficient Registers                                        |      |

|         |                |                                                                                       |      |

| IV-Out  |                |                                                                                       |      |

| 4.1     | TV-Out (       | Control Registers [DevCL]                                                             | 255  |

|         | 4.1.1          | TV_CTL—TV-Out Control                                                                 | 255  |

|         | 4.1.2          | TV_DAC—TV DAC Control / Status [DevCL]                                                |      |

| 4.2     | Color Co       | onversion and Control Registers [DevCL]                                               | 260  |

|         | 4.2.1          | TV_CSC_Y—Color Space Convert Y                                                        |      |

|         | 4.2.2          | TV_CSC_Y2—Color Space Convert Y2                                                      |      |

|         | 4.2.3          | TV_CSC_U—Color Space Convert U                                                        |      |

|         | 4.2.4          | TV_CSC_U2—Color Space Convert U2                                                      | 262  |

|         | 4.2.5          | TV_CSC_V—Color Space Convert V                                                        |      |

|       | 4.2.6                                             | TV_CSC_V2—Color Space Convert V2           |  |  |  |

|-------|---------------------------------------------------|--------------------------------------------|--|--|--|

|       | 4.2.7                                             | TV_CLR_KNOBS—Color Knobs                   |  |  |  |

|       | 4.2.8                                             | TV_CLR_LEVEL—Color Level Control           |  |  |  |

| 4.3   | Timing F                                          | Registers                                  |  |  |  |

|       | 4.3.1                                             | TV_H_CTL_1—H Control 1                     |  |  |  |

|       | 4.3.2                                             | TV_H_CTL_2—H Control 2264                  |  |  |  |

|       | 4.3.3                                             | TV_H_CTL_3—H Control 3                     |  |  |  |

|       | 4.3.4                                             | TV_V_CTL_1—V Control 1                     |  |  |  |

|       | 4.3.5                                             | TV_V_CTL_2—V Control 2                     |  |  |  |

|       | 4.3.6                                             | TV_V_CTL_3—V Control 3                     |  |  |  |

|       | 4.3.7                                             | TV_V_CTL_4—V Control 4                     |  |  |  |

|       | 4.3.8                                             | TV_V_CTL_5—V Control 5                     |  |  |  |

|       | 4.3.9                                             | TV_V_CTL_6—V Control 6                     |  |  |  |

|       | 4.3.10                                            | TV_V_CTL_7—V Control 7                     |  |  |  |

| 4.4   |                                                   | ier Control Registers [DevCL]269           |  |  |  |

|       | 4.4.1                                             | TV_SC_CTL_1—SC Control 1                   |  |  |  |

|       | 4.4.2                                             | TV_SC_CTL_2—SC Control 2                   |  |  |  |

|       | 4.4.3                                             | TV_SC_CTL_3—SC Control 3                   |  |  |  |

| 4.5   | Window                                            | Control Registers [DevCL]                  |  |  |  |

|       | 4.5.1                                             | TV_WIN_POS—Window Position Register270     |  |  |  |

|       | 4.5.2                                             | TV_WIN_SIZE—Window Size Register271        |  |  |  |

| 4.6   | Filter Co                                         | ontrol Registers [DevCL]                   |  |  |  |

|       | 4.6.1                                             | TV_FILTER_CTL_1—Filter Control Register 1  |  |  |  |

|       | 4.6.2                                             | TV_FILTER_CTL_2—Filter Control Register 2  |  |  |  |

|       | 4.6.3                                             | TV_FILTER_CTL_3—Filter Control Register 3  |  |  |  |

|       | 4.6.4                                             | SIN_ROM—Sin ROM                            |  |  |  |

| 4.7   | Closed C                                          | Captioning Registers [DevCL]               |  |  |  |

|       | 4.7.1                                             | TV_CC_CTL—CC Control Register [DevCL]274   |  |  |  |

|       | 4.7.2                                             | TV_CC_DATA1—CC Data Register Field 1275    |  |  |  |

|       | 4.7.3                                             | TV_CC_DATA2—CC Data Register Field 2       |  |  |  |

| 4.8   | PAL Wid                                           | e Screen Signaling (WSS) Registers [DevCL] |  |  |  |

|       | 4.8.1                                             | TV_WSS_CTL—WSS Control Register            |  |  |  |

|       | 4.8.2                                             | TV_WSS_DATA—WSS Data Register Field 1      |  |  |  |

| 4.9   | Filter Co                                         | pefficient Registers [DevCL]               |  |  |  |

|       | 4.9.1                                             | TV_H_LUMA—H Filter Luma Coeffs             |  |  |  |

|       | 4.9.2                                             | TV_H_CHROMA—H Filter Chroma Coeffs         |  |  |  |

|       | 4.9.3                                             | TV_V_LUMA—V Filter Luma Coeffs             |  |  |  |

|       | 4.9.4                                             | TV_V_CHROMA—V Filter Chroma Coeffs         |  |  |  |

|       |                                                   |                                            |  |  |  |

| TV-Ou | t Program                                         | nming Guide [DevCL]                        |  |  |  |

| 5.1   | TV-Out I                                          | Register Descriptions279                   |  |  |  |

| 5.2   | TV-Out I                                          | Programming                                |  |  |  |

|       | 5.2.1                                             | Television Standards                       |  |  |  |

|       | 5.2.2                                             | Underscanning and Pixel Aspect Ratios      |  |  |  |

|       | 5.2.3                                             | Programming Filter Coefficients            |  |  |  |

|       | 5.2.4                                             | Setting the Mode                           |  |  |  |

|       | 5.2.5                                             | Detection and Determination of the Load    |  |  |  |

| 5.3   |                                                   | nnector and Dongle Design                  |  |  |  |

|       |                                                   |                                            |  |  |  |

| VGA a | VGA and Extended VGA Registers (00000h–00FFFh)295 |                                            |  |  |  |

| 6.1   | General                                           | Control and Status Registers               |  |  |  |

|       | 6.1.1                                             | ST00—Input Status 0                        |  |  |  |

|       | 6.1.2                                             | ST01—Input Status 1                        |  |  |  |

|       |                                                   | · · · · · · · · · · · · · · · · · · ·      |  |  |  |

|     | 6.1.3     | FCR—Feature Control                         |       |

|-----|-----------|---------------------------------------------|-------|

|     | 6.1.4     | MSR—Miscellaneous Output                    | . 301 |

| 6.2 | Sequence  | cer Registers                               | . 303 |

|     | 6.2.1     | SRX—Sequencer Index                         | . 303 |

|     | 6.2.2     | SR00—Sequencer Reset                        |       |

|     | 6.2.3     | SR01—Clocking Mode                          | . 304 |

|     | 6.2.4     | SR02—Plane/Map Mask                         | . 305 |

|     | 6.2.5     | SR03—Character Font                         | . 306 |

|     | 6.2.6     | SR04—Memory Mode Register                   |       |

|     | 6.2.7     | SR07—Horizontal Character Counter Reset     | . 308 |

| 6.3 | Graphics  | s Controller Registers                      | . 308 |

|     | 6.3.1     | GRX—GRX Graphics Controller Index Register  | . 308 |

|     | 6.3.2     | GR00—Set/Reset Register                     |       |

|     | 6.3.3     | GR01—Enable Set/Reset Register              |       |

|     | 6.3.4     | GR02—Color Compare Register                 | .310  |

|     | 6.3.5     | GR03—Data Rotate Register                   |       |

|     | 6.3.6     | GR04—Read Plane Select Register             | .311  |

|     | 6.3.7     | GR05—Graphics Mode Register                 | .311  |

|     | 6.3.8     | GR06—Miscellaneous Register                 | .314  |

|     | 6.3.9     | GR07—Color Don't Care Register              | .315  |

|     | 6.3.10    | GR08—Bit Mask Register                      | .315  |

|     | 6.3.11    | GR10—Address Mapping                        | .316  |

|     | 6.3.12    | GR11—Page Selector                          | .318  |

|     | 6.3.13    | GR18—Software Flags                         | . 318 |

| 6.4 | Attribute | e Controller Registers                      | .318  |

|     | 6.4.1     | ARX—Attribute Controller Index Register     | .319  |

|     | 6.4.2     | AR[00:0F]—Palette Registers [0:F]           | . 320 |

|     | 6.4.3     | AR10—Mode Control Register                  |       |

|     | 6.4.4     | AR11—Overscan Color Register                | . 322 |

|     | 6.4.5     | AR12—Memory Plane Enable Register           |       |

|     | 6.4.6     | AR13—Horizontal Pixel Panning Register      |       |

|     | 6.4.7     | AR14—Color Select Register                  |       |

| 6.5 | VGA Col   | or Palette Registers                        | .324  |

|     | 6.5.1     | DACMASK—Pixel Data Mask Register            |       |

|     | 6.5.2     | DACSTATE—DAC State Register                 |       |

|     | 6.5.3     | DACRX—Palette Read Index Register           |       |

|     | 6.5.4     | DACWX—Palette Write Index Register          |       |

|     | 6.5.5     | DACDATA—Palette Data Register               |       |

| 6.6 | CRT Cor   | ntroller Register                           |       |

|     | 6.6.1     | CRX—CRT Controller Index Register           |       |

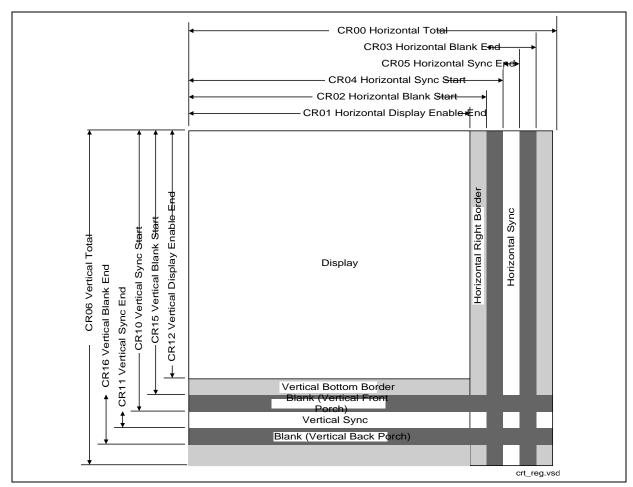

|     | 6.6.2     | CR00—Horizontal Total Register              |       |

|     | 6.6.3     | CR01—Horizontal Display Enable End Register |       |

|     | 6.6.4     | CR02—Horizontal Blanking Start Register     |       |

|     | 6.6.5     | CR03—Horizontal Blanking End Register       |       |

|     | 6.6.6     | CR04—Horizontal Sync Start Register         |       |

|     | 6.6.7     | CR05—Horizontal Sync End Register           |       |

|     | 6.6.8     | CR06—Vertical Total Register                |       |

|     | 6.6.9     | CR07—Overflow Register (Vertical)           |       |

|     | 6.6.10    | CR08—Preset Row Scan Register               |       |

|     | 6.6.11    | CR09—Maximum Scan Line Register             |       |

|     | 6.6.12    | CROA—Text Cursor Start Register             |       |

|     | 6.6.13    | CROB—Text Cursor End Register               |       |

|     | 6.6.14    | CROC—Start Address High Register            | . 338 |

|       | 6.6.15                                | CR0D—Start Address Low Register                                           |  |  |

|-------|---------------------------------------|---------------------------------------------------------------------------|--|--|

|       | 6.6.16                                | CROE—Text Cursor Location High Register                                   |  |  |

|       | 6.6.17                                | CROF—Text Cursor Location Low Register                                    |  |  |

|       | 6.6.18                                | CR10—Vertical Sync Start Register                                         |  |  |

|       | 6.6.19                                | CR11—Vertical Sync End Register                                           |  |  |

|       | 6.6.20                                | CR12—Vertical Display Enable End Register                                 |  |  |

|       | 6.6.21                                | CR13—Offset Register341                                                   |  |  |

|       | 6.6.22                                | CR14—Underline Location Register                                          |  |  |

|       | 6.6.23                                | CR15—Vertical Blanking Start Register                                     |  |  |

|       | 6.6.24                                | CR16—Vertical Blanking End Register                                       |  |  |

|       | 6.6.25                                | CR17—CRT Mode Control                                                     |  |  |

|       | 6.6.26                                | CR18—Line Compare Register                                                |  |  |

|       | 6.6.27                                | CR22—Memory Read Latch Data Register                                      |  |  |

|       | 6.6.28                                | CR24— Test Register for Toggle State of Attribute Controller Register 348 |  |  |

| AVC B | it-Serial D                           | Decoder                                                                   |  |  |

| 7.1   | Introduc                              | stion                                                                     |  |  |

|       | 7.1.1                                 | Terminologies                                                             |  |  |

|       | 7.1.2                                 | Design Assumptions                                                        |  |  |

|       | 7.1.3                                 | Bit-Serial Decoding (BSD) Unit                                            |  |  |

|       | 7.1.4                                 | Intra Prediction for I Slices                                             |  |  |

| 7.2   | H/W Asy                               | ynchronous Reset                                                          |  |  |

| 7.3   | -                                     | eline Flush                                                               |  |  |

| 7.4   | MMIO Ir                               | nterface                                                                  |  |  |

| 7.5   | Program                               | ming the BSD Unit                                                         |  |  |

|       | 7.5.1                                 | Example Command Sequence for Decoding a Single Video Stream 353           |  |  |

| 7.6   | AVC_BS                                | D Commands                                                                |  |  |

|       | 7.6.1                                 | BSD_IND_OBJ_BASE_ADDR Command                                             |  |  |

|       | 7.6.2                                 | AVC_BSD_STATE Commands                                                    |  |  |

|       | 7.6.3                                 | AVC_BSD_OBJECT Command                                                    |  |  |

| 7.7   | AVC_BS                                | D Output Definitions                                                      |  |  |

|       | 7.7.1                                 | AVC-IT Data Buffer Description                                            |  |  |

|       | 7.7.2                                 | Special Scan order for MB/MB Pair Kernel Processing                       |  |  |

| 7.8   | Error Ha                              | andling and Error Concealment                                             |  |  |

|       | 7.8.1                                 | Design Assumptions415                                                     |  |  |

|       | 7.8.2                                 | Error Concealment and Recovery Strategies415                              |  |  |

|       | 7.8.3                                 | Error Handling416                                                         |  |  |

|       | 7.8.4                                 | Error Handling for Non-Existing Reference Picture418                      |  |  |

| 7.9   |                                       | ent, Multiple Video Stream Decoding Support419                            |  |  |

| 7.10  | Performance and Latency Estimation419 |                                                                           |  |  |

| 7.11  |                                       | lessages                                                                  |  |  |

| 7.12  | Media A                               | pplications with Specific Hardware Support                                |  |  |

|       | 7.12.1                                | AVC – Off-host CABAC/CAVLD Acceleration419                                |  |  |

# Figures

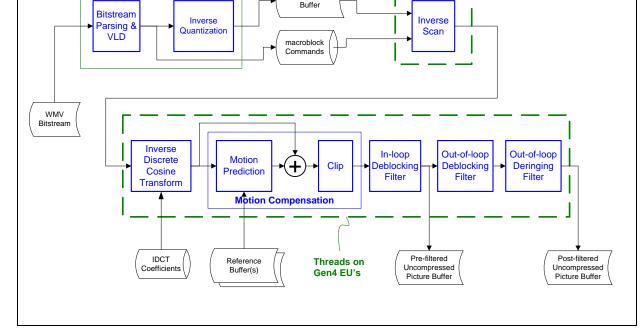

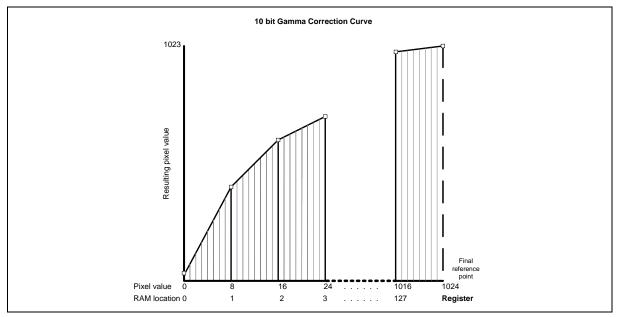

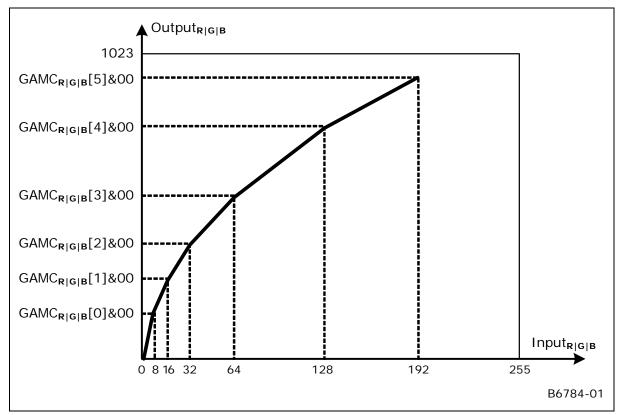

| Figure 2-1. 10-bit Gamma Correction Curve                                            | 67    |

|--------------------------------------------------------------------------------------|-------|

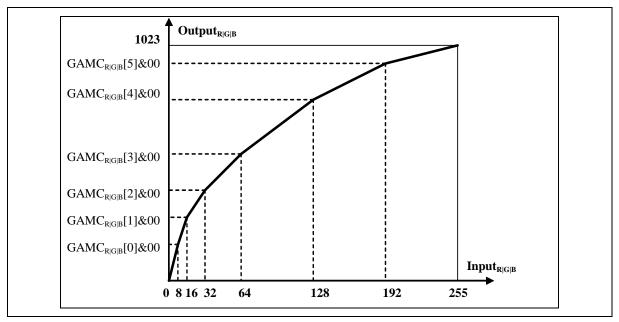

| Figure 2-2. Programming of the Piecewise-linear Estimation of Gamma Correction Curve | . 177 |

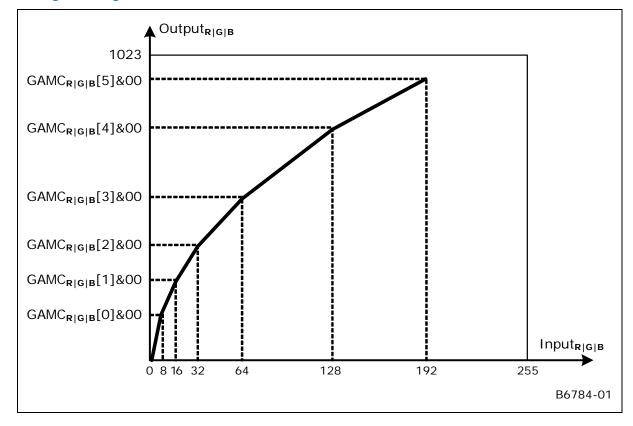

| Figure 2-3. Programming of the Piecewise-linear Estimation of Gamma Correction Curve | . 186 |

| Figure 2-4. Programming of the Piecewise-linear Estimation of Gamma Correction Curve | . 197 |

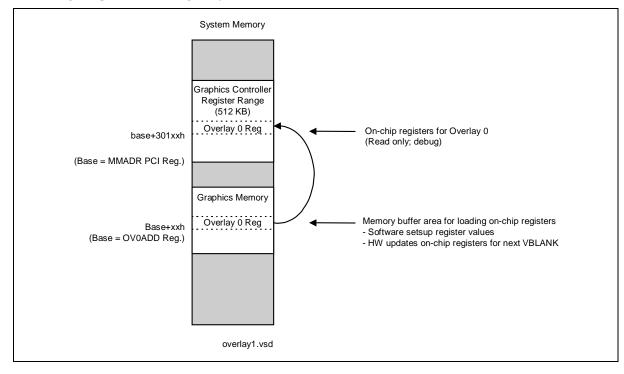

| Figure 3-1. Overlay Register Memory Map                                              | . 205 |

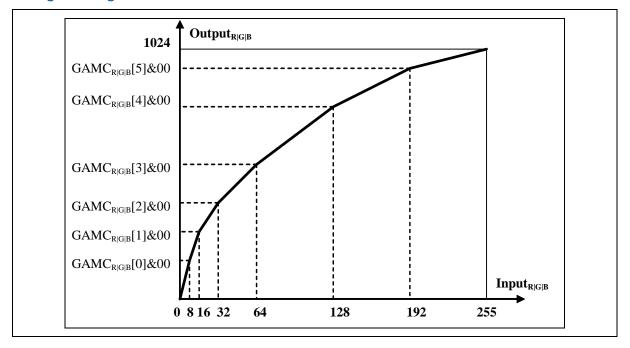

| Figure 3-2. Programming of the Piecewise-linear Estimation of Gamma Correction Curve | . 212 |

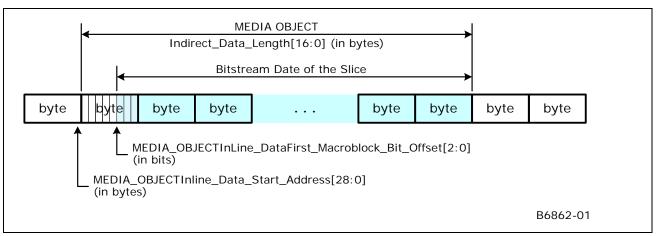

| Figure 7-1. Indirect data buffer for a slice                                         | . 387 |

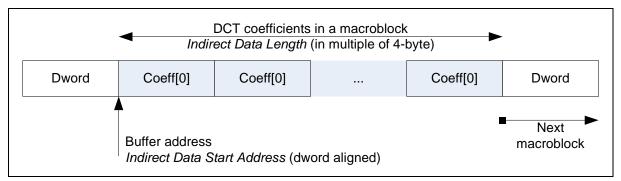

| Figure 7-2. Structure of the Quantized DCT Coefficients Data Buffer                  | . 396 |

| Figure 7-3. AVC decoding pipeline with off-host CABAC/CAVLD acceleration             | . 420 |

# **Tables**

| Table 1-1. | Supported Chipsets 11                                                                       |

|------------|---------------------------------------------------------------------------------------------|

| Table 2-1. | Mode Switch Sequences                                                                       |

| Table 2-2. | Simultaneous Display Capabilities on a Single Display Pipe                                  |

| Table 2-3. | 8-Bit Mode                                                                                  |

|            | 10-bit Mode (Even DWord)68                                                                  |

| Table 2-5. | 10-bit Mode (Odd DWord)68                                                                   |

|            | Cursor Mode Select 120                                                                      |

|            | Cursor Mode Select 126                                                                      |

|            | Overlay Register Categories 205                                                             |

|            | Overlay Memory Offset Registers 214                                                         |

|            | Overlay Buffer Start Address Alignment Restriction 215                                      |

|            | Vertical Initial Phase (for 1:1 scaling, upper left sync) 220                               |

|            | Horizontal Initial Phase (for 1:1 scaling, upper left sync)                                 |

|            | Destination Color Key Value Programming in Each Supported Graphics Mode                     |

|            | Destination Color Key Mask Programming in Each Supported Graphics Mode                      |

|            | RGB Range Expansion Rules 235                                                               |

| Table 6-1. | Analog CRT Display Sync Polarities 302                                                      |

|            | Memory Address Counter Address Bits [15:0] 346                                              |

|            | Frame Buffer Address Decoder 346                                                            |

|            | Structure of a quantized DCT coefficient block 396                                          |

|            | Definition of intra-prediction neighbor availability calculation in MBAFF mode 406          |

|            | Definition of intra-prediction neighbor availability calculation in non-MBAFF mode 407      |

| Table 7-4. | Detailed explanation of intra-prediction neighbor availability calculation in MBAFF mode407 |

|            |                                                                                             |

# **Revision History**

| Document<br>Number | Revision<br>Number | Description                | Revision Date |

|--------------------|--------------------|----------------------------|---------------|

| 24517              | 1.0c               | Initial release. January   |               |

| 321394-001         | 2.0a               | Cantiga release January 20 |               |

§§

# **1** Introduction

This Programmer's Reference Manual (PRM) describes the architectural behavior and programming environment of the Intel<sup>®</sup> 965 Express Chipset family and Intel<sup>®</sup> G35 and G45 Express Chipset GMCH graphics devices (see Table 1-1). The GMCH's Graphics Controller (GC) contains an extensive set of registers and instructions for configuration, 2D, 3D, and Video systems. The PRM describes the register, instruction, and memory interfaces and the device behaviors as controlled and observed through those interfaces. The PRM also describes the registers and instructions and provides detailed bit/field descriptions.

**Note:** The term "GenX" is used throughout the PRM to refer to the family of graphics devices. The devices listed in Table 1-1 are GenX devices.

| Chipset Family Name               | Device Name | Device Tag |

|-----------------------------------|-------------|------------|

| Intel <sup>®</sup> Q965 Chipset   | 82Q965 GMCH | [DevBW]    |

| Intel <sup>®</sup> Q963 Chipset   | 82Q963 GMCH |            |

| Intel <sup>®</sup> G965 Chipset   | 82G965 GMCH |            |

| Intel <sup>®</sup> G35 Chipset    | 82G35 GMCH  | [DevBW-E]  |

| Intel <sup>®</sup> GM965 Chipset  | GM965 GMCH  | [DevCL]    |

| Intel <sup>®</sup> GME965 Chipset | GME965 GMCH |            |

| Intel <sup>®</sup> GM45 Chipset   | GM45 GMCH   | [DevCTG]   |

|                                   | GS45 GMCH   |            |

|                                   | GL40 GMCH   |            |

| Intel <sup>®</sup> G41 Chipset    | GM41 GMCH   | [DevEL]    |

| Intel <sup>®</sup> G45 Chipset    | GM43 GMCH   |            |

| Intel <sup>®</sup> G43 Chipset    | GM54 GMCH   |            |

| Intel <sup>®</sup> G54 Chipset    | Q43 GMCH    |            |

| Intel <sup>®</sup> Q43 Chipset    | Q45 GMCH    |            |

| Intel <sup>®</sup> Q45 Chipset    |             |            |

#### Table 1-1. Supported Chipsets

NOTES:

- 1. Unless otherwise specified, the information in this document applies to all of the devices mentioned in Table 1-1. For Information that does not apply to all devices, the Device Tag is used.

- 2. Throughout the PRM, references to "All" in a project field refters to all devices in Table 1-1.

- 3. Throughout the PRM, references to [DevBW] apply to both [DevBW] and [DevBW-E]. [DevBW-E] is referenced specifically for information that is [DevBW-E] only.

- 4. Stepping info is sometimes appended to the device tag (e.g., [DevBW-C]). Information without any device tagging is applicable to all devices/steppings.

The PRM is intended for hardware, software, and firmware designers who seek to implement or use the graphic functions of the 965 Express Chipset family, G35, and G45 Express Chipset. Familiarity with 2D and 3D graphics programming is assumed.

The Programmer's Reference Manual is organized into four volumes:

#### • PRM, Volume 1a and Volume 1b: Graphics Core

Volume 1 covers the overall Graphics Processing Unit (GPU), without much detail on 3D, Media, or the core subsystem. Topics include the command streamer, context switching, and memory access (including tiling). The Memory Data Formats can also be found in this volume.

The volume also contains a chapter on the Graphics Processing Engine (GPE). The GPE is a collective term for 3D, Media, the subsystem, and the parts of the memory interface that are used by these units. Display, blitter and their memory interfaces are *not* included in the GPE.

#### • PRM, Volume 2; 3D/Media

Volume 2 covers the 3D and Media pipelines in detail. This volume is where details for all of the "fixed functions" are covered, including commands processed by the pipelines, fixed-function state structures, and a definition of the inputs (payloads) and outputs of the threads spawned by these units.

This volume also covers the single Media Fixed Function, VLD. It describes how to initiate generic threads using the thread spawner (TS). It is generic threads which will be used for doing the majority of media functions. Programmable kernels will handle the algorithms for media functions such IDCT, Motion Compensation, and even Motion Estimation (used for encoding MPEG streams).

#### • PRM, Volume 3: Display Registers

Volume 3 describes the control registers for the display. The overlay registers and VGA registers are also covered in this volume.

#### • PRM, Volume 4: Subsystem and Cores

Volume 4 describes the GMCH programmable cores, or EUs, and the "shared functions", which are shared by more than one EU and perform functions such as I/O and complex math functions.

The shared functions consist of the sampler, extended math unit, data port (the interface to memory for 3D and media), Unified Return Buffer (URB), and the Message Gateway which is used by EU threads to signal each other. The EUs use messages to send data to and receive data from the subsystem; the messages are described along with the shared functions, although the generic message send EU instruction is described with the rest of the instructions in the Instruction Set Architecture (ISA) chapters.

This latter part of this volume describes the GMCH core, or EU, and the associated instructions that are used to program it. The instruction descriptions make up what is referred to as an Instruction Set Architecture, or ISA. The ISA describes all of the instructions that the GMCH core can execute, along with the registers that are used to store local data.

*Note:* The chipset PCI Configuration registers are not part of this PRM.

# 1.1 Notations and Conventions

### 1.1.1 Reserved Bits and Software Compatibility

In many register, instruction and memory layout descriptions, certain bits are marked as "Reserved". When bits are marked as reserved, it is essential for compatibility with future devices that software treat these bits as having a future, though unknown, effect. The behavior of reserved bits should be regarded as not only undefined, but unpredictable. Software should follow these guidelines in dealing with reserved bits:

- Do not depend on the states of any reserved bits when testing values of registers that contain such bits. Mask out the reserved bits before testing. Do not depend on the states of any reserved bits when storing to instruction or to a register.

- When loading a register or formatting an instruction, always load the reserved bits with the values indicated in the documentation, if any, or reload them with the values previously read from the register.

# 1.2 Terminology

| Term                           | Abbr. | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3D Pipeline                    | _     | One of the two pipelines supported in the GPE. The 3D pipeline is a set of fixed-function units arranged in a pipelined fashion, which process 3D-related commands by spawning EU threads. Typically this processing includes rendering primitives. See <i>3D Pipeline</i> .                                                                                                                                                                                                                                                                                                                                                                       |

| Adjacency                      |       | One can consider a single line object as existing in a strip<br>of connected lines. The neighboring line objects are called<br>"adjacent objects", with the non-shared endpoints called<br>the "adjacent vertices." The same concept can be applied<br>to a single triangle object, considering it as existing in a<br>mesh of connected triangles. Each triangle shares edges<br>with three other adjacent triangles, each defined by an<br>non-shared adjacent vertex. Knowledge of these adjacent<br>objects/vertices is required by some object processing<br>algorithms (e.g., silhouette edge detection). See <i>3D</i><br><i>Pipeline</i> . |

| Application IP                 | AIP   | Application Instruction Pointer. This is part of the control registers for exception handling for a thread. Upon an exception, hardware moves the current IP into this register and then jumps to SIP.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Architectural<br>Register File | ARF   | A collection of architecturally visible registers for a thread<br>such as address registers, accumulator, flags, notification<br>registers, IP, null, etc. ARF should not be mistaken as just<br>the address registers.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Array of Cores                 | _     | Refers to a group of GenX EUs, which are physically<br>organized in two or more rows. The fact that the EUs are<br>arranged in an array is (to a great extent) transparent to<br>CPU software or EU kernels.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Term                     | Abbr.     | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Binding Table            | _         | Memory-resident list of pointers to surface state blocks (also in memory).                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Binding Table<br>Pointer | BTP       | Pointer to a binding table, specified as an offset from the Surface State Base Address register.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Bypass Mode              | _         | Mode where a given fixed function unit is disabled and forwards data down the pipeline unchanged. Not supported by all FF units.                                                                                                                                                                                                                                                                                                                                                                                                             |

| Byte                     | В         | A numerical data type of 8 bits, B represents a signed byte integer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Child Thread             | _         | A branch-node or a leaf-node thread that is created by<br>another thread. It is a kind of thread associated with the<br>media fixed function pipeline. A child thread is originated<br>from a thread (the parent) executing on an EU and<br>forwarded to the Thread Dispatcher by the TS unit. A child<br>thread may or may not have child threads depending on<br>whether it is a branch-node or a leaf-node thread. All pre-<br>allocated resources such as URB and scratch memory for a<br>child thread are managed by its parent thread. |

| Clip Space               | _         | A 4-dimensional coordinate system within which a clipping<br>frustum is defined. Object positions are projected from<br>Clip Space to NDC space via "perspective divide" by the W<br>coordinate, and then viewport mapped into Screen Space                                                                                                                                                                                                                                                                                                  |

| Clipper                  | _         | 3D fixed function unit that removes invisible portions of<br>the drawing sequence by discarding (culling) primitives or<br>by "replacing" primitives with one or more primitives that<br>replicate only the visible portion of the original primitive.                                                                                                                                                                                                                                                                                       |

| Color Calculator         | сс        | Part of the Data Port shared function, the color calculator performs fixed-function pixel operations (e.g., blending) prior to writing a result pixel into the render cache.                                                                                                                                                                                                                                                                                                                                                                 |

| Command                  | _         | Directive fetched from a ring buffer in memory by the<br>Command Streamer and routed down a pipeline. Should<br>not be confused with instructions which are fetched by the<br>instruction cache subsystem and executed on an EU.                                                                                                                                                                                                                                                                                                             |

| Command<br>Streamer      | CS or CSI | Functional unit of the Graphics Processing Engine that fetches commands, parses them and routes them to the appropriate pipeline.                                                                                                                                                                                                                                                                                                                                                                                                            |

| Constant URB<br>Entry    | CURBE     | A UE that contains "constant" data for use by various stages of the pipeline.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Control Register         | CR        | The read-write registers are used for thread mode control and exception handling for a thread.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Degenerate Object        | _         | Object that is invisible due to coincident vertices or because does not intersect any sample points (usually due to being tiny or a very thin sliver).                                                                                                                                                                                                                                                                                                                                                                                       |

| Destination              | —         | Describes an output or write operand.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Destination Size         | -         | The number of data elements in the destination of a GenX SIMD instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Term                         | Abbr.     | Definition                                                                                                                                                                                                                                                                                 |

|------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Destination Width            | —         | The size of each of (possibly) many elements of the destination of a GenX SIMD instruction.                                                                                                                                                                                                |

| Double Quad word<br>(DQword) | DQ        | A fundamental data type, DQ represents 16 bytes.                                                                                                                                                                                                                                           |

| Double word<br>(DWord)       | D or DW   | A fundamental data type, D or DW represents 4 bytes.                                                                                                                                                                                                                                       |

| Drawing Rectangle            |           | A screen-space rectangle within which 3D primitives are rendered. An objects screen-space positions are relative to the Drawing Rectangle origin. See <i>Strips and Fans</i> .                                                                                                             |

| End of Block                 | EOB       | A 1-bit flag in the non-zero DCT coefficient data structure indicating the end of an 8x8 block in a DCT coefficient data buffer.                                                                                                                                                           |

| End Of Thread                | EOT       | A message sideband signal on the Output message bus<br>signifying that the message requester thread is<br>terminated. A thread must have at least one SEND<br>instruction with the EOT bit in the message descriptor field<br>set in order to properly terminate.                          |

| Exception                    | _         | Type of (normally rare) interruption to EU execution of a thread's instructions. An exception occurrence causes the EU thread to begin executing the System Routine which is designed to handle exceptions.                                                                                |

| Execution Channel            | _         | GenX EU instructions typically operate on multiple data<br>values in parallel (i.e., in "SIMD" fashion). The data is<br>processed in parallel "execution channels" (e.g., a SIMD8<br>instruction uses 8 execution channels to perform 8<br>operations in parallel).                        |

| Execution Size               | ExecSize  | Execution Size indicates the number of data elements<br>processed by a GENX SIMD instruction. It is one of the<br>GENX instruction fields and can be changed per<br>instruction.                                                                                                           |

| Execution Unit               | EU        | Execution Unit. An EU is a multi-threaded processor within<br>the GENX multi-processor system. Each EU is a fully-<br>capable processor containing instruction fetch and decode,<br>register files, source operand swizzle and SIMD ALU, etc.<br>An EU is also referred to as a GENX Core. |

| Execution Unit<br>Identifier | EUID      | The 4-bit field within a thread state register (SR0) that identifies the row and column location of the EU a thread is located. A thread can be uniquely identified by the EUID and TID.                                                                                                   |

| Execution Width              | ExecWidth | The width of each of several data elements that may be processed by a single GenX SIMD instruction.                                                                                                                                                                                        |

| Extended Math Unit           | EM        | A Shared Function that performs more complex math operations on behalf of several EUs.                                                                                                                                                                                                     |

| FF Unit                      | _         | A Fixed-Function Unit is the hardware component of a 3D<br>Pipeline Stage. A FF Unit typically has a unique FF ID<br>associated with it.                                                                                                                                                   |

| Term                            | Abbr.      | Definition                                                                                                                                                                                                                                                                                                                                        |  |

|---------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Fixed Function                  | FF         | Function of the pipeline that is performed by dedicated (vs. programmable) hardware.                                                                                                                                                                                                                                                              |  |

| Fixed Function ID               | FFID       | Unique identifier for a fixed function unit.                                                                                                                                                                                                                                                                                                      |  |

| FLT_MAX                         | fmax       | The magnitude of the maximum representable single precision floating number according to IEEE-754 standard. FLT_MAX has an exponent of 0xFE and a mantissa of all one's.                                                                                                                                                                          |  |

| Gateway                         | GW         | See Message Gateway.                                                                                                                                                                                                                                                                                                                              |  |

| GENX Core                       | _          | Alternative name for an EU in the GENX multi-processor system.                                                                                                                                                                                                                                                                                    |  |

| General Register<br>File        | GRF        | Large read/write register file shared by all the EUs for<br>operand sources and destinations. This is the most<br>commonly used read-write register space organized as an<br>array of 256-bit registers for a thread.                                                                                                                             |  |

| General State Base<br>Address   | _          | The Graphics Address of a block of memory-resident "state<br>data", which includes state blocks, scratch space, constant<br>buffers and kernel programs. The contents of this<br>memory block are referenced via offsets from the contents<br>of the General State Base Address register. See <i>Graphics</i><br><i>Processing Engine</i> .       |  |

| Geometry Shader                 | GS         | Fixed-function unit between the vertex shader and the clipper that (if enabled) dispatches "geometry shader" threads on its input primitives. Application-supplied geometry shaders normally expand each input primitive into several output primitives in order to perform 3D modeling algorithms such as fur/fins. See <i>Geometry Shader</i> . |  |

| Graphics Address                | _          | The GPE virtual address of some memory-resident object.<br>This virtual address gets mapped by a GTT or PGTT to a<br>physical memory address. Note that many memory-<br>resident objects are referenced not with Graphics<br>Addresses, but instead with offsets from a "base address<br>register".                                               |  |

| Graphics<br>Processing Engine   | GPE        | Collective name for the Subsystem, the 3D and Media pipelines, and the Command Streamer.                                                                                                                                                                                                                                                          |  |

| Guardband                       | GB         | Region that may be clipped against to make sure objects<br>do not exceed the limitations of the renderer's coordinate<br>space.                                                                                                                                                                                                                   |  |

| Horizontal Stride               | HorzStride | The distance in element-sized units between adjacent elements of a GenX region-based GRF access.                                                                                                                                                                                                                                                  |  |

| Immediate floating point vector | VF         | A numerical data type of 32 bits, an immediate floating<br>point vector of type VF contains 4 floating point elements<br>with 8 bits each. The 8-bit floating point element contains<br>a sign field, a 3-bit exponent field and a 4-bit mantissa<br>field. It may be used to specify the type of an immediate<br>operand in an instruction.      |  |

| Term                                 | Abbr. | Definition                                                                                                                                                                                                                                                                                |  |

|--------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Immediate integer<br>vector          | V     | A numerical data type of 32 bits, an immediate integer vector of type V contains 8 signed integer elements with 4-bit each. The 4-bit integer element is in 2's complement form. It may be used to specify the type of an immediate operand in an instruction.                            |  |

| Index Buffer                         | IB    | Buffer in memory containing vertex indices.                                                                                                                                                                                                                                               |  |

| In-loop Deblocking<br>Filter         | ILDB  | The deblocking filter operation in the decoding loop. It is a stage after MC in the video decoding pipe.                                                                                                                                                                                  |  |

| Instance                             | _     | In the context of the VF unit, an instance is one of a sequence of sets of similar primitive data. Each set has identical vertex data but may have unique instance data that differentiates it from other sets in the sequence.                                                           |  |

| Instruction                          | _     | Data in memory directing an EU operation. Instructions<br>are fetched from memory, stored in a cache and executed<br>on one or more GenX cores. Not to be confused with<br>commands which are fetched and parsed by the command<br>streamer and dispatched down the 3D or Media pipeline. |  |

| Instruction Pointer                  | IP    | The address (really an offset) of the instruction currently being fetched by an EU. Each EU has its own IP.                                                                                                                                                                               |  |

| Instruction Set<br>Architecture      | ISA   | The GENX ISA describes the instructions supported by a GENX EU.                                                                                                                                                                                                                           |  |

| Instruction State<br>Cache           | ISC   | On-chip memory that holds recently-used instructions and state variable values.                                                                                                                                                                                                           |  |

| Interface<br>Descriptor              | _     | Media analog of a State Descriptor.                                                                                                                                                                                                                                                       |  |

| Intermediate Z                       | IZ    | Completion of the Z (depth) test at the front end of the Windower/Masker unit when certain conditions are met (no alpha, no pixel-shader computed Z values, etc.)                                                                                                                         |  |

| Inverse Discrete<br>Cosine Transform | IDCT  | The stage in the video decoding pipe between IQ and MC                                                                                                                                                                                                                                    |  |

| Inverse<br>Quantization              | IQ    | A stage in the video decoding pipe between IS and IDCT.                                                                                                                                                                                                                                   |  |

| Inverse Scan                         | IS    | A stage in the video decoding pipe between VLD and IQ. In<br>this stage, a sequence of none-zero DCT coefficients are<br>converted into a block (e.g. an 8x8 block) of coefficients.<br>VFE unit has fixed functions to support IS for both MPEG-2<br>and WMV.                            |  |

| Jitter                               |       | Just-in-time compiler.                                                                                                                                                                                                                                                                    |  |

| Kernel                               | _     | A sequence of GenX instructions that is logically part of the<br>driver or generated by the jitter. Differentiated from a<br>Shader which is an application supplied program that is<br>translated by the jitter to GenX instructions.                                                    |  |

| Least Significant<br>Bit             | LSB   | Least Significant Bit                                                                                                                                                                                                                                                                     |  |

| MathBox                              | _     | See Extended Math Unit                                                                                                                                                                                                                                                                    |  |

| Term                               | Abbr. | Definition                                                                                                                                                                                                           |  |

|------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Media                              | _     | Term for operations such as video decode and encode that are normally performed by the Media pipeline.                                                                                                               |  |

| Media Pipeline                     | _     | Fixed function stages dedicated to media and "generic" processing, sometimes referred to as the generic pipeline.                                                                                                    |  |

| Message                            | _     | Messages are data packages transmitted from a thread to<br>another thread, another shared function or another fixed<br>function. Message passing is the primary communication<br>mechanism of GENX architecture.     |  |

| Message Gateway                    | _     | Shared function that enables thread-to-thread message communication/synchronization used solely by the Media pipeline.                                                                                               |  |

| Message Register<br>File           | MRF   | Write-only registers used by EUs to assemble messages prior to sending and as the operand of a send instruction.                                                                                                     |  |

| Most Significant Bit               | MSB   | Most Significant Bit                                                                                                                                                                                                 |  |

| Motion<br>Compensation             | MC    | Part of the video decoding pipe.                                                                                                                                                                                     |  |

| Motion Picture<br>Expert Group     | MPEG  | MPEG is the international standard body JTC1/SC29/WG11<br>under ISO/IEC that has defined audio and video<br>compression standards such as MPEG-1, MPEG-2, and<br>MPEG-4, etc.                                        |  |

| Motion Vector Field<br>Selection   | MVFS  | A four-bit field selecting reference fields for the motion vectors of the current macroblock.                                                                                                                        |  |

| Multi Render<br>Targets            | MRT   | Multiple independent surfaces that may be the target of a sequence of 3D or Media commands that use the same surface state.                                                                                          |  |

| Normalized Device<br>Coordinates   | NDC   | Clip Space Coordinates that have been divided by the Clip Space "W" component.                                                                                                                                       |  |