# G45: Volume 1a Graphics Core Intel<sup>®</sup> 965G Express Chipset Family and Intel<sup>®</sup> G35 Express Chipset Graphics Controller

Programmer's Reference Manual (PRM)

January 2009

Revision 2.0a Reference Number: 321391-001

Technical queries: ilg@linux.intel.com www.intellinuxgraphics.org

#### You are free:

to Share — to copy, distribute, display, and perform the work

#### Under the following conditions:

**Attribution**. You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

No Derivative Works. You may not alter, transform, or build upon this work.

You are not obligated to provide Intel with comments or suggestions regarding this document. However, should you provide Intel with comments or suggestions for the modification, correction, improvement, or enhancement of: 9a) this document; or (b) Intel products, which may embody this document, you grant to Intel a non-exclusive, irrevocable, worldwide, royalty-free license, with the right to sublicense Intel's licensees and customers, under Recipient intellectual property rights, to use and disclose such comments and suggestions in any manner Intel chooses and to display, perform, copy, make, have made, use, sell, and otherwise dispose of Intel's and its sublicensee's products embodying such comments and suggestions in any manner and via any media Intel chooses, without reference to the source.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 965 Express Chipset Family and Intel<sup>®</sup> G35 Express Chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

12C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the 12C bus/protocol and was developed by Intel. Implementations of the 12C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2008, Intel Corporation. All rights reserved.

# Contents

| Introd     | uction                                                |

|------------|-------------------------------------------------------|

| 1.1        | Notations and Conventions                             |

|            | 1.1.1 Reserved Bits and Software Compatibility        |

| 1.2        | Terminology                                           |

| Granh      | ics Device Overview                                   |

| •          |                                                       |

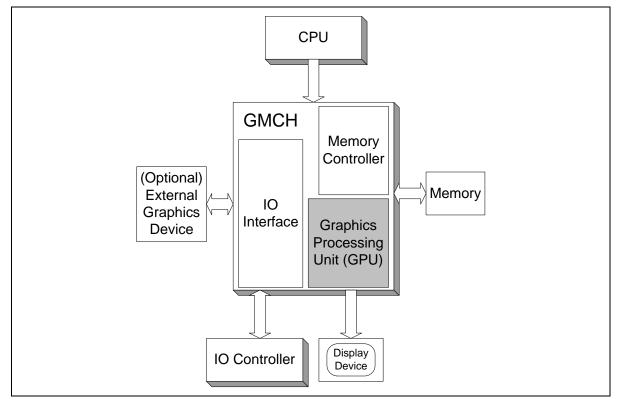

| 2.1        | Graphics Memory Controller Hub (GMCH)                 |

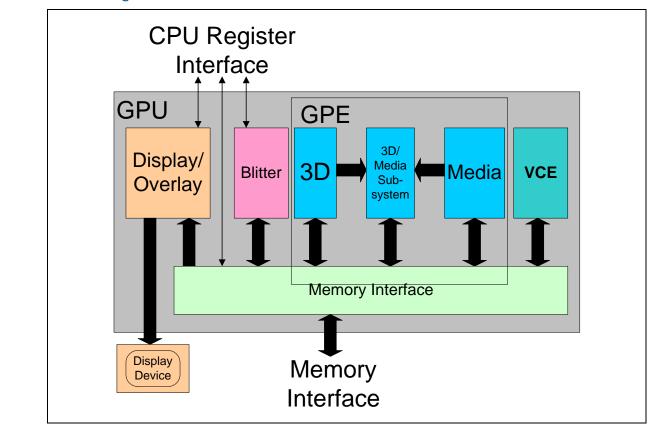

| 2.2        | Graphics Processing Unit (GPU)                        |

| Graph      | ics Processing Engine (GPE)                           |

| 3.1        | Introduction                                          |

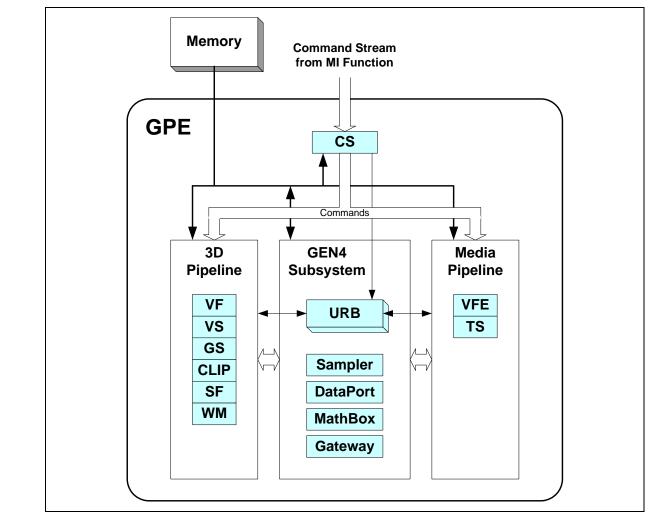

| 3.2        | Overview                                              |

|            | 3.2.1 Block Diagram                                   |

|            | 3.2.2 Command Stream (CS) Unit                        |

|            | 3.2.3 3D Pipeline                                     |

|            | 3.2.4 Media Pipeline                                  |

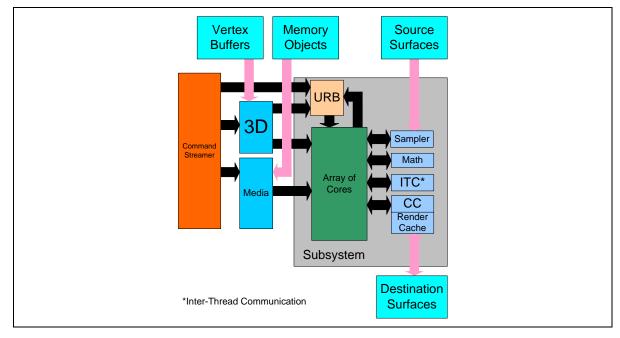

|            | 3.2.5 GENX Subsystem                                  |

|            | 3.2.6 GPE Function IDs                                |

| 3.3        | Pipeline Selection                                    |

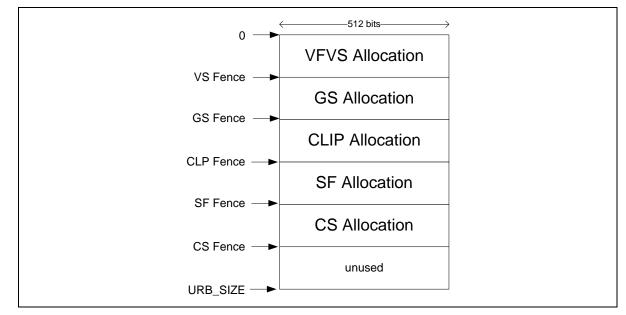

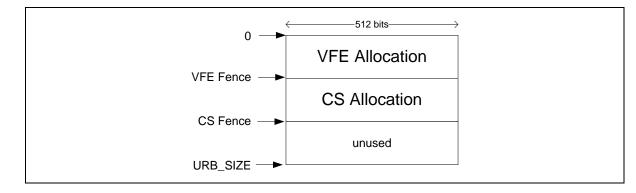

| 3.4        | URB Allocation                                        |

| 0.1        | 3.4.1 URB_FENCE                                       |

| 2 5        | Constant URB Entries (CURBEs)                         |

| 3.5        |                                                       |

|            | 3.5.1 Overview                                        |

|            | 3.5.2 Multiple CURBE Allocation                       |

|            | 3.5.3 CS_URB_STATE                                    |

| <b>.</b> ( | 3.5.4 CONSTANT_BUFFER                                 |

| 3.6        | Memory Access Indirection                             |

|            | 3.6.1 STATE_BASE_ADDRESS                              |

| 3.7        | State Invalidation ([DevCTG+])                        |

|            | 3.7.1 STATE_POINTER_INVALIDATE ([DevCTG+])            |

| 3.8        | Instruction and State Prefetch                        |

|            | 3.8.1 STATE_PREFETCH                                  |

| 3.9        | System Thread Configuration51                         |

|            | 3.9.1 STATE_SIP                                       |

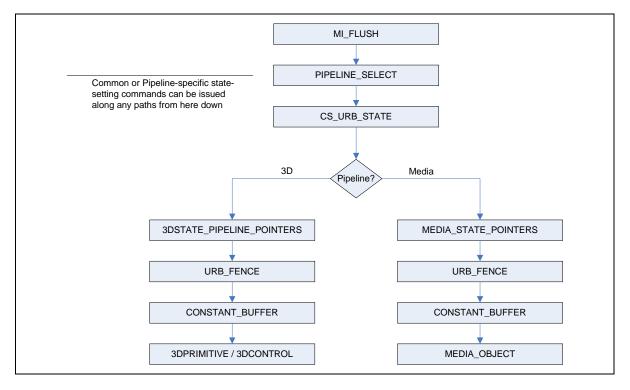

| 3.10       | Command Ordering Rules                                |

|            | 3.10.1 PIPELINE_SELECT                                |

|            | 3.10.2 PIPE_CONTROL                                   |

|            | 3.10.3 URB-Related State-Setting Commands             |

|            | 3.10.4 Common Pipeline State-Setting Commands         |

|            | 3.10.5 3D Pipeline-Specific State-Setting Commands    |

|            | 3.10.6 Media Pipeline-Specific State-Setting Commands |

|            | 3.10.7 URB_FENCE (URB Fencing & Entry Allocation)     |

|            | 3.10.8 CONSTANT_BUFFER (CURBE Load)                   |

|            | 3.10.9 3DPRIMITIVE55                                  |

|            | 3.10.10 MEDIA_OBJECT                                  |

| Graph       | nics Comn      | nand Formats5                                    | 56             |  |

|-------------|----------------|--------------------------------------------------|----------------|--|

| 4.1         | Comma          | and Formats                                      | 56             |  |

|             | 4.1.1          | Memory Interface Commands                        |                |  |

|             | 4.1.2          | 2D Commands                                      |                |  |

|             | 4.1.3          | 3D/Media Commands                                |                |  |

|             | 4.1.4          | Video Codec Commands                             |                |  |

| 4.2         |                | and Map6                                         |                |  |

| т. <b>∠</b> | 4.2.1          | Memory Interface Command Map                     |                |  |

|             | 4.2.2          | 2D Command Map                                   |                |  |

|             | 4.2.2          | 3D/Media Command Map                             |                |  |

| Deele       |                |                                                  |                |  |

| -           |                | ss Maps                                          |                |  |

| 5.1         | •              | cs Register Address Map                          |                |  |

|             | 5.1.1          | Memory and I/O Space Registers                   |                |  |

|             | 5.1.2          | PCI Configuration Space                          |                |  |

|             | 5.1.3          | Graphics Register Memory Address Map             |                |  |

| 5.2         |                | nd Extended VGA Register Map                     |                |  |

|             | 5.2.1          | VGA and Extended VGA I/O and Memory Register Map |                |  |

| 5.3         | Indirect       | t VGA and Extended VGA Register Indices          | <del>9</del> 4 |  |

| Memo        | ory Data F     | Formats                                          | 97             |  |

| 6.1         | Memory         | y Object Overview                                | 76             |  |

| 0.1         | 6.1.1          | Memory Object Types                              |                |  |

| 6.2         |                | el Formats                                       |                |  |

| 0.2         |                | Unsigned Normalized (UNORM)                      |                |  |

|             | 6.2.1<br>6.2.2 |                                                  |                |  |

|             | 6.2.2          | Gamma Conversion (SRGB)                          |                |  |

|             | 6.2.3<br>6.2.4 | Signed Normalized (SNORM)                        |                |  |

|             |                | Unsigned Integer (UINT/USCALED)                  |                |  |

|             | 6.2.5<br>6.2.6 | Signed Integer (SINT/SSCALED)                    |                |  |

| 6.2         |                | Floating Point (FLOAT)                           |                |  |

| 6.3         |                | deo Surface Formats                              |                |  |

|             | 6.3.1          | Surface Format Naming                            |                |  |

|             | 6.3.2          | Intensity Formats                                |                |  |

|             | 6.3.3          | Luminance Formats                                |                |  |

|             | 6.3.4          | P4A4_UNORM                                       |                |  |

|             | 6.3.5          | A4P4_UNORM                                       |                |  |

|             | 6.3.6          | P8A8_UNORM                                       |                |  |

|             | 6.3.7          | A8P8_UNORM                                       |                |  |

|             | 6.3.8<br>6.3.9 | P8_UNORM                                         |                |  |

|             |                | P2_UNORM                                         |                |  |

| 6.4         | •              | essed Surface Formats                            |                |  |

|             | 6.4.1          | FXT Texture Formats                              |                |  |

|             | 6.4.2          | BC Texture Formats                               |                |  |

|             | 6.4.3          | BC4                                              |                |  |

|             | 6.4.4          | BC5                                              |                |  |

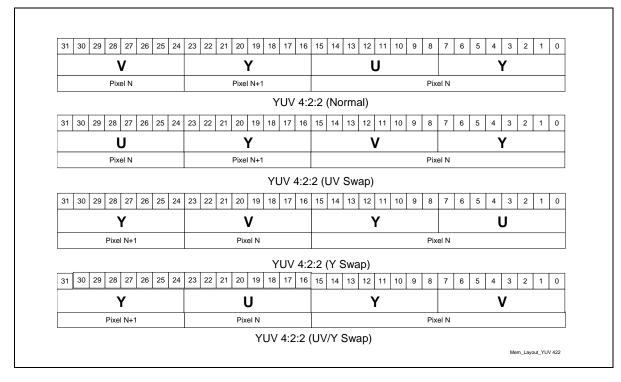

| 6.5         |                | Pixel/Texel Formats                              |                |  |

|             | 6.5.1          | Packed Memory Organization 12                    |                |  |

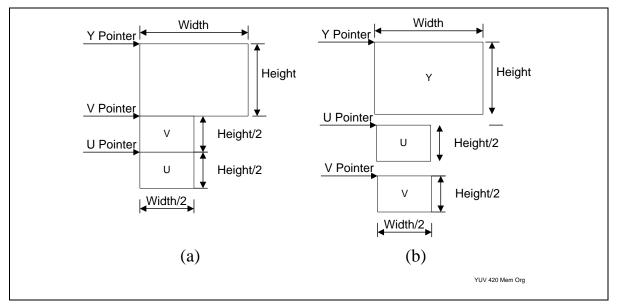

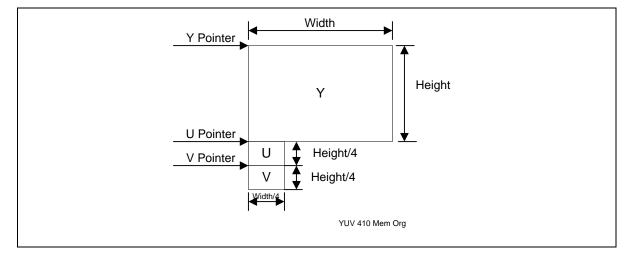

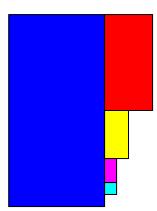

|             | 6.5.2          | Planar Memory Organization 12                    |                |  |

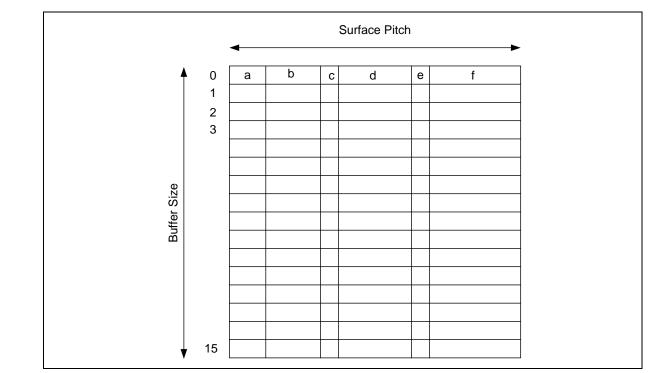

| 6.6         |                | e Memory Organizations12                         |                |  |

| 6.7         | Graphic        | cs Translation Tables 12                         | 28             |  |

| 6.8         | Hardwa         | Hardware Status Page 129                         |                |  |

| 6.9         | Instruc        | tion Ring Buffers                                | 29             |  |

| -           |                | J                                                |                |  |

|        | Instructi                                                                                                                                                                                                                            | on Batch Buffers 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9                                                   |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 6.11   | Display, Overlay, Cursor Surfaces                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |

| 6.12   | 2D Rend                                                                                                                                                                                                                              | ler Surfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9                                                   |

| 6.13   | 2D Mond                                                                                                                                                                                                                              | pchrome Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | С                                                   |

| 6.14   |                                                                                                                                                                                                                                      | - Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                     |

| 6.15   |                                                                                                                                                                                                                                      | <sup>-</sup> Buffer (Destination) Surfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                     |

| 6.16   |                                                                                                                                                                                                                                      | h Buffer Surfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |

|        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |

| 6.17   |                                                                                                                                                                                                                                      | Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

|        | 6.17.1<br>6.17.2                                                                                                                                                                                                                     | Buffers         13'           1D Surfaces         13'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                     |

|        | 6.17.2                                                                                                                                                                                                                               | 2D Surfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |

|        | 6.17.4                                                                                                                                                                                                                               | Cube Surfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                     |

|        | 6.17.5                                                                                                                                                                                                                               | 3D Surfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                     |

| 6.18   |                                                                                                                                                                                                                                      | Padding Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |

| 00     | 6.18.1                                                                                                                                                                                                                               | Sampling Engine Surfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |

|        | 6.18.2                                                                                                                                                                                                                               | Render Target and Media Surfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                     |

| 6.19   | Logical (                                                                                                                                                                                                                            | Context Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |

|        | 6.19.1                                                                                                                                                                                                                               | Overall Context Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

|        | 6.19.2                                                                                                                                                                                                                               | Register/State Context                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                     |

|        | 6.19.3                                                                                                                                                                                                                               | The Probe List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |

|        | 6.19.4                                                                                                                                                                                                                               | Pipelined State Page 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 9                                                   |

|        | 6.19.5                                                                                                                                                                                                                               | Ring Buffer 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9                                                   |

|        | 6.19.6                                                                                                                                                                                                                               | The Per-Process Hardware Status Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | С                                                   |

| Device | 2 Configu                                                                                                                                                                                                                            | uration Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                   |

| 7.1    |                                                                                                                                                                                                                                      | tion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |

| 7.2    | Device 2                                                                                                                                                                                                                             | 2, Function 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                   |

|        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |

|        | 7.2.1                                                                                                                                                                                                                                | VID2 — Vendor Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                     |

|        | 7.2.1<br>7.2.2                                                                                                                                                                                                                       | VID2 — Vendor Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3                                                   |

|        |                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3<br>3                                              |

|        | 7.2.2                                                                                                                                                                                                                                | DID2 — Device Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3<br>3<br>4                                         |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5                                                                                                                                                                                                     | DID2 — Device Identification163PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3<br>3<br>4<br>5<br>6                               |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6                                                                                                                                                                                            | DID2 — Device Identification163PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code165                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3<br>3<br>4<br>5<br>6<br>7                          |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7                                                                                                                                                                                   | DID2 — Device Identification163PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code167CLS — Cache Line Size167                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3<br>3<br>4<br>5<br>6<br>7<br>7                     |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8                                                                                                                                                                          | DID2 — Device Identification163PCICMD2 — PCI Command164PCISTS2 — PCI Status164RID2 — Revision Identification166CC — Class Code167CLS — Cache Line Size167MLT2 — Master Latency Timer168                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3<br>3<br>4<br>5<br>6<br>7<br>8                     |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9                                                                                                                                                                 | DID2 — Device Identification163PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code167CLS — Cache Line Size167MLT2 — Master Latency Timer168HDR2 — Header Type168                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3<br>3<br>4<br>5<br>6<br>7<br>8<br>8                |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10                                                                                                                                                       | DID2 — Device Identification163PCICMD2 — PCI Command164PCISTS2 — PCI Status164RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size165MLT2 — Master Latency Timer168HDR2 — Header Type168BIST — Built In Self Test168                                                                                                                                                                                                                                                                                                                                                                                                                               | 3<br>3<br>4<br>5<br>6<br>7<br>8<br>8<br>8           |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11                                                                                                                                             | DID2 — Device Identification163PCICMD2 — PCI Command164PCISTS2 — PCI Status164RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size165MLT2 — Master Latency Timer168HDR2 — Header Type168BIST — Built In Self Test168GTTMMADR — Graphics Translation Table Range Address169                                                                                                                                                                                                                                                                                                                                                                         | 3<br>3<br>4<br>5<br>6<br>7<br>7<br>8<br>8<br>8<br>9 |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12                                                                                                                                   | DID2 — Device Identification165PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size165MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address166GMADR — Graphics Memory Range Address170                                                                                                                                                                                                                                                                                                                                 | 334567788890                                        |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12<br>7.2.13                                                                                                                         | DID2 — Device Identification165PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size165MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address167GMADR — Graphics Memory Range Address170IOBAR — I/O Base Address170                                                                                                                                                                                                                                                                                                      | 3345677888901                                       |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12<br>7.2.13<br>7.2.14                                                                                                               | DID2 — Device Identification165PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size165MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address176GMADR — Graphics Memory Range Address177SVID2 — Subsystem Vendor Identification177                                                                                                                                                                                                                                                                                       | 33456778889011                                      |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12<br>7.2.13                                                                                                                         | DID2 — Device Identification165PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size165MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address167GMADR — Graphics Memory Range Address170IOBAR — I/O Base Address170                                                                                                                                                                                                                                                                                                      | 334567788890112                                     |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12<br>7.2.13<br>7.2.14<br>7.2.15                                                                                                     | DID2 — Device Identification165PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size165MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address170IOBAR — I/O Base Address177SVID2 — Subsystem Vendor Identification177SID2 — Subsystem Identification177                                                                                                                                                                                                                                                                  | 3345677888901122                                    |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12<br>7.2.13<br>7.2.14<br>7.2.15<br>7.2.16<br>7.2.17<br>7.2.18                                                                       | DID2 — Device Identification165PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size166MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address170IOBAR — I/O Base Address177SVID2 — Subsystem Vendor Identification177SID2 — Subsystem Identification177ROMADR — Video BIOS ROM Base Address177INTRLINE — Interrupt Line173                                                                                                                                                                                               | 334567788890112223                                  |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12<br>7.2.13<br>7.2.14<br>7.2.15<br>7.2.16<br>7.2.17<br>7.2.18<br>7.2.19                                                             | DID2 — Device Identification165PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size166MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address170IOBAR — I/O Base Address177SVID2 — Subsystem Vendor Identification177SID2 — Subsystem Identification177ROMADR — Video BIOS ROM Base Address177INTRLINE — Interrupt Line177INTRPIN — Interrupt Pin175                                                                                                                                                                     | 3345677888901122233                                 |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12<br>7.2.13<br>7.2.14<br>7.2.15<br>7.2.16<br>7.2.17<br>7.2.18<br>7.2.19<br>7.2.20                                                   | DID2 — Device Identification165PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size166MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address170IOBAR — I/O Base Address177SVID2 — Subsystem Vendor Identification177SID2 — Subsystem Identification177ROMADR — Video BIOS ROM Base Address177INTRLINE — Interrupt Line173INTRPIN — Interrupt Pin173MINGNT — Minimum Grant173                                                                                                                                            | 334567788890112223333                               |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12<br>7.2.13<br>7.2.14<br>7.2.15<br>7.2.16<br>7.2.17<br>7.2.18<br>7.2.19<br>7.2.20<br>7.2.21                                         | DID2 — Device Identification165PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size166MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address167IOBAR — I/O Base Address177SVID2 — Subsystem Vendor Identification177SID2 — Subsystem Identification177ROMADR — Video BIOS ROM Base Address177INTRLINE — Interrupt Line177INTRPIN — Interrupt Pin177MINGNT — Minimum Grant177MAXLAT — Maximum Latency174                                                                                                                 | 334567788890112223334                               |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12<br>7.2.13<br>7.2.14<br>7.2.15<br>7.2.16<br>7.2.17<br>7.2.18<br>7.2.19<br>7.2.20<br>7.2.21<br>7.2.21                               | DID2 — Device Identification165PCICMD2 — PCI Command164PCISTS2 — PCI Status165RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size166MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address176GMADR — Graphics Memory Range Address177SVID2 — Subsystem Vendor Identification177SID2 — Subsystem Identification177ROMADR — Video BIOS ROM Base Address177INTRLINE — Interrupt Line173INTRPIN — Interrupt Pin173MINGNT — Minimum Grant174MAXLAT — Maximum Latency174MCAPPTR — Capabilities Pointer (to Mirror of Dev0 CAPID)174                                         | 3345677888901122233344                              |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12<br>7.2.13<br>7.2.14<br>7.2.15<br>7.2.16<br>7.2.17<br>7.2.18<br>7.2.19<br>7.2.20<br>7.2.20<br>7.2.21<br>7.2.22<br>7.2.23           | DID2 — Device Identification166PCICMD2 — PCI Command166PCISTS2 — PCI Status166RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size166MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address177IOBAR — I/O Base Address177SVID2 — Subsystem Vendor Identification177SID2 — Subsystem Identification177ROMADR — Video BIOS ROM Base Address177INTRLINE — Interrupt Line177INTRPIN — Interrupt Pin177MINGNT — Minimum Grant177MAXLAT — Maximum Latency177MCAPPTR — Capabilities Pointer (to Mirror of DevO CAPID)174MCAPID — Mirror of Dev O Capability Identification174 | 334567788890112223333444                            |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12<br>7.2.13<br>7.2.14<br>7.2.15<br>7.2.16<br>7.2.17<br>7.2.18<br>7.2.19<br>7.2.20<br>7.2.21<br>7.2.20<br>7.2.21<br>7.2.23<br>7.2.24 | DID2 — Device Identification165PCICMD2 — PCI Command164PCISTS2 — PCI Status166RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size166MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address176GMADR — Graphics Memory Range Address177IOBAR — I/O Base Address177SVID2 — Subsystem Vendor Identification177SID2 — Subsystem Identification177INTRLINE — Interrupt Line177INTRLINE — Interrupt Pin177MINGNT — Minimum Grant177MAXLAT — Maximum Latency177MCAPPTR — Capabilities Pointer (to Mirror of DevO CAPID)177MGGC — Mirror of DevO GMCH Graphics Control175      | 334567788890112223334445                            |

|        | 7.2.2<br>7.2.3<br>7.2.4<br>7.2.5<br>7.2.6<br>7.2.7<br>7.2.8<br>7.2.9<br>7.2.10<br>7.2.11<br>7.2.12<br>7.2.13<br>7.2.14<br>7.2.15<br>7.2.16<br>7.2.17<br>7.2.18<br>7.2.19<br>7.2.20<br>7.2.20<br>7.2.21<br>7.2.22<br>7.2.23           | DID2 — Device Identification166PCICMD2 — PCI Command166PCISTS2 — PCI Status166RID2 — Revision Identification166CC — Class Code165CLS — Cache Line Size166MLT2 — Master Latency Timer166HDR2 — Header Type166BIST — Built In Self Test166GTTMMADR — Graphics Translation Table Range Address177IOBAR — I/O Base Address177SVID2 — Subsystem Vendor Identification177SID2 — Subsystem Identification177ROMADR — Video BIOS ROM Base Address177INTRLINE — Interrupt Line177INTRPIN — Interrupt Pin177MINGNT — Minimum Grant177MAXLAT — Maximum Latency177MCAPPTR — Capabilities Pointer (to Mirror of DevO CAPID)174MCAPID — Mirror of Dev O Capability Identification174 | 3345677888901122233344456                           |

|     | 7.2.27         | BSM — Base of Stolen Memory 176                                                    |

|-----|----------------|------------------------------------------------------------------------------------|

|     | 7.2.28         | HSRW — Hardware Scratch Read Write                                                 |

|     | 7.2.29         | MSAC — Multi Size Aperture Control 177                                             |

|     | 7.2.30         | SCWBFC — Secondary CWB Flush Control ([DevBW] Only) 178                            |

|     | 7.2.31         | CAPL — Capabilities List Control                                                   |

|     | 7.2.32         | MSI_CAPID — Message Signaled Interrupts Capability ID 179                          |

|     | 7.2.33         | MC — Message Control                                                               |

|     | 7.2.34         | MA — Message Address                                                               |

|     | 7.2.35         | MD — Message Data                                                                  |

|     | 7.2.35         | GDRST — Graphics Device Reset                                                      |

|     | 7.2.30         | GMBUSFREQ — GMBUS frequency binary encoding                                        |

|     | 7.2.37         |                                                                                    |

|     |                | PMCAPID — Power Management Capabilities ID                                         |

|     | 7.2.39         | PMCAP — Power Management Capabilities                                              |

|     | 7.2.40         | PMCS — Power Management Control/Status                                             |

|     | 7.2.41         | SWSMI — Software SMI                                                               |

|     | 7.2.42         | ASLE — System Display Event Register 185                                           |

|     | 7.2.43         | SWSCI — Software SCI                                                               |

|     | 7.2.44         | LBB — Legacy Backlight Brightness ([DevCL] Only) 187                               |

|     | 7.2.45         | MID2 — Manufacturing ID 188                                                        |

|     | 7.2.46         | ASLS — ASL Storage 188                                                             |

| 7.3 | Device 2       | 9, Function 1                                                                      |

|     | 7.3.1          | VID2 — Vendor Identification 190                                                   |

|     | 7.3.2          | DID2 — Device Identification                                                       |

|     | 7.3.3          | PCICMD2 — PCI Command                                                              |

|     | 7.3.4          | PCISTS2 — PCI Status                                                               |

|     | 7.3.5          | RID2 — Revision Identification                                                     |

|     | 7.3.6          | CC — Class Code                                                                    |

|     | 7.3.7          | CLS — Cache Line Size                                                              |

|     | 7.3.8          | MLT2 — Master Latency Timer                                                        |

|     | 7.3.9          | HDR2 — Header Type                                                                 |

|     | 7.3.9          | BIST — Built In Self Test                                                          |

|     |                |                                                                                    |

|     | 7.3.11         | MMADR — Memory Mapped Range Address                                                |

|     | 7.3.12         | SVID2 — Subsystem Vendor Identification                                            |

|     | 7.3.13         | SID2 — Subsystem Identification                                                    |

|     | 7.3.14         | ROMADR — Video BIOS ROM Base Address 197                                           |

|     | 7.3.15         | CAPPOINT — Capabilities Pointer                                                    |

|     | 7.3.16         | MINGNT — Minimum Grant 198                                                         |

|     | 7.3.17         | MAXLAT — Maximum Latency 198                                                       |

|     | 7.3.18         | MCAPPTR — Capabilities Pointer (to Mirror of DevO CAPID) 198                       |

|     | 7.3.19         | MCAPID — Mirror of Dev 0 Capability Identification                                 |

|     | 7.3.20         | MGGC — Mirror of Dev0 GMCH Graphics Control 199                                    |

|     | 7.3.21         | MDEVENdev0F0 — Mirror of Dev0 DEVEN 201                                            |

|     | 7.3.22         | SSRW — Software Scratch Read Write 201                                             |

|     |                | Produtore 202                                                                      |

|     | -              | ce Registers 203                                                                   |

| 8.1 | Introduc       | tion                                                                               |

| 8.2 | Virtual M      | lemory Control                                                                     |

|     | 8.2.1          | Global Virtual Memory                                                              |

|     | 8.2.2          | PGTBL_ER—Page Table Error Register <i>(Debug)</i> [Per-Process GTT enabled on CTG] |

|     | 0.2.2          |                                                                                    |

|     | 8.2.3          | Single-Level (Flat) Per-Process Virtual Memory                                     |

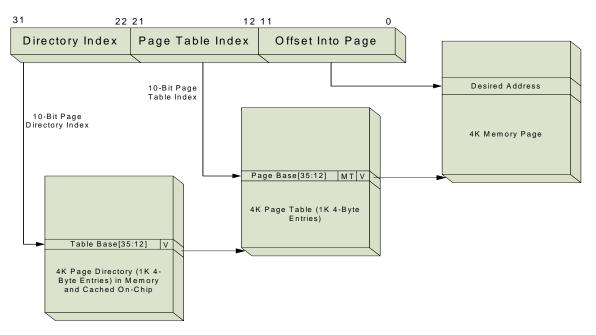

|     | 8.2.4          | Two-Level Per-Process Virtual Memory ([DevCTG] Only)                               |

|     | 8.2.4<br>8.2.5 | PPGTT Page Fault Interface ([DevCTG] Only)                                         |

|     | 8.2.5          |                                                                                    |

| 0.0 |                | TLB Read Interface                                                                 |

| 8.3 | GFX_IVIO       | DE – Graphics Mode Register 235                                                    |

| 8.4  | EXCC—E     | xecute Condition Code Register 236                                 |     |

|------|------------|--------------------------------------------------------------------|-----|

| 8.5  | RINGBU     | -Ring Buffer Registers                                             |     |

|      | 8.5.1      | UHPTR — Pending Head Pointer Register                              |     |

| 8.6  | Debua R    | egisters Control                                                   |     |

|      | 8.6.1      | HW_MEMRD—Memory Read Sync Register (Debug)                         |     |

|      | 8.6.2      | IPEIR—Instruction Parser Error Identification Register (Debug) 246 |     |

|      | 8.6.3      | HW_MEMCWR—Memory Snoop Sync Register ([DevCTG])                    |     |

|      | 8.6.4      | IPEHR—Instruction Parser Error Header Register (Debug)             |     |

|      | 8.6.5      | INSTDONE—Instruction Stream Interface Done Register (Debug). 249   |     |

|      | 8.6.6      | INSTPS—Instruction Parser State Register (Debug)                   |     |

|      | 8.6.7      | ACTHD — Active Head Pointer Register (Debug)                       |     |

|      | 8.6.8      | DMA_FADD_P — Primary DMA Engine Fetch Address (Debug) 253          |     |

|      | 8.6.9      | INSTDONE_1 — Additional Instruction Stream Interface Done (Debug)  | 254 |

|      | 8.6.10     | INSTDONE_1 — Additional Instruction Stream Interface Done          |     |

|      |            | (Debug)[DevCTG+]                                                   |     |

|      | 8.6.11     | GFX_FLSH_CNTL — Graphics Flush Control                             |     |

|      | 8.6.12     | CTXT_PREMP_DBG - Pre-emption Debug Register ([DevCTG] Only)259     |     |

| 8.7  | NOPID -    | - NOP Identification Register                                      |     |

| 8.8  |            | g Timer Registers [DevCTG]                                         |     |

|      | 8.8.1      | PR_CTR_CTL—Render Watchdog Counter Control                         |     |

|      | 8.8.2      | PR_CTR_THRSH—Render Watchdog Counter Threshold                     |     |

|      | 8.8.3      | PR_CTR—Render Watchdog Counter                                     |     |

| 8.9  | Interrupt  | t Control Registers                                                |     |

|      | 8.9.1      | HWS_PGA — Hardware Status Page Address Register                    |     |

|      | 8.9.2      | PWRCTXA — Power Context Register Address ([DevCL] Only) 271        |     |

|      | 8.9.3      | HWSTAM — Hardware Status Mask Register                             |     |

|      | 8.9.4      | IER — Interrupt Enable Register                                    |     |

|      | 8.9.5      | IIR — Interrupt Identity Register                                  |     |

|      | 8.9.6      | IMR—Interrupt Mask Register                                        |     |

|      | 8.9.7      | ISR — Interrupt Status Register                                    |     |

| 8.10 | Hardwar    | e-Detected Error Bit Definitions (for EIR, EMR, ESR)               |     |

|      | 8.10.1     | EIR — Error Identity Register                                      |     |

|      | 8.10.2     | EMR—Error Mask Register                                            |     |

|      | 8.10.3     | ESR—Error Status Register                                          |     |

| 8.11 | Probe Lis  | st Registers ([DevCTG] Only)                                       |     |

|      | 8.11.1     | PRBL_SF – Probe List Slot Fault Register                           |     |

| 8.12 | Register   | Definitions for Context Save                                       |     |

|      | 8.12.1     | INSTPM—Instruction Parser Mode Register                            |     |

|      | 8.12.2     | Cache_Mode_0— Cache Mode Register 0                                |     |

|      | 8.12.3     | Cache_Mode_1— Cache Mode Register 1                                |     |

|      | 8.12.4     | FBC RT BASE ADDRESS REGISTER                                       |     |

|      | 8.12.5     | BB_ADDR—Batch Buffer Head Pointer Register                         |     |

|      | 8.12.6     | BB_STATE – Batch Buffer State Register                             |     |

|      | 8.12.7     | CTXT_SR_CTL – Context Save/Restore Control Register                |     |

| 8.13 | Logical C  | Context Support                                                    |     |

|      | 8.13.1     | CCID—Current Context ID Register                                   |     |

|      | 8.13.2     | CXT_SIZE—Context Size with Extended State                          |     |

|      | 8.13.3     | CXT_SIZE_NOEXT—Context Size without the Extended State 306         |     |

| 8.14 | Arbitratio | on Control, and Scratch Bits                                       |     |

|      | 8.14.1     | MI_DISPLAY_POWER_DOWN—Display Power Down ([DevCL+]) 307            |     |

|      | 8.14.2     | MI_ARB_STATE—Memory Interface Arbitration State Register 308       |     |

|      | 8.14.3     | MI_RDRET_STATE—Memory Interface Read Return State Register 312     |     |

|      | 8.14.4     | MI_MODE — Mode Register for Software Interface                     |     |

|      |            |                                                                    |     |

|      | 8.14.5    | ECOSKPD—ECO Scratch Pad (DEBUG) 321                                         |

|------|-----------|-----------------------------------------------------------------------------|

| 8.15 | Debug R   | legisters                                                                   |

|      | 8.15.1    | ČSFLFSM — Flush FSM (Debug)                                                 |

|      | 8.15.2    | CSFLFLAG — Flush FLAG (Debug)                                               |

|      | 8.15.3    | CSFLTRK — Flush Track (Debug)                                               |

|      |           | CSCMDOP — Instruction DWORD (Debug)                                         |

|      | 8.15.4    |                                                                             |

|      | 8.15.5    | CSCMDVLD — Instruction DWORD Valid (Debug)                                  |

|      | 8.15.6    | PREEMPTDLY — Power Context Register Address ([DevCTG] Only) (Debug) 329     |

|      | 8.15.7    | CLKCMP — Compare count clock stop (Debug) 330                               |

|      | 8.15.8    | VFDC—Set Value of Draw Count (DEBUG)                                        |

|      | 8.15.9    | VFSKPD—VF Scratch Pad (DEBUG)                                               |

| 8.16 | Pipelines | Statistics Counter Registers                                                |

|      | 8.16.1    | IA_VERTICES_COUNT — Reported Vertices Counter                               |

|      | 8.16.2    | IA_PRIMITIVES_COUNT — Reported Vertex Fetch Output Primitives Counter 333   |

|      | 8.16.3    | VS_INVOCATION_COUNT— Reported Vertex Shader Invocation Counter 334          |

|      | 8.16.4    | GS_INVOCATION_COUNT — Reported Geometry Shader Thread Invocation            |

|      | 0.10.4    | Counter                                                                     |

|      | 8.16.5    | GS_PRIMITIVES_COUNT — Reported Geometry Shader Output Primitives Counter    |

|      | 0.10.0    |                                                                             |

|      | 0.1//     | 335                                                                         |

|      | 8.16.6    | CL_INVOCATION_COUNT— Reported Clipper Thread Invocation Counter 335         |

|      | 8.16.7    | CL_PRIMITIVES_COUNT— Reported Clipper Output Primitives Counter 336         |

|      | 8.16.8    | PS_INVOCATION_COUNT— Reported Pixels Shaded counter 337                     |

|      | 8.16.9    | PS_DEPTH_COUNT — Reported Pixels Passing Depth Test Counter 337             |

|      |           | TIMESTAMP — Reported Timestamp Count 338                                    |

|      |           | TIMESTAMP — Reported Timestamp Count ([DevCTG] Only) 339                    |

|      | 8.16.12   | VT_CL_WRITTEN— Number of Cachelines for the GTT used for VT-d purposes      |

|      |           | (Debug/Validation Only)([DevCTG] only)                                      |

|      | 8.16.13   | SO_NUM_PRIMS_WRITTEN— Reported Stream Output Num Primitives Written         |

|      |           | Counter ([DevCTG] Only)                                                     |

|      | 8.16.14   | SO_PRIM_STORAGE_NEEDED — Reported Stream Output Primitive Storage           |

|      |           | Needed Counter ([DevCTG] Only)                                              |

| 8.17 | мтсн с    | ID_RST – Matched Context ID Reset Register                                  |

| 8.18 |           | Related Registers for Flip Queue                                            |

| 0.10 |           |                                                                             |

|      | 8.18.1    | MAXQ_FLIP_A – Maximum Flips Allowed for Display A Register ([DevCTG] Only)  |

|      | 0 10 0    |                                                                             |

|      | 8.18.2    | MAXQ_FLIP_B – Maximum Flips Allowed for Display B Register ([DevCTG] Only)  |

|      | 0.40.0    |                                                                             |

|      | 8.18.3    | NUM_FLIP_A – Number of flips pending on Display A Register ([DevCTG] Only)  |

|      |           |                                                                             |

|      | 8.18.4    | NUM_FLIP_B – Number of flips pending on Display B Register ([DevCTG] Only)  |

|      |           |                                                                             |

| 8.19 | Video Co  | odec Engine Command Streamer                                                |

|      | 8.19.1    | Registers in the VCE Command Streamer [DevCTG+]                             |

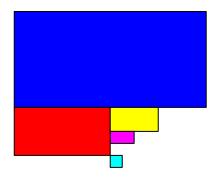

|      | 8.19.2    | Unique BCS Registers ([DevCTG] Only)                                        |