# Intel<sup>®</sup> 965 Express Chipset Family and Intel<sup>®</sup> G35 Express Chipset Graphics Controller PRM

Programmer's Reference Manual (PRM)

Volume 2: 3D/Media

January 2008

**Revision 1.0b**

Technical queries: ilg@linux.intel.com www.intellinuxgraphics.org

#### Creative Commons License

#### You are free:

to Share - to copy, distribute, display, and perform the work

#### Under the following conditions:

Attribution. You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

No Derivative Works. You may not alter, transform, or build upon this work.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 965 Express Chipset family and Intel<sup>®</sup> G35 Express Chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

I2C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I2C bus/protocol and was developed by Intel. Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2008, Intel Corporation. All rights reserved.

## Contents

| 1 | Introdu      | uction    |            |                                                | 13  |  |

|---|--------------|-----------|------------|------------------------------------------------|-----|--|

|   | 1.1          | Notation  |            | entions<br>Bits and Software Compatibility     |     |  |

|   | 1.2          |           |            |                                                |     |  |

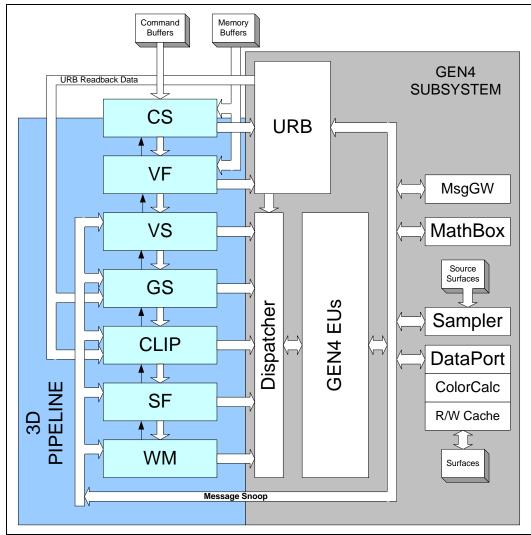

| 2 | 3D Pipeline2 |           |            |                                                |     |  |

|   | 2.1          | Introduc  | tion       |                                                | .26 |  |

|   | 2.2          | 3D Pipeli | w          | 26                                             |     |  |

|   |              | 2.2.1     | •          | e Stages                                       |     |  |

|   | 2.3          |           |            | iew                                            |     |  |

|   | 2.4          |           |            | /iew                                           |     |  |

|   | 2.5          | 3D Pipeli |            | verview                                        |     |  |

|   |              | 2.5.1     |            | Nodel                                          |     |  |

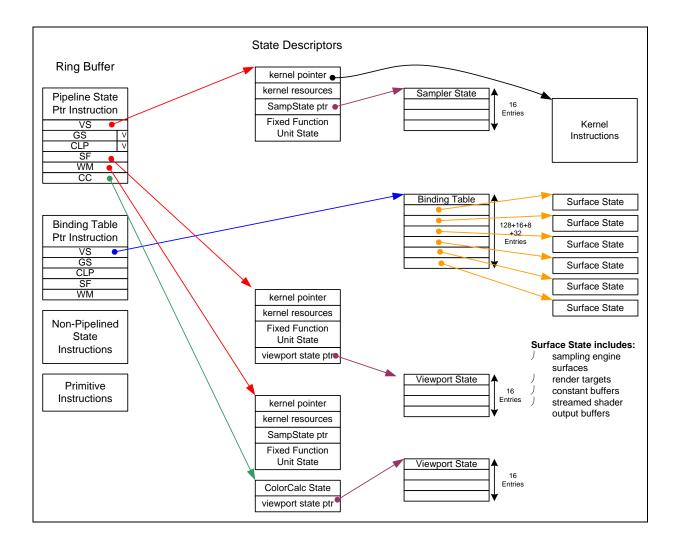

|   |              | 2.5.2     |            | PIPELINED_POINTERS                             |     |  |

|   |              | 2.5.3     |            | BINDING_TABLE_POINTERS                         |     |  |

|   | 2.6          |           |            | 2W                                             |     |  |

|   |              | 2.6.1     |            | B Entry (VUE) Formats                          |     |  |

|   |              | 2.6.2     |            | sitions                                        |     |  |

|   |              |           |            | Clip Space Position                            |     |  |

|   |              |           |            | NDC Space Position<br>Screen-Space Position    |     |  |

|   | 2.7          | 2D Dinali |            | verview                                        |     |  |

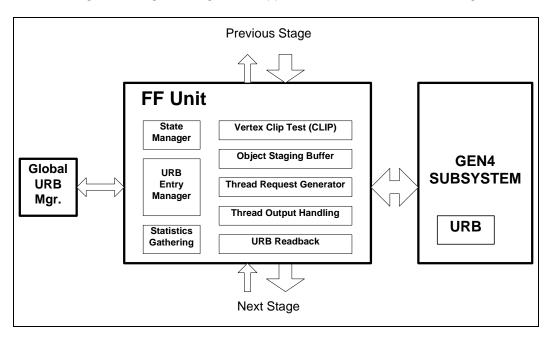

|   | 2.7          | 2.7.1     | 0          | D FF Unit Block Diagram                        |     |  |

|   |              | 2.7.1     |            | 3D FF Unit Functions                           |     |  |

|   |              | 2.7.3     |            | age Input                                      |     |  |

|   |              | 2.7.4     | •          | State Commands                                 |     |  |

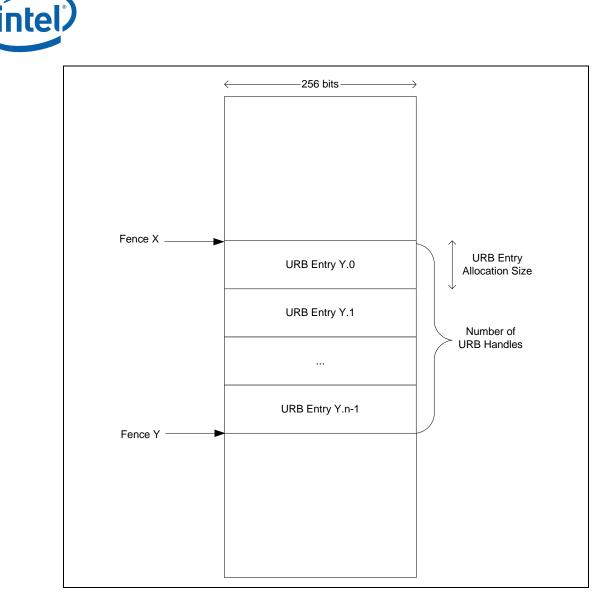

|   |              |           |            | URB_FENCE                                      |     |  |

|   |              |           |            | 3DSTATE_PIPELINED_POINTERS                     |     |  |

|   |              |           | 2.7.4.3    | 3DSTATE_BINDING_TABLE_POINTERS                 |     |  |

|   |              |           |            | CONSTANT_BUFFER                                |     |  |

|   |              | 2.7.5     |            | ode                                            |     |  |

|   |              | 2.7.6     |            | Management                                     |     |  |

|   |              | 2.7.7     |            | tiation Management                             |     |  |

|   |              |           |            | Thread Input Buffering                         |     |  |

|   |              | 2 7 0     |            | Thread Resource Allocation                     |     |  |

|   |              | 2.7.8     |            | quest Generation<br>Thread Control Information |     |  |

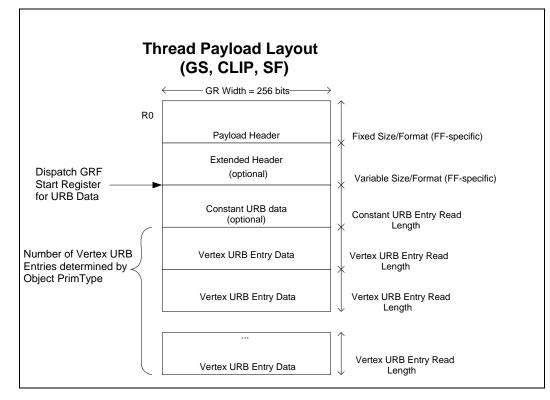

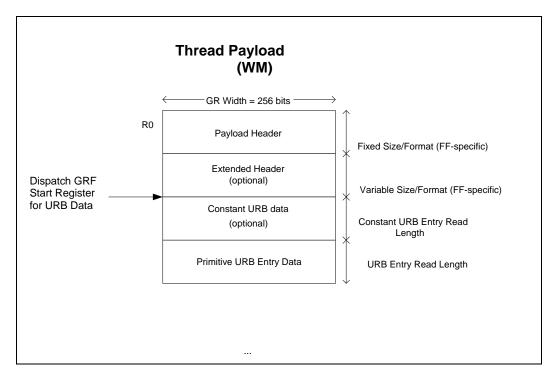

|   |              |           |            | Thread Payload Generation                      |     |  |

|   |              | 2.7.9     |            | tput Handling                                  |     |  |

|   |              | ,         |            | URB Entry Output (VS, GS, CLIP, SF)            |     |  |

|   |              |           |            | VUE Allocation (GS, CLIP)                      |     |  |

|   |              |           | 2.7.9.3    | VUE Dereference (GS, CLIP)                     | .68 |  |

|   |              |           | 2.7.9.4    | Thread Termination                             | 68  |  |

|   |              | 2.7.10    |            | back                                           |     |  |

|   | 2.8          | Synchro   |            | he 3D Pipeline                                 |     |  |

|   |              | 2.8.1     |            | e Synchronization                              |     |  |

|   |              | 2.8.2     | Write Syno | chronization                                   | 69  |  |

|       | 2.8.3          | Synchronization Actions69              |

|-------|----------------|----------------------------------------|

|       |                | 2.8.3.1 Writing a Value to Memory      |

|       |                | 2.8.3.2 Generating an Interrupt        |

|       |                | 2.8.3.3 Invalidating of Caches         |

|       | 2.8.4          | PIPE_CONTROL Command                   |

| Verte | x Fetch (\     | /F) Stage75                            |

| 3.1   | Vertex         | Fetch (VF) Stage Overview75            |

|       | 3.1.1          | Input Assembly75                       |

|       |                | 3.1.1.1 Vertex Assembly75              |

|       | 3.1.2          | Vertex Cache                           |

| 3.2   |                | ge Input76                             |

| 3.3   | Index E        | Buffer (IB)                            |

|       | 3.3.1          | 3DSTATE_INDEX_BUFFER78                 |

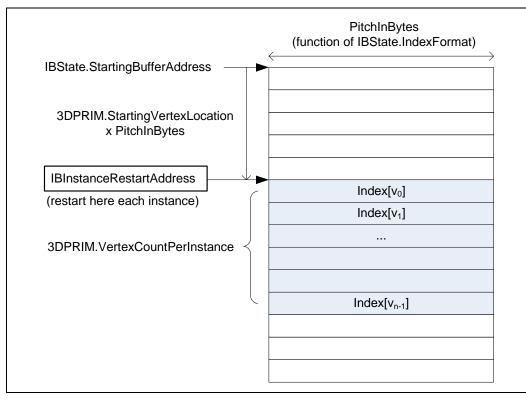

|       | 3.3.2          | Index Buffer Access                    |

| 3.4   |                | Buffers (VBs)82                        |

|       | 3.4.1          | 3DSTATE_VERTEX_BUFFERS                 |

|       | 3.4.2          | VERTEX_BUFFER_STATE Structure          |

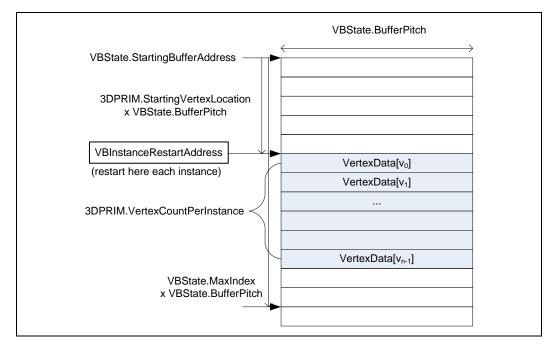

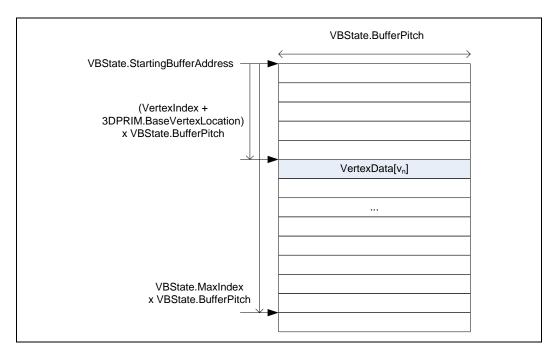

|       | 3.4.3          | VERTEXDATA Buffers – SEQUENTIAL Access |

| o -   | 3.4.4          | VERTEXDATA Buffers – RANDOM Access     |

| 3.5   |                | ertex Definition                       |

|       | 3.5.1          | 3DSTATE_VERTEX_ELEMENTS                |

|       | 3.5.2          | VERTEX_ELEMENT_STATE Structure         |

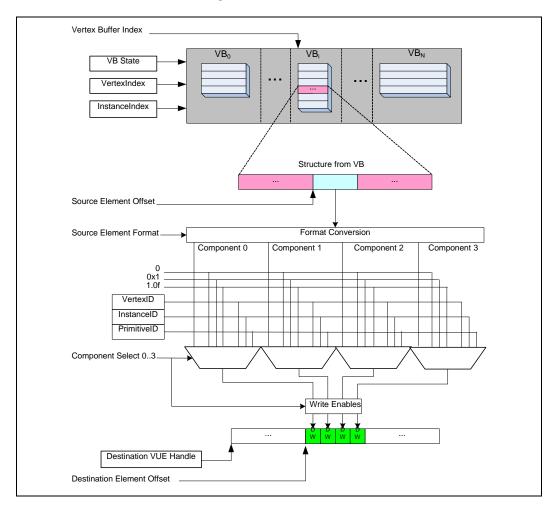

| 2 (   | 3.5.3          | Vertex Element Data Path               |

| 3.6   |                | nitive Processing                      |

|       | 3.6.1<br>3.6.2 | 3DPRIMITIVE Command                    |

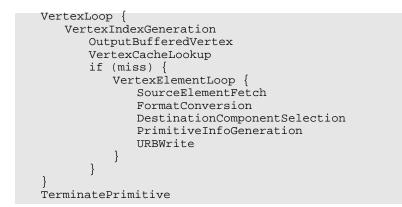

|       | 3.6.2<br>3.6.3 | Functional Overview                    |

|       | 3.6.4          | VertexIndexGeneration                  |

|       | 3.6.5          | VertexCacheLookup                      |

|       | 3.6.6          | VertexElementLoop                      |

|       | 3.6.7          | SourceElementFetch                     |

|       | 3.6.8          | FormatConversion                       |

|       | 3.6.9          | DestinationFormatSelection             |

|       | 3.6.10         | URBWrite                               |

|       | 3.6.11         | OutputBufferedVertex                   |

| 3.7   | Danglir        | ng Vertex Removal                      |

| Verte | x Shader       | (VS) Stage                             |

| 4.1   | VS Sta         | ge Overview                            |

|       | 4.1.1          | Vertex Caching                         |

| 4.2   |                | ge Input                               |

|       | 4.2.1          | State                                  |

|       | 1.2.1          | 4.2.1.1 URB_FENCE                      |

|       |                | 4.2.1.2 VS_STATE                       |

|       | 4.2.2          | Input Vertices                         |

| 4.3   |                | ead Request Generation                 |

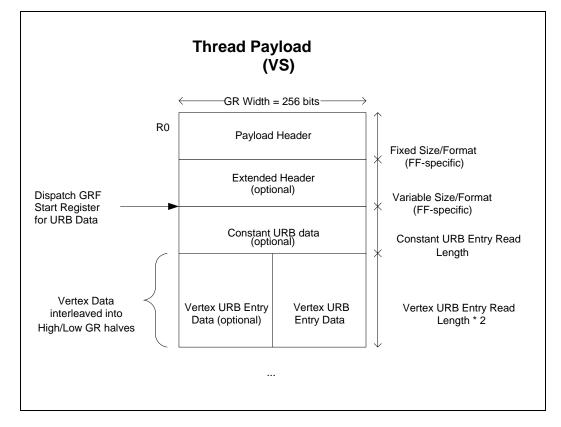

|       | 4.3.1          | Thread Payload                         |

| 4.4   |                | ead Execution                          |

|       | 4.4.1          | Vertex Output                          |

|       | 4.4.2          | Thread Termination                     |

| 4.5   |                | ve Output                              |

|       |                | •                                      |

| Geom   | etry Shad | der (GS) Stage                                      | 11 |

|--------|-----------|-----------------------------------------------------|----|

| 5.1    | GS Sta    | ge Overview                                         | 11 |

| 5.2    |           | ge Input                                            |    |

|        | 5.2.1     | State                                               |    |

|        |           | 5.2.1.1 GS_STATE                                    |    |

| 5.3    | Object    | Staging                                             |    |

| 5.4    | -         | ead Request Generation                              |    |

| 0.1    | 5.4.1     | Object Vertex Ordering                              |    |

|        | 5.4.2     | GS Thread Payload                                   |    |

| 5.5    |           | ead Execution                                       |    |

| 0.0    | 5.5.1     | Vertex Output                                       |    |

|        | 5.5.2     | Thread Termination                                  |    |

| 5.6    |           | Header Readback                                     |    |

| 5.7    |           | ve Output                                           |    |

|        |           |                                                     |    |

| Clip S | tage      |                                                     | 12 |

| 6.1    | CLIP St   | tage Overview                                       | 12 |

|        | 6.1.1     | Clip Stage – General-Purpose Processing             | 12 |

|        | 6.1.2     | Clip Stage – 3D Clipping                            |    |

| 6.2    | Concep    | ots                                                 | 13 |

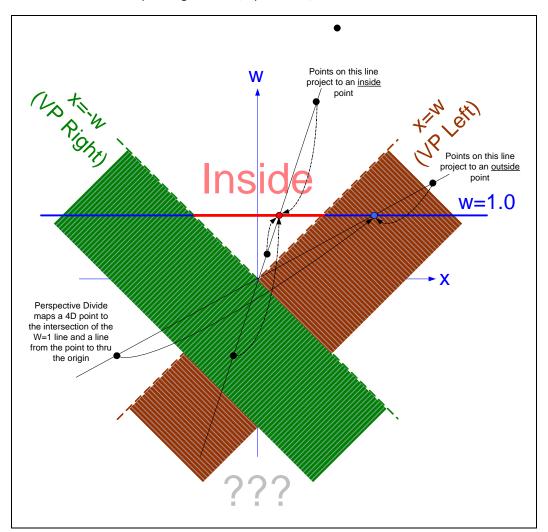

|        | 6.2.1     | The Clip Volume                                     | 13 |

|        |           | 6.2.1.1 View Volume                                 | 13 |

|        | 6.2.2     | User-Specified Clipping                             | 13 |

|        |           | 6.2.2.1 User Clip Planes                            | 13 |

|        | 6.2.3     | Negative-W Clipping Errata                          |    |

|        |           | 6.2.3.1 W Clipping Errata (DevBW, DevCL-A)          |    |

|        |           | 6.2.3.2 W Clipping Errata (DevCL-B)                 |    |

|        | 6.2.4     | Tristrip Clipping Errata [Pre-DevBW-E1], [DevCL]    |    |

|        | 6.2.5     | Guard Band                                          |    |

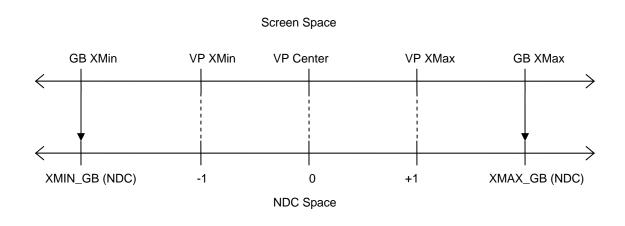

|        |           | 6.2.5.1 NDC Guardband Parameters                    |    |

|        |           | 6.2.5.2 Screen Space Guardband Parameters           |    |

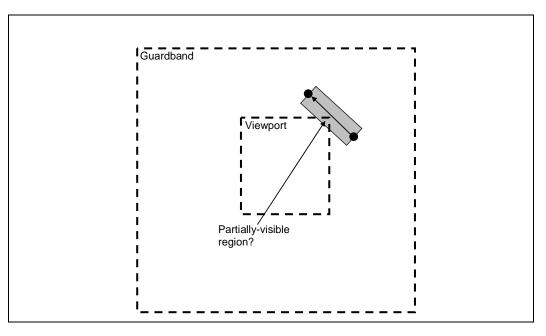

|        | 6.2.6     | Vertex-Based Clip Testing & Considerations          |    |

|        |           | 6.2.6.1Triangle Objects6.2.6.2Non-Wide Line Objects |    |

|        |           | 6.2.6.3 Wide Line Objects                           |    |

|        |           | 6.2.6.4 Wide Points                                 |    |

|        |           | 6.2.6.5 RECTLIST                                    |    |

|        | 6.2.7     | 3D Clipping                                         |    |

| 6.3    | <u> </u>  | tage Input                                          |    |

| 0.0    | 6.3.1     | State                                               |    |

|        | 0.0.1     | 6.3.1.1 CLIP_STATE                                  |    |

|        |           | 6.3.1.2 CLIP_VIEWPORT                               |    |

| 6.4    | Vertex    | ClipTest Function                                   |    |

| 6.5    |           | Staging                                             |    |

| 0.0    | 6.5.1     | Partial Object Removal                              |    |

|        | 6.5.2     | ClipDetermination Function                          |    |

|        | 6.5.3     | ClipMode                                            |    |

|        |           | 6.5.3.1 NORMAL ClipMode                             |    |

|        |           | 6.5.3.2 CLIP_ALL ClipMode                           |    |

|        |           | 6.5.3.3 CLIP_NON_REJECT ClipMode                    |    |

|        |           | 6.5.3.4 REJECT_ALL ClipMode                         |    |

|        |           | 6.5.3.5 ACCEPT_ALL ClipMode                         |    |

| 6.6    | Object    | Pass-Through                                        | 16 |

| 6.7      | CLIP Thr       | ead Request Generation                                                      | 166 |

|----------|----------------|-----------------------------------------------------------------------------|-----|

|          | 6.7.1          | Object Vertex Ordering                                                      |     |

|          | 6.7.2          | CLIP Thread Payload                                                         | 168 |

| 6.8      | CLIP Thr       | ead Execution                                                               | 170 |

|          | 6.8.1          | Vertex Output                                                               |     |

|          | 6.8.2          | Thread Termination                                                          | 171 |

| 6.9      | Thread-0       | Generated Vertex Readback                                                   | 172 |

| 6.10     | Primitive      | e Output                                                                    | 172 |

| 6.11     |                | Inctionality                                                                |     |

| 0        | 6.11.1         | Statistics Gathering                                                        |     |

|          | 0.11.1         | 6.11.1.1 CL_INVOCATION_COUNT                                                |     |

|          |                | 6.11.1.2 GS_PRIMITIVES_COUNT                                                |     |

| <b>.</b> |                |                                                                             |     |

| Strips   |                | (SF) Stage                                                                  |     |

| 7.1      | Overviev       | N                                                                           | 175 |

|          | 7.1.1          | Inputs from CLIP                                                            | 175 |

|          | 7.1.2          | Attribute Setup/Interpolation Process                                       | 176 |

|          | 7.1.3          | Outputs to WM                                                               | 177 |

| 7.2      | Primitive      | e Assembly                                                                  | 177 |

|          | 7.2.1          | Point List Decomposition                                                    | 181 |

|          | 7.2.2          | Line List Decomposition                                                     | 182 |

|          | 7.2.3          | Line Strip Decomposition                                                    |     |

|          | 7.2.4          | Triangle List Decomposition                                                 |     |

|          | 7.2.5          | Triangle Strip Decomposition                                                |     |

|          | 7.2.6          | Triangle Fan Decomposition                                                  |     |

|          | 7.2.7          | Polygon Decomposition                                                       | 186 |

|          | 7.2.8          | Rectangle List Decomposition                                                |     |

| 7.3      | -              | etup                                                                        |     |

|          | 7.3.1          | Invalid Position Culling (Pre/Post-Transform)                               |     |

|          | 7.3.2          | Viewport Transformation                                                     |     |

|          | 7.3.3<br>7.3.4 | Destination Origin Bias                                                     |     |

|          | 7.3.4          | Point Rasterization Rule Adjustment<br>Drawing Rectangle Offset Application |     |

|          | 7.3.5          | 7.3.5.1 3DSTATE_DRAWING_RECTANGLE                                           | 102 |

|          | 7.3.6          | Point Width Application                                                     |     |

|          | 7.3.7          | Rectangle Completion                                                        |     |

|          | 7.3.8          | Vertex X,Y Clamping and Quantization                                        |     |

|          | 7.3.9          | Degenerate Object Culling                                                   |     |

|          | 7.3.10         | Degenerate Triangle Culling                                                 |     |

|          | 7.3.11         | Triangle Orientation (Face) Culling                                         |     |

|          | 7.3.12         | Scissor Rectangle Clipping                                                  |     |

|          | 7.3.13         | Line Rasterization                                                          |     |

|          |                | 7.3.13.1 Zero-Width (Cosmetic) Line Rasterization                           |     |

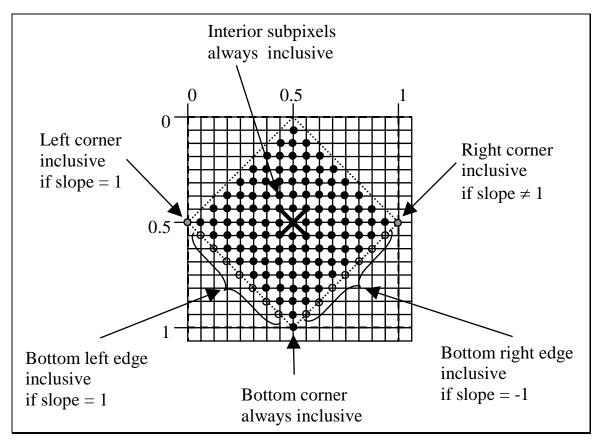

|          |                | 7.3.13.2 Diamond Exit Sampling Rules – Legacy Mode                          |     |

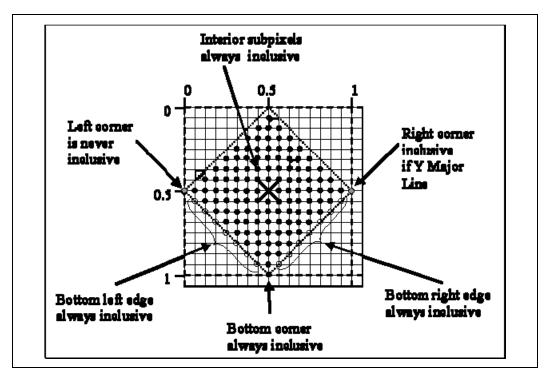

|          |                | 7.3.13.3 Diamond Exit Sampling Rules – New Mode                             |     |

|          |                | 7.3.13.4 Non-Antialiased Wide Line Rasterization                            |     |

|          |                | 7.3.13.5 Anti-aliased Line Rasterization                                    |     |

| 7.4      | •              | ne State Summary                                                            |     |

|          | 7.4.1          | SF_STATE                                                                    |     |

|          | 7.4.2          | SF_VIEWPORT                                                                 |     |

| 7.5      | The SF T       | Thread Interpolation Coefficient Calculation                                |     |

|          | 7.5.1          | SF Setup Parameters Passed to SF Thread                                     |     |

|          |                | 7.5.1.1 TRIANGLE Parameters                                                 | 216 |

|       |           | 7.5.1.2<br>7.5.1.3<br>7.5.1.4 | RECTANGLE Parameters<br>POINT Parameters<br>LINE Parameters |     |

|-------|-----------|-------------------------------|-------------------------------------------------------------|-----|

|       | 7.5.2     | SF (Setup                     | ) Thread Payload                                            |     |

|       | 7.5.3     |                               | Execution                                                   |     |

|       | 7.5.4     |                               | l Output                                                    |     |

| 7.6   | Other S   |                               |                                                             |     |

|       | 7.6.1     |                               | Gathering                                                   |     |

| Windo | ower (WM) | ) Stage                       |                                                             | 224 |

| 8.1   | Overvie   | w                             |                                                             |     |

|       | 8.1.1     | Inputs fro                    | m SF to WM                                                  |     |

| 8.2   | Window    |                               | State                                                       |     |

| 0.2   | 8.2.1     |                               | Έ                                                           |     |

| 8.3   |           |                               |                                                             |     |

| 0.3   |           |                               |                                                             |     |

|       | 8.3.1     | -                             | Rectangle Clipping                                          |     |

|       | 8.3.2     |                               | erization                                                   |     |

|       |           | 8.3.2.1                       | Coverage Values for Anti-Aliased Lines                      |     |

|       |           | 8.3.2.2                       | Line Stipple                                                |     |

|       |           | 8.3.2.3                       | 3DSTATE_LINE_STIPPLE                                        |     |

|       | 8.3.3     |                               | Triangle and Rectangle) Rasterization                       |     |

|       |           | 8.3.3.1                       | Polygon Stipple                                             |     |

|       |           | 8.3.3.2                       | 3DSTATE_POLY_STIPPLE_OFFSET                                 |     |

|       |           | 8.3.3.3                       | 3DSTATE_POLY_STIPPLE_PATTERN                                |     |

|       |           | 8.3.3.4                       | 3DSTATE_GLOBAL_DEPTH_OFFSET_CLAMP                           |     |

| 8.4   | Early De  | •                             | Processing                                                  |     |

|       | 8.4.1     | Depth Co                      | efficient Read-Back                                         |     |

|       | 8.4.2     | Depth Off                     | set                                                         |     |

|       | 8.4.3     | Early Dep                     | th Test / Stencil Test/Write                                |     |

|       |           | 8.4.3.1                       | Software-Provided PS Kernel Info                            |     |

|       |           | 8.4.3.2                       | Early Depth Test Cases                                      |     |

|       | 8.4.4     | Depth/Ste                     | encil Buffer State                                          |     |

|       |           | 8.4.4.1                       | 3DSTATE_DEPTH_BUFFER                                        |     |

| 8.5   | Pixel Sh  | ader Threa                    | d Generation                                                |     |

|       | 8.5.1     |                               | Iping (Dispatch Size) Control                               |     |

|       | 8.5.2     |                               | Payload for Normal Dispatch                                 |     |

| 0 4   |           |                               | S                                                           |     |

| 8.6   |           |                               |                                                             |     |

|       | 8.6.1     |                               | Gathering                                                   |     |

| Color |           | •                             | erger)                                                      |     |

|       | 9.1.1     | Alpha Tes                     | t                                                           |     |

|       | 9.1.2     |                               | fer Coordinate Offset Disable                               |     |

|       | 9.1.3     |                               | st                                                          |     |

|       | 9.1.4     |                               | st                                                          |     |

|       | 9.1.5     |                               | Color Clamping                                              |     |

|       | 9.1.6     | Color Buff                    | er Blending                                                 |     |

|       |           | 9.1.6.1                       | 3DSTATE_CONSTANT COLOR                                      |     |

|       | 9.1.7     | Post-Blen                     | d Color Clamping                                            |     |

|       | 9.1.8     | Color Qua                     | ntization                                                   |     |

|       | 9.1.9     | Dithering.                    |                                                             |     |

|       | 9.1.10    | 0                             | date                                                        |     |

|       |           | 9.1.10.1                      |                                                             |     |

|       |           | 9.1.10.2                      | Depth Buffer Updates                                        |     |

|       |           |                               | Color Gamma Correction                                      |     |

|         |            | 9.1.10.4    | Color Buffer Updates                            | . 282 |

|---------|------------|-------------|-------------------------------------------------|-------|

| 9.2     | Pixel Pipe | eline State | Summary                                         | . 283 |

|         | 9.2.1      | COLOR_C     | ALC_STATE                                       | . 283 |

|         | 9.2.2      |             | PORT                                            |       |

| 9.3     | Other Pix  |             | Functions                                       |       |

|         | 9.3.1      | •           | Gathering                                       |       |

|         |            |             | 5                                               |       |

| Media a | and Genei  | ral Purpose | Pipeline                                        | . 295 |

| 10.1    | Introduc   | tion        |                                                 | . 295 |

|         | 10.1.1     | Terminolo   | gies                                            | . 296 |

| 10.2    | Media Pi   | peline Over | view                                            | . 298 |

| 10.3    | Program    | ming Media  | Pipeline                                        | . 299 |

|         | 10.3.1     | -           | Sequence                                        |       |

|         | 10.3.2     |             | _atency                                         |       |

| 10.4    | Video Fro  |             | it                                              |       |

|         | 10.4.1     |             | ·                                               |       |

|         |            | 10.4.1.1    | Interface to Command Streamer                   |       |

|         |            | 10.4.1.2    | Interface to Thread Spawner                     |       |

|         |            | 10.4.1.3    | Interface to State Variable Manager             |       |

|         |            |             | Interface to Global URB Manager                 |       |

|         |            |             | Interface to URB                                |       |

|         | 10.4.2     |             | perations                                       |       |

|         |            | 10.4.2.1    | Generic Mode                                    |       |

|         |            | 10.4.2.2    | IS Mode                                         | . 308 |

|         |            | 10.4.2.3    | VLD Mode                                        | . 308 |

|         | 10.4.3     |             | unter                                           |       |

| 10.5    | Thread S   | -           | it                                              |       |

|         | 10.5.1     | •           | tions                                           |       |

|         | 10.0.1     | 10.5.1.1    | Root Threads Lifecycle                          |       |

|         |            | 10.5.1.2    | URB Handles                                     |       |

|         |            | 10.5.1.3    | Root to Child Responsibilities                  |       |

|         |            | 10.5.1.4    | Multiple Simultaneous Roots                     |       |

|         |            | 10.5.1.5    | Synchronized Root Threads                       |       |

|         |            | 10.5.1.6    | Deadlock Prevention                             |       |

|         |            | 10.5.1.7    | Child Thread Lifecycle                          |       |

|         |            | 10.5.1.8    | Arbitration between Root and Child Threads      |       |

|         | 10.5.2     | Interfaces  |                                                 |       |

|         |            | 10.5.2.1    | Interface to VFE                                | . 325 |

|         |            | 10.5.2.2    | Interface to Thread Dispatcher                  |       |

| 10.6    | Media St   |             | ·                                               |       |

|         | 10.6.1     |             | te Model                                        |       |

|         | 10.6.2     |             | Ε                                               |       |

|         | 10.6.3     | VLD STAT    | Έ                                               | . 329 |

|         | 10.6.4     |             | E_DESCRIPTOR                                    |       |

| 10.7    | Media St   |             |                                                 |       |

|         | 10.7.1     |             | ATE_POINTERS Command                            |       |

|         | 10.7.2     | _           | BJECT Command                                   |       |

|         |            | 10.7.2.1    | Inline and Indirect Data Format in Generic Mode |       |

|         |            | 10.7.2.2    | Inline and Indirect Data Format in IS Mode      |       |

|         |            | 10.7.2.3    | Inline and Indirect Data Format in VLD Mode     |       |

| 10.8    | Media Me   | essages     |                                                 |       |

|         | 10.8.1     | 0           | yload Messages                                  |       |

|         |            |             | Generic Mode Root Thread                        |       |

|         |            |             |                                                 |       |

|       |          | 10.8.1.2    | IS-Mode Root Thread            | 346 |

|-------|----------|-------------|--------------------------------|-----|

|       |          | 10.8.1.3    | VLD-Mode Root Thread           | 351 |

|       |          | 10.8.1.4    | Child Thread                   | 356 |

|       | 10.8.2   | Thread Sp   | awn Message                    | 357 |

|       |          | 10.8.2.1    | Message Descriptor             | 358 |

|       |          | 10.8.2.2    | Message Payload                | 359 |

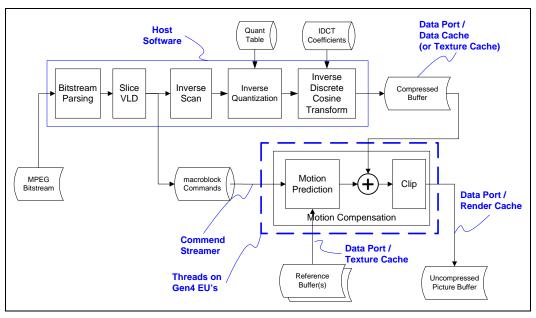

| 10.9  | Media Ap | plications  | with Specific Hardware Support | 360 |

|       | 10.9.1   | Full MPEG   | -2 Decode                      | 360 |

|       |          | 10.9.1.1    | Theory of Operation            | 360 |

|       |          | 10.9.1.2    | Performance                    | 364 |

| 10.10 | Media Ke | ernel Desig | n Guide                        | 364 |

|       | 10.10.1  | MPEG-2 H    | WMC                            | 364 |

|       | 10.10.2  | Deinterlag  | e Filter                       | 366 |

|       | 10.10.3  | Video Enc   | ode                            | 366 |

## Figures

| Figure 6-1. SW Workaround Summary                                                             | 135 |

|-----------------------------------------------------------------------------------------------|-----|

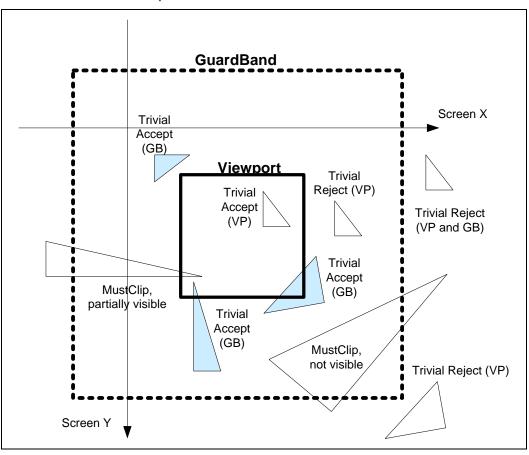

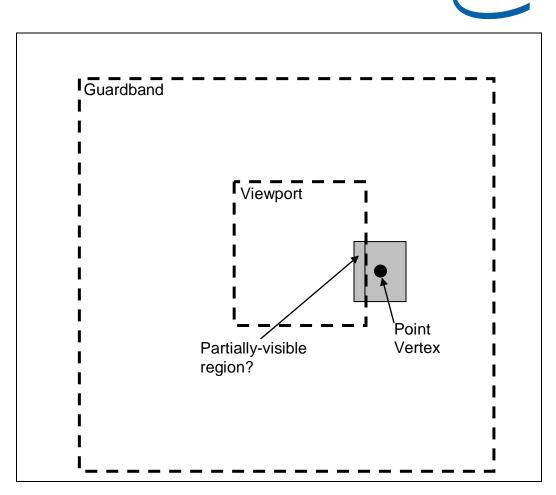

| Figure 6-2. Normal Guardband Operation                                                        | 140 |

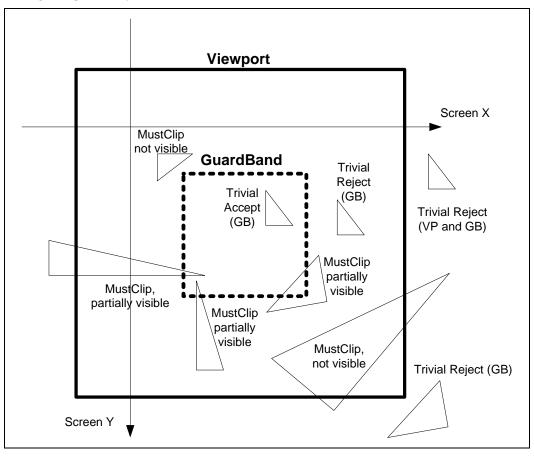

| Figure 6-3. Very Large Viewport Case                                                          | 141 |

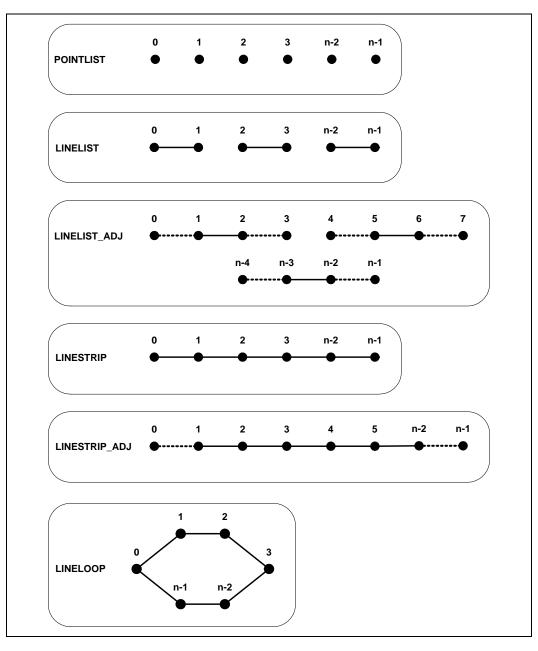

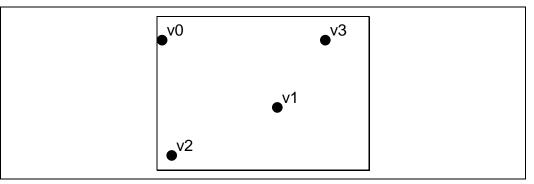

| Figure 7-1. 3DPRIM_POINTLIST Primitive                                                        | 181 |

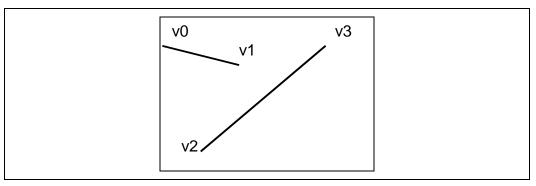

| Figure 7-2. 3DPRIM_LINELIST Primitive                                                         | 182 |

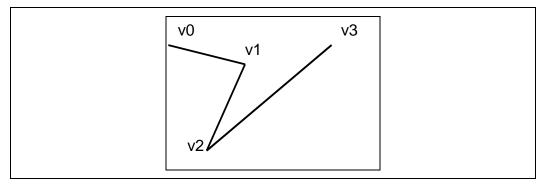

| Figure 7-3. 3DPRIM_LINESTRIP_xxx Primitive                                                    | 183 |

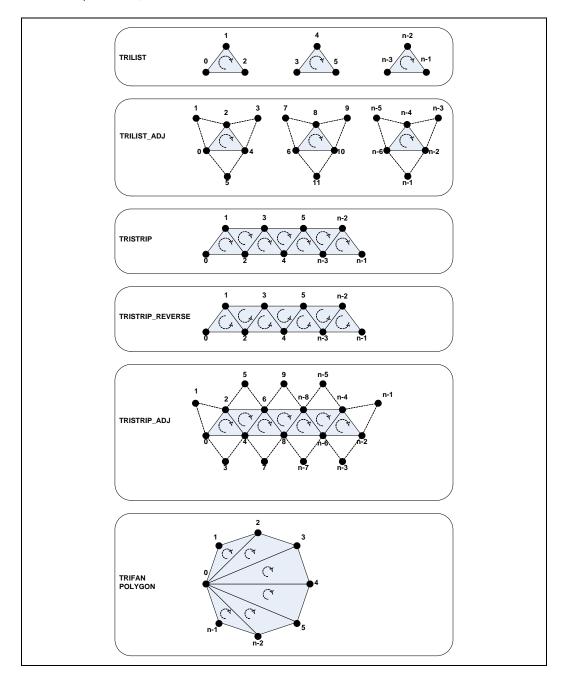

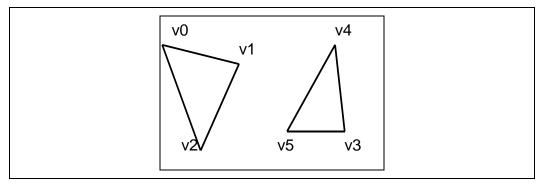

| Figure 7-4. 3DPRIM_TRILIST Primitive                                                          | 184 |

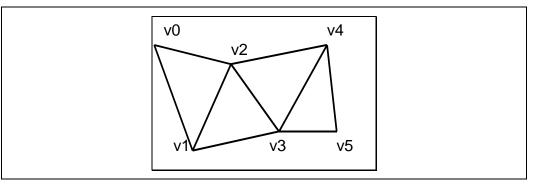

| Figure 7-5. 3DPRIM_TRISTRIP[_REVERSE] Primitive                                               | 185 |

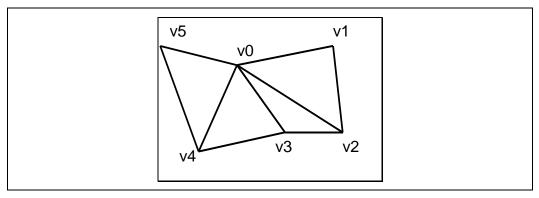

| Figure 7-6. 3DPRIM_TRIFAN Primitive                                                           |     |

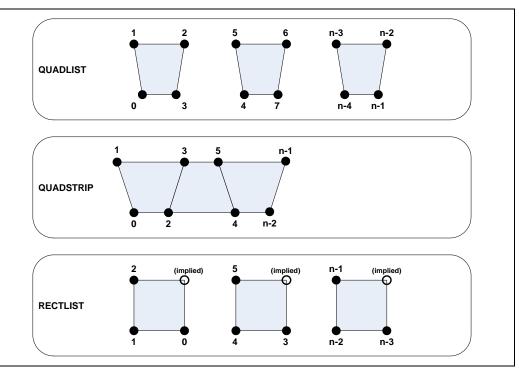

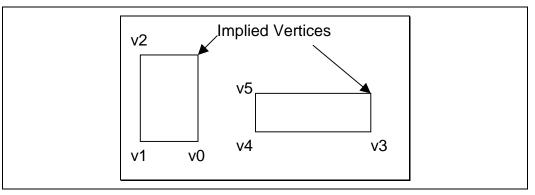

| Figure 7-7. 3DPRIM_RECTLIST Primitive                                                         |     |

| Figure 7-8. Destination Origin Bias                                                           | 189 |

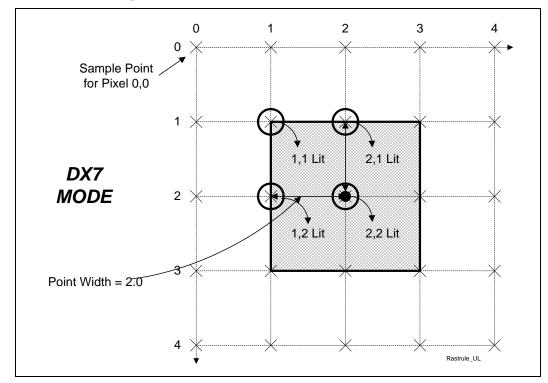

| Figure 7-9. RASTRULE_UPPER_LEFT                                                               |     |

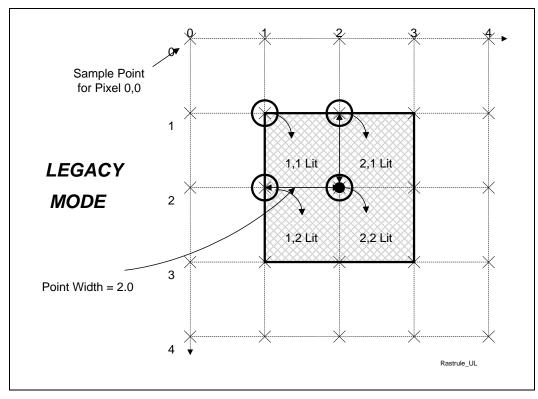

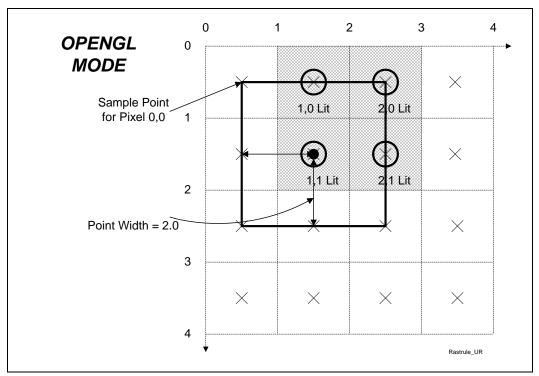

| Figure 7-10. RASTRULE_UPPER_RIGHT                                                             | 191 |

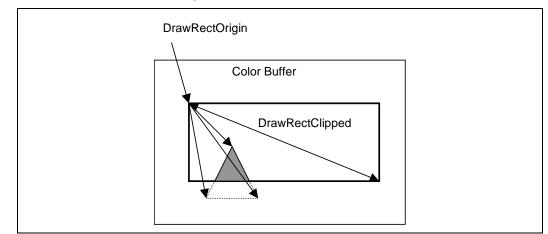

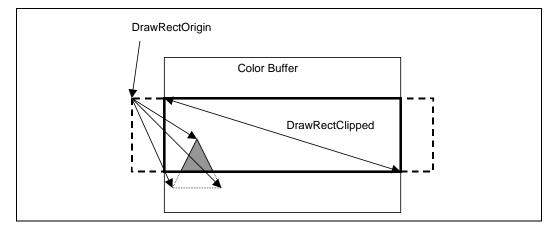

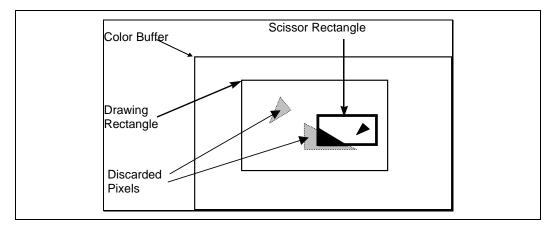

| Figure 7-11. Onscreen Draw Rectangle                                                          |     |

| Figure 7-12. Partially-offscreen Draw Rectangle                                               | 192 |

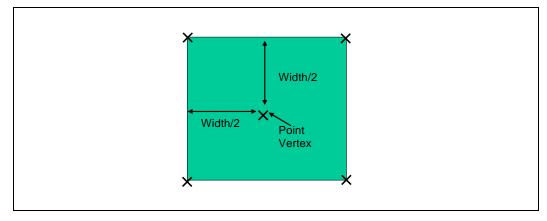

| Figure 7-13. Point Width Application                                                          |     |

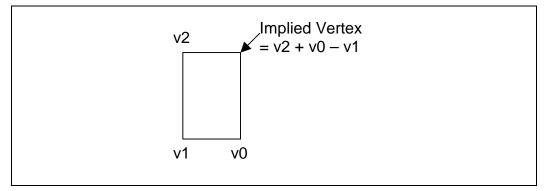

| Figure 7-14. Rectangle Completion                                                             |     |

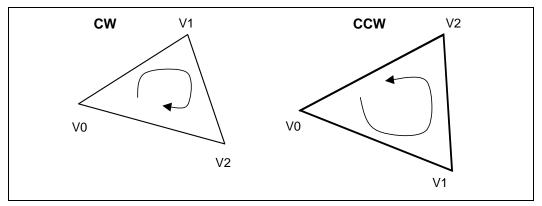

| Figure 7-15. Triangle Winding Order                                                           |     |

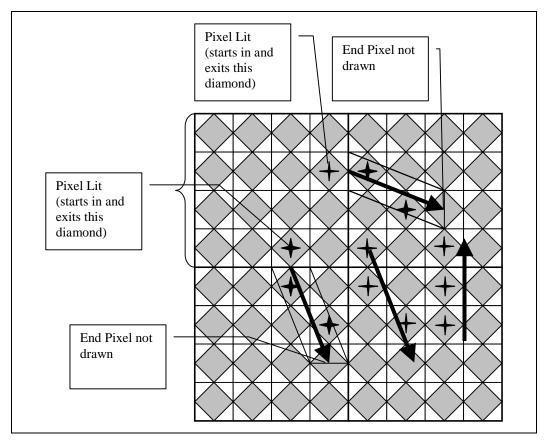

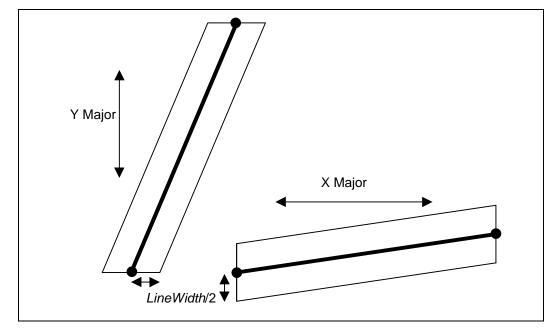

| Figure 7-16. Non-Antialiased Line Rasterization                                               |     |

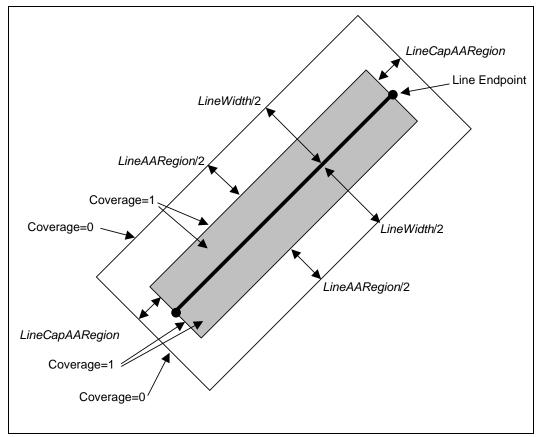

| Figure 7-17. Anti-aliased Line Rasterization                                                  |     |

| Figure 8-1. Pixels with a SubSpan                                                             |     |

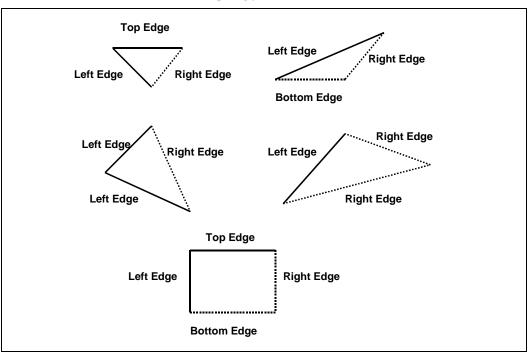

| Figure 8-2. TRIANGLE and RECTANGLE Edge Types                                                 |     |

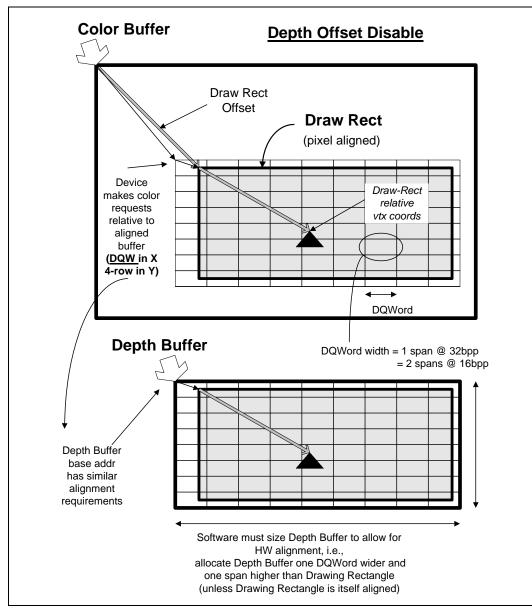

| Figure 9-1. Drawing Rectangle Offset                                                          |     |

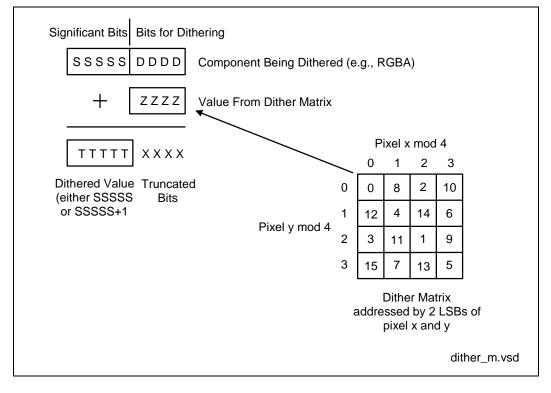

| Figure 9-2. Dithering Process (5-Bit Example)                                                 |     |

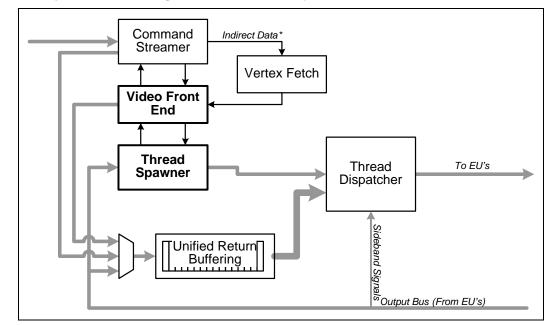

| Figure 10-1. Top level block diagram of the Media Pipeline                                    | 299 |

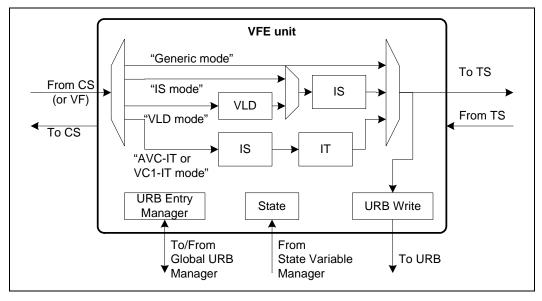

| Figure 10-2. VFE Functional Blocks and Modes of Operations                                    |     |

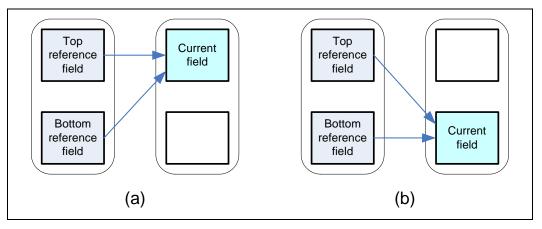

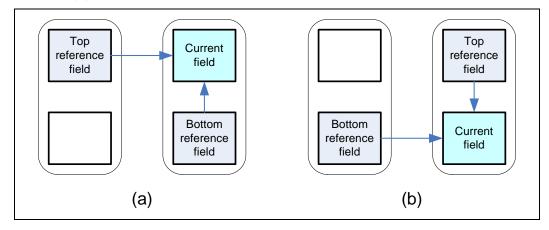

| Figure 10-3. Prediction for a P field picture that is a first field, which is (a) a top field |     |

| or (b) a bottom field                                                                         |     |

| Figure 10-4. Prediction for a P field picture that is a second field, which is (a) a top      |     |

| field, or (b) a bottom field                                                                  |     |

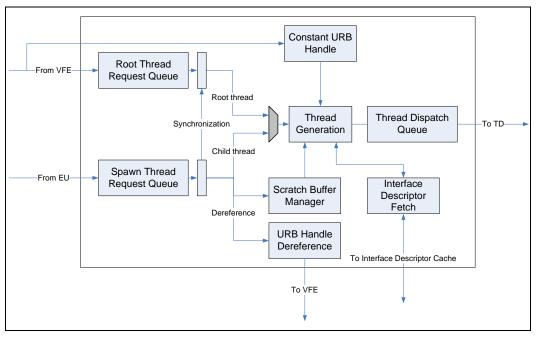

| Figure 10-5. Thread Spawner block diagram                                                     |     |

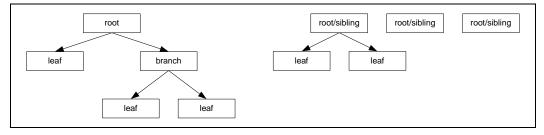

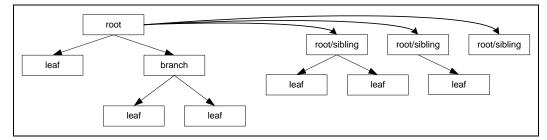

| Figure 10-6. Examples of thread relationship                                                  |     |

| Figure 10-7. An example of thread relationship with root sibling dependency                   |     |

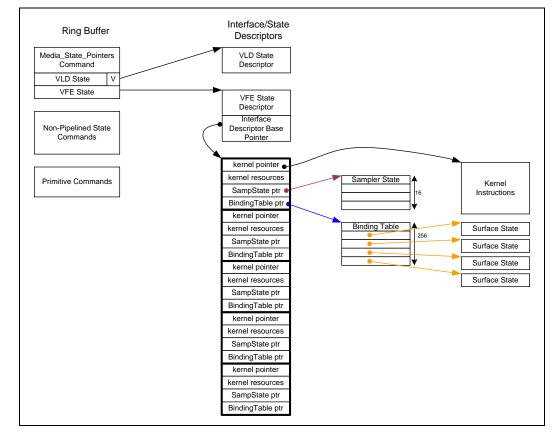

| Figure 10-8. Media State Model                                                                |     |

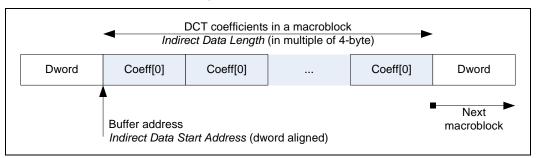

| Figure 10-9. Structure of the IDCT Compressed Data Buffer                                     |     |

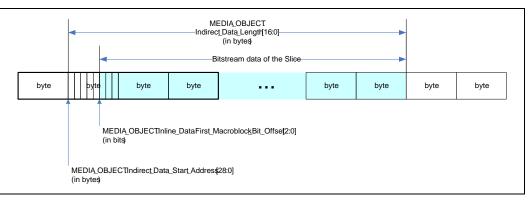

| Figure 10-10. Indirect data buffer for a slice                                                | 344 |

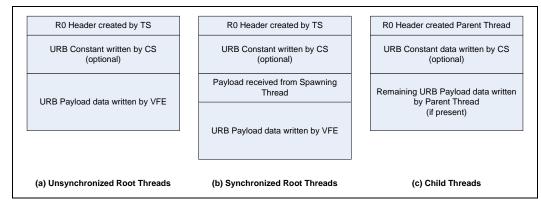

| Figure 10-11. Thread payload message formats for root and child threads                       | 344 |

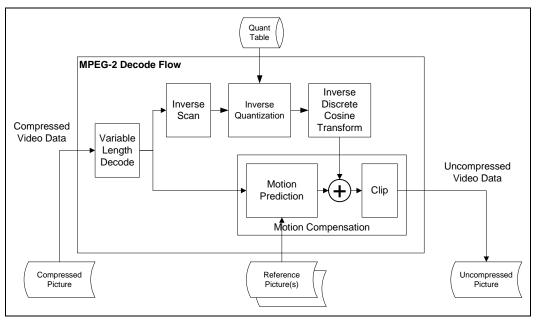

| Figure 10-12. MPEG-2 decode flow chart                                                        | 361 |

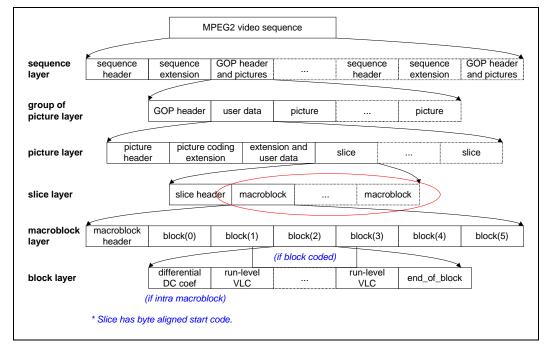

| Figure 10-13. MPEG-2 compressed bitstream syntax                                              |     |

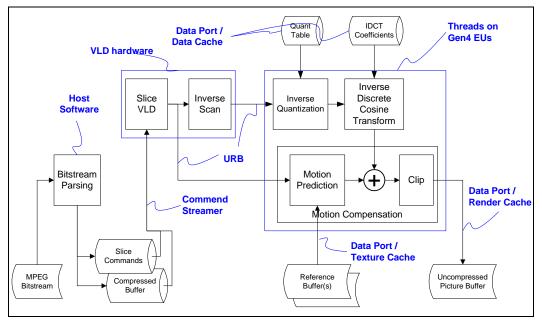

| Figure 10-14. Functional mapping of MPEG-2 decode hardware acceleration with of               |     |

| host VLD                                                                                      | 363 |

| Figure 10-15. Functional mapping of MPEG-2 decode hardware acceleration with                  |     |

| HWMC                                                                                          | 365 |

## Tables

| Table 1-1. Supported Chipsets13Table 2-1. 3D Primitive Topology Types28Table 2-2. VUE Vertex Header/UE Vertex Header43Table 2-3. State Variables Included in Thread Control Information58Table 2-4. Payload Sizes59Table 2-5. Fixed Payload Header Fields (non-FF-specific)62Table 2-6. State Variables Controlling Payload URB Data65Table 2-6. State Variables Controlling Payload URB Data65Table 2-7. Caches Invalidated/Flushed by PIPE_CONTROL Bit Settings71Table 3-1. 3D Primitive Topology Type Encoding.94Table 3-2. Source Element Formats supported in VF Unit.97Table 4-1. VS Thread Payload112Table 6-1. CLIP Thread Payload123Table 6-1. SF's Vertex Pipeline Inputs175Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions178Table 7-3. 3D Object Types178Table 7-4. Primitive Decomposition Outputs179Table 7-5. VPIndex/RTAIndex Selection180Table 7-6. Degenerate Objects197Table 7-7. Cull Mode259Table 9-1. Color Buffer Blend Color Factors277Table 9-2. Color Buffer Blend Functions278Table 10-3. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-4. Converting Frame-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for frame picture destination317Ta                                                                        |                                                                       |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----|

| Table 2-2. VUE Vertex HeaderVUE Vertex Header43Table 2-3. State Variables Included in Thread Control Information58Table 2-4. Payload Sizes59Table 2-5. Fixed Payload Header Fields (non-FF-specific)62Table 2-6. State Variables Controlling Payload URB Data65Table 2-7. Caches Invalidated/Flushed by PIPE_CONTROL Bit Settings71Table 3-1. 3D Primitive Topology Type Encoding94Table 3-2. Source Element Formats supported in VF Unit97Table 4-1. VS Thread Payload112Table 5-1. GS Thread Payload168Table 7-1. SF's Vertex Pipeline Inputs175Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions178Table 7-3. 3D Object Types179Table 7-4. Primitive Decomposition Outputs179Table 7-5. VPIndex/RTAIndex Selection180Table 7-5. Cull Mode198Table 7-7. Cull Mode198Table 9-1. Color Buffer Blend Color Factors277Table 9-2. Color Buffer Blend Functions278Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types313Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation for Pictures with Frame Motion Type314Table 10-4. Converting Field-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 4MV315Table 10-6. Macroblock indices for field picture destination317Table 10-7. Macroblock indices for field picture destination317 <t< td=""><td>Table 1-1. Supported Chipsets</td><td>13</td></t<> | Table 1-1. Supported Chipsets                                         | 13  |

| Table 2-3. State Variables Included in Thread Control Information58Table 2-4. Payload Sizes59Table 2-5. Fixed Payload Header Fields (non-FF-specific)62Table 2-6. State Variables Controlling Payload URB Data65Table 2-7. Caches Invalidated/Flushed by PIPE_CONTROL Bit Settings71Table 3-1. 3D Primitive Topology Type Encoding94Table 3-2. Source Element Formats supported in VF Unit97Table 3-1. GS Thread Payload112Table 5-1. GS Thread Payload123Table 6-1. CLIP Thread Payload168Table 7-1. SF's Vertex Pipeline Inputs175Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions178Table 7-3. 3D Object Types179Table 7-4. Primitive Decomposition Outputs179Table 7-5. VPIndex/RTAIndex Selection180Table 9-1. Color Buffer Blend Color Factors277Table 9-2. Color Buffer Blend Color Factors277Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-3. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-4. Converting Field-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-8. TS Resource Available in Device Hardware324Table 10-10. Subblock coding (bits [7:6] are reserved)341Table 10-111. Structure of a DCT coef                                             | Table 2-1. 3D Primitive Topology Types                                | 28  |

| Table 2-4.Payload Sizes59Table 2-5.Fixed Payload Header Fields (non-FF-specific)62Table 2-6.State Variables Controlling Payload URB Data65Table 2-7.Caches Invalidated/Flushed by PIPE_CONTROL Bit Settings.71Table 3-1.3D Primitive Topology Type Encoding.94Table 3-2.Source Element Formats supported in VF Unit97Table 4-1.VS Thread Payload112Table 5-1.GS Thread Payload123Table 6-1.CLIP Thread Payload168Table 7-1.SF's Vertex Pipeline Inputs175Table 7-2.SF-Supported Primitive Types & Vertex Count Restrictions178Table 7-3.3D Object Types178Table 7-4.Primitive Decomposition Outputs179Table 7-5.VPIndex/RTAIndex Selection180Table 7-6.Degenerate Objects197Table 7-7.Cull Mode198Table 9-1.Color Buffer Blend Color Factors277Table 9-2.Color Buffer Blend Functions278Table 9-3.Stencil Buffer Operation312Table 10-1.Summary of Motion Types313Table 10-2.Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3.Motion Comp Operation with Field Motion Type314Table 10-4.Converting Field-Dual Prime Motion to 4MV315Table 10-5.Converting Field-Dual Prime Motion to 2MV315Table 10-6.Macroblock indices for frame picture destination317 <tr< td=""><td>Table 2-2. VUE Vertex HeaderVUE Vertex Header</td><td>43</td></tr<>                                                                                                                                                           | Table 2-2. VUE Vertex HeaderVUE Vertex Header                         | 43  |

| Table 2-5. Fixed Payload Header Fields (non-FF-specific)62Table 2-6. State Variables Controlling Payload URB Data65Table 2-7. Caches Invalidated/Flushed by PIPE_CONTROL Bit Settings71Table 3-1. 3D Primitive Topology Type Encoding.94Table 3-2. Source Element Formats supported in VF Unit97Table 4-1. VS Thread Payload112Table 5-1. GS Thread Payload123Table 6-1. CLIP Thread Payload168Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions178Table 7-3. 3D Object Types178Table 7-4. Primitive Decomposition Outputs179Table 7-5. VPIndex/RTAIndex Selection180Table 7-6. Degenerate Objects197Table 7-7. Cull Mode198Table 9-1. Color Buffer Blend Color Factors277Table 10-2. Motion Comp Operations281Table 10-3. Stencil Buffer Operations281Table 10-4. Converting Frame-Dual Prime Motion to 2MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-8. TS Resource Available in Device Hardware324Table 10-9. Inline data in IS mode337Table 10-11. Structure of a DCT coefficient unit342Table 10-12. Ro header of a generic mode root thread345Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                               | Table 2-3. State Variables Included in Thread Control Information     | 58  |

| Table 2-6.State Variables Controlling Payload URB Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                       |     |

| Table 2-7. Caches Invalidated/Flushed by PIPE_CONTROL Bit Settings.71Table 3-1. 3D Primitive Topology Type Encoding.94Table 3-2. Source Element Formats supported in VF Unit97Table 4-1. VS Thread Payload.112Table 5-1. GS Thread Payload.123Table 6-1. CLIP Thread Payload.168Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions175Table 7-3. 3D Object Types178Table 7-4. Primitive Decomposition Outputs179Table 7-5. VPIndex/RTAIndex Selection.180Table 7-6. Degenerate Objects197Table 7-7. Cull Mode198Table 9-1. Color Buffer Blend Functions278Table 9-2. Color Buffer Blend Functions278Table 10-3. Stencil Buffer Operations281Table 10-4. Converting Frame-Dual Prime Motion to 4MV.315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-1. Structure of a DCT coefficient unit342Table 10-12. Ro header of a generic mode root thread345Table 10-13. Structure of a DCT coefficient unit342Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                       | Table 2-5. Fixed Payload Header Fields (non-FF-specific)              | 62  |

| Table 3-1. 3D Primitive Topology Type Encoding.94Table 3-2. Source Element Formats supported in VF Unit.97Table 4-1. VS Thread Payload.112Table 5-1. GS Thread Payload.123Table 6-1. CLIP Thread Payload.168Table 7-1. SF's Vertex Pipeline Inputs.175Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions178Table 7-3. 3D Object Types178Table 7-4. Primitive Decomposition Outputs.179Table 7-5. VPIndex/RTAIndex Selection.180Table 7-6. Degenerate Objects197Table 8-1. Variable Pixel Dispatch259Table 9-2. Color Buffer Blend Color Factors.277Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion to 4MV.315Table 10-4. Converting Frame-Dual Prime Motion to 2MV315Table 10-5. Converting Frame-Dual Prime Motion to 2MV317Table 10-7. Macroblock indices for frame picture destination317Table 10-8. TS Resource Available in Device Hardware324Table 10-9. Inline data in IS mode337Table 10-11. Structure of a DCT coefficient unit342Table 10-12. Ro header of a generic mode root thread345Table 10-13. Storemat of a block of DCT coefficients in GRF registers.355Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                       |                                                                       |     |

| Table 3-1. 3D Primitive Topology Type Encoding.94Table 3-2. Source Element Formats supported in VF Unit.97Table 4-1. VS Thread Payload.112Table 5-1. GS Thread Payload.123Table 6-1. CLIP Thread Payload.168Table 7-1. SF's Vertex Pipeline Inputs.175Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions178Table 7-3. 3D Object Types178Table 7-4. Primitive Decomposition Outputs.179Table 7-5. VPIndex/RTAIndex Selection.180Table 7-6. Degenerate Objects197Table 8-1. Variable Pixel Dispatch259Table 9-2. Color Buffer Blend Color Factors.277Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion to 4MV.315Table 10-4. Converting Frame-Dual Prime Motion to 2MV315Table 10-5. Converting Frame-Dual Prime Motion to 2MV317Table 10-7. Macroblock indices for frame picture destination317Table 10-8. TS Resource Available in Device Hardware324Table 10-9. Inline data in IS mode337Table 10-11. Structure of a DCT coefficient unit342Table 10-12. Ro header of a generic mode root thread345Table 10-13. Storemat of a block of DCT coefficients in GRF registers.355Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                       | Table 2-7. Caches Invalidated/Flushed by PIPE_CONTROL Bit Settings    | 71  |

| Table 4-1. VS Thread Payload112Table 5-1. GS Thread Payload123Table 6-1. CLIP Thread Payload168Table 7-1. SF's Vertex Pipeline Inputs175Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions178Table 7-3. 3D Object Types178Table 7-4. Primitive Decomposition Outputs179Table 7-5. VPIndex/RTAIndex Selection180Table 7-6. Degenerate Objects197Table 7-7. Cull Mode198Table 8-1. Variable Pixel Dispatch259Table 9-2. Color Buffer Blend Color Factors277Table 10-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation for Picture destination317Table 10-4. Converting Frame-Dual Prime Motion to 4MV.315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for field picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-9. Inline data in IS mode337Table 10-10. Subblock coding (bits [7:6] are reserved).341Table 10-11. Structure of a DCT coefficient unit342Table 10-12. RO header of a generic mode root thread345Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                        |                                                                       |     |

| Table 4-1. VS Thread Payload112Table 5-1. GS Thread Payload123Table 6-1. CLIP Thread Payload168Table 7-1. SF's Vertex Pipeline Inputs175Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions178Table 7-3. 3D Object Types178Table 7-4. Primitive Decomposition Outputs179Table 7-5. VPIndex/RTAIndex Selection180Table 7-6. Degenerate Objects197Table 7-7. Cull Mode198Table 8-1. Variable Pixel Dispatch259Table 9-2. Color Buffer Blend Color Factors277Table 10-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation for Picture destination317Table 10-4. Converting Frame-Dual Prime Motion to 4MV.315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for field picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-9. Inline data in IS mode337Table 10-10. Subblock coding (bits [7:6] are reserved).341Table 10-11. Structure of a DCT coefficient unit342Table 10-12. RO header of a generic mode root thread345Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                        | Table 3-2. Source Element Formats supported in VF Unit                | 97  |

| Table 6-1. CLIP Thread Payload.168Table 7-1. SF's Vertex Pipeline Inputs.175Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions.178Table 7-3. 3D Object Types.178Table 7-4. Primitive Decomposition Outputs.179Table 7-5. VPIndex/RTAIndex Selection.180Table 7-6. Degenerate Objects.197Table 7-7. Cull Mode198Table 8-1. Variable Pixel Dispatch259Table 9-2. Color Buffer Blend Color Factors.277Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion Type.314Table 10-4. Converting Frame-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-7. Macroblock indices for frame picture destination317Table 10-8. TS Resource Available in Device Hardware324Table 10-9. Inline data in IS mode337Table 10-10. Subblock coding (bits [7:6] are reserved)341Table 10-11. Structure of a DCT coefficient unit342Table 10-12. RO header of a generic mode root thread345Table 10-13. Format of a block of DCT coefficients in GRF registers.355Table 10-14. Use of GEN4 shared resources for post-VLD kernels.363                                                                                                                                                                                                 |                                                                       |     |

| Table 7-1. SF's Vertex Pipeline Inputs175Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions178Table 7-3. 3D Object Types178Table 7-4. Primitive Decomposition Outputs179Table 7-5. VPIndex/RTAIndex Selection180Table 7-6. Degenerate Objects197Table 7-7. Cull Mode198Table 8-1. Variable Pixel Dispatch259Table 9-2. Color Buffer Blend Color Factors277Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion Type314Table 10-5. Converting Frame-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-9. Inline data in IS mode337Table 10-10. Subblock coding (bits [7:6] are reserved)341Table 10-11. Structure of a DCT coefficient unit342Table 10-12. RO header of a generic mode root thread345Table 10-13. Format of a block of DCT coefficients in GRF registers355Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                                                                                                             | Table 5-1. GS Thread Payload                                          | 123 |

| Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions178Table 7-3. 3D Object Types178Table 7-4. Primitive Decomposition Outputs179Table 7-5. VPIndex/RTAIndex Selection180Table 7-6. Degenerate Objects197Table 7-7. Cull Mode198Table 8-1. Variable Pixel Dispatch259Table 9-2. Color Buffer Blend Color Factors277Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation for Picture Swith Frame Motion Type314Table 10-5. Converting Frame-Dual Prime Motion to 4MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-9. Inline data in IS mode337Table 10-10. Subblock coding (bits [7:6] are reserved)341Table 10-11. Structure of a DCT coefficient unit342Table 10-12. RO header of a generic mode root thread345Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                                                                                                                                                                                                               | Table 6-1. CLIP Thread Payload                                        | 168 |

| Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions178Table 7-3. 3D Object Types178Table 7-4. Primitive Decomposition Outputs179Table 7-5. VPIndex/RTAIndex Selection180Table 7-6. Degenerate Objects197Table 7-7. Cull Mode198Table 8-1. Variable Pixel Dispatch259Table 9-2. Color Buffer Blend Color Factors277Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation for Picture Swith Frame Motion Type314Table 10-5. Converting Frame-Dual Prime Motion to 4MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-9. Inline data in IS mode337Table 10-10. Subblock coding (bits [7:6] are reserved)341Table 10-11. Structure of a DCT coefficient unit342Table 10-12. RO header of a generic mode root thread345Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                                                                                                                                                                                                               | Table 7-1. SF's Vertex Pipeline Inputs                                | 175 |

| Table 7-3. 3D Object Types178Table 7-4. Primitive Decomposition Outputs179Table 7-4. Primitive Decomposition Outputs179Table 7-5. VPIndex/RTAIndex Selection180Table 7-6. Degenerate Objects197Table 7-7. Cull Mode198Table 8-1. Variable Pixel Dispatch259Table 9-2. Color Buffer Blend Color Factors277Table 9-2. Color Buffer Blend Functions278Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion Type314Table 10-4. Converting Frame-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-7. Macroblock indices for field picture destination317Table 10-8. TS Resource Available in Device Hardware324Table 10-10. Subblock coding (bits [7:6] are reserved)341Table 10-11. Structure of a DCT coefficient unit342Table 10-12. RO header of a generic mode root thread345Table 10-13. Format of a block of DCT coefficients in GRF registers363                                                                                                                                                                                                                                                                                                                                                                                                                  | Table 7-2. SF-Supported Primitive Types & Vertex Count Restrictions   | 178 |

| Table 7-5. VPIndex/RTAIndex Selection180Table 7-6. Degenerate Objects197Table 7-7. Cull Mode198Table 8-1. Variable Pixel Dispatch259Table 9-1. Color Buffer Blend Color Factors277Table 9-2. Color Buffer Blend Functions278Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion Type314Table 10-4. Converting Frame-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-7. Macroblock indices for field picture destination317Table 10-8. TS Resource Available in Device Hardware324Table 10-9. Inline data in IS mode337Table 10-11. Structure of a DCT coefficient unit342Table 10-12. RO header of a generic mode root thread345Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                       |     |

| Table 7-5. VPIndex/RTAIndex Selection180Table 7-6. Degenerate Objects197Table 7-7. Cull Mode198Table 8-1. Variable Pixel Dispatch259Table 9-1. Color Buffer Blend Color Factors277Table 9-2. Color Buffer Blend Functions278Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion Type314Table 10-4. Converting Frame-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-7. Macroblock indices for field picture destination317Table 10-8. TS Resource Available in Device Hardware324Table 10-9. Inline data in IS mode337Table 10-11. Structure of a DCT coefficient unit342Table 10-12. RO header of a generic mode root thread345Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table 7-4. Primitive Decomposition Outputs                            | 179 |

| Table 7-6. Degenerate Objects.197Table 7-7. Cull Mode198Table 8-1. Variable Pixel Dispatch259Table 9-1. Color Buffer Blend Color Factors.277Table 9-2. Color Buffer Blend Functions278Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion Type314Table 10-4. Converting Frame-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-9. Inline data in IS mode337Table 10-10. Subblock coding (bits [7:6] are reserved)341Table 10-11. Structure of a DCT coefficient unit342Table 10-13. Format of a block of DCT coefficients in GRF registers355Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                       |     |

| Table 8-1. Variable Pixel Dispatch259Table 9-1. Color Buffer Blend Color Factors277Table 9-2. Color Buffer Blend Functions278Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion Type314Table 10-4. Converting Frame-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-9. Inline data in IS mode337Table 10-10. Subblock coding (bits [7:6] are reserved)341Table 10-11. Structure of a DCT coefficient unit342Table 10-13. Format of a block of DCT coefficients in GRF registers355Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                       |     |

| Table 9-1. Color Buffer Blend Color Factors.277Table 9-2. Color Buffer Blend Functions.278Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion Type314Table 10-4. Converting Frame-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-8. TS Resource Available in Device Hardware324Table 10-9. Inline data in IS mode337Table 10-10. Subblock coding (bits [7:6] are reserved)341Table 10-11. Structure of a DCT coefficient unit342Table 10-13. Format of a block of DCT coefficients in GRF registers355Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Table 7-7. Cull Mode                                                  | 198 |

| Table 9-2. Color Buffer Blend Functions.278Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion Type314Table 10-4. Converting Frame-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-8. TS Resource Available in Device Hardware324Table 10-9. Inline data in IS mode337Table 10-10. Subblock coding (bits [7:6] are reserved)341Table 10-12. RO header of a generic mode root thread345Table 10-13. Format of a block of DCT coefficients in GRF registers353                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table 8-1. Variable Pixel Dispatch                                    | 259 |

| Table 9-3. Stencil Buffer Operations281Table 10-1. Summary of Motion Types312Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion Type314Table 10-4. Converting Frame-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-8. TS Resource Available in Device Hardware324Table 10-9. Inline data in IS mode337Table 10-10. Subblock coding (bits [7:6] are reserved)341Table 10-12. RO header of a generic mode root thread345Table 10-13. Format of a block of DCT coefficients in GRF registers355Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 9-1. Color Buffer Blend Color Factors                           | 277 |

| Table 10-1.Summary of Motion Types312Table 10-2.Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3.Motion Comp Operation with Field Motion Type314Table 10-4.Converting Frame-Dual Prime Motion to 4MV315Table 10-5.Converting Field-Dual Prime Motion to 2MV315Table 10-6.Macroblock indices for frame picture destination317Table 10-7.Macroblock indices for field picture destination317Table 10-8.TS Resource Available in Device Hardware324Table 10-9.Inline data in IS mode337Table 10-10.Subblock coding (bits [7:6] are reserved)341Table 10-12.R0 header of a generic mode root thread345Table 10-13.Format of a block of DCT coefficients in GRF registers355Table 10-14.Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Table 9-2. Color Buffer Blend Functions                               | 278 |

| Table 10-2. Motion Comp Operation for Pictures with Frame Motion Type313Table 10-3. Motion Comp Operation with Field Motion Type314Table 10-4. Converting Frame-Dual Prime Motion to 4MV315Table 10-5. Converting Field-Dual Prime Motion to 2MV315Table 10-6. Macroblock indices for frame picture destination317Table 10-7. Macroblock indices for field picture destination317Table 10-8. TS Resource Available in Device Hardware324Table 10-9. Inline data in IS mode337Table 10-10. Subblock coding (bits [7:6] are reserved)341Table 10-12. RO header of a generic mode root thread345Table 10-13. Format of a block of DCT coefficients in GRF registers355Table 10-14. Use of GEN4 shared resources for post-VLD kernels363                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Table 9-3. Stencil Buffer Operations                                  | 281 |