### Intel<sup>®</sup> Iris<sup>®</sup> X<sup>e</sup> MAX Graphics Open Source

### **Programmer's Reference Manual**

### For the 2020 Discrete GPU formerly named "DG1"

Volume 13: General Assets

February 2021, Revision 1.0

### **Notices and Disclaimers**

Intel technologies may require enabled hardware, software or service activation.

No product or component can be absolutely secure.

Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not "commercial" names and not intended to function as trademarks.

Customer is responsible for safety of the overall system, including compliance with applicable safetyrelated requirements or standards.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

### **Table of Contents**

| General Assets                                  | 1  |

|-------------------------------------------------|----|

| Discrete Graphics Memory Map Information        | 1  |

| MMIO                                            | 2  |

| Force Wake and Steering Table                   | 2  |

| Slice Registers and Die Recovery                | 11 |

| SW Virtualization Reserved MMIO range           | 11 |

| Register Address Maps                           | 11 |

| Graphics Register Address Map                   | 11 |

| VGA and Extended VGA Register Map               | 12 |

| Command Stream Programming                      | 15 |

| Introduction                                    | 15 |

| Workload Submission and Execution Status        | 16 |

| Commands and Programming Interface              | 27 |

| Command Batch Buffers                           | 27 |

| Context Management                              | 56 |

| Producer-Consumer Data ordering for MI Commands | 66 |

| Command Fetch                                   | 69 |

| Observability                                   | 70 |

| Observability Overview                          | 70 |

| GT Power-up/RC6 Exit                            | 71 |

| Render Engine Power-up                          | 71 |

| Media Engine Power-up                           | 71 |

| Resume from Partial GT Power Down               | 71 |

| Trace                                           | 71 |

| Interrupts                                      | 91 |

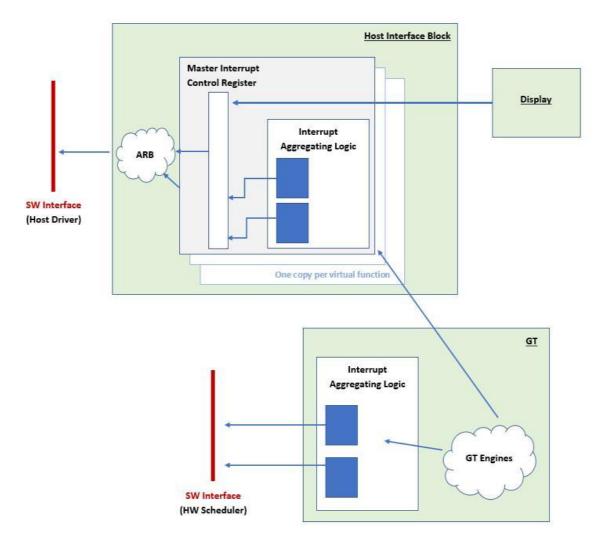

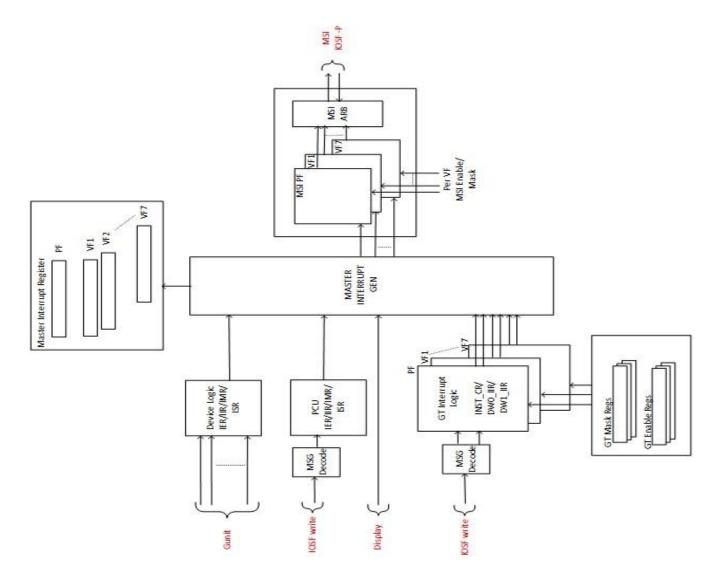

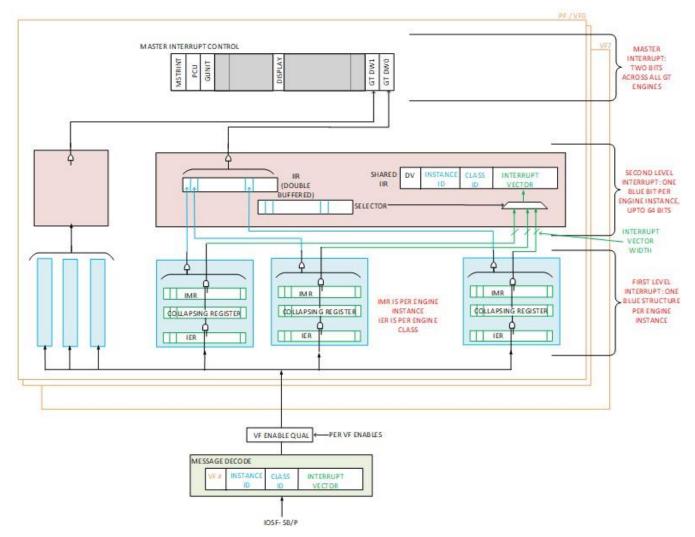

| Overview:                                       | 91 |

| GT Engine Interrupts:                           | 92 |

| Hardware Scheduler/MinIA SW Interface           | 93 |

| Host SW Interface                               | 94 |

| Interrupt Aggregating Logic                     | 95 |

### **General Assets**

This is the General Assets section.

### **Discrete Graphics Memory Map Information**

Intel graphics subsystem need certain \*reserved\* area in memory for various use case. Memory can be system memory for Integrated GFX or Local memory for discrete GFX. This chapter provides information on \*reserved\* area and provide general guideline for recommended size & location of memory.

During boot, for discrete graphics, a secure uController (like GSC) will program the memory map. Some of reserved area is also setup by drivers. Region size and placement is passed to graphics hardware and software via defined MMIO register locations. The general category of this reserved section of memory are:

- **D**ata **S**tolen **M**emory (DSM): Stolen memory used typically for pre-OS Display Frame buffers like in GOP/VBIOS and within Driver as general GFX memory. Note: Driver typically reuses this area for Frame Buffer compression (FBC)

- Write-Once-Protected-Content-Memory (WOPCM): Used for storing Authenticated FW like RC6 context, etc.

- **G**lobal Translation Table(GTT) **S**tolen **M**emory (GSM): Location of the Global Graphics Translation Table.

- Flat Compression Control Surface (Flat CCS): Compression table within Local memory.

- Local Memory Translation Table (LMTT): When virtualized, location of the local memory translation table.

PCIe MMIO Memory BARs :

- LMEMBAR :

o 64 bit prefetchable BAR

o The driver requests the OS to map the LMEMBAR range as memory type write-combining (ie. USWC) .. for performance reasons.

- GTTMMADR :

o 64 bit prefetchable BAR

o Uncacheable (ie. UC).

o GTTMMADR(Reg) : R/W will be 32 bit aligned and 32 bit (or less) in length. Driver requirement similar to prior art.

o GTTMMADR(GTT) : R/W will be 64 bit aligned and 64 bits (or less) in length. Driver requirement similar to prior art.

### ΜΜΙΟ

This is the MMIO chapter.

### Force Wake and Steering Table

Here is the Force Wake and Steering Table.

| MMIO Range<br>Start | MMIO Range<br>End | #<br>Bytes | Wake Target | Replicated<br>/<br>Multicast<br>? | Replication<br>Group<br>Type | Inst.<br>Count | Steering       |

|---------------------|-------------------|------------|-------------|-----------------------------------|------------------------------|----------------|----------------|

| 0000000             | 00000AFF          | 2816       |             |                                   |                              |                |                |

| 00000B00            | 00000BFF          | 256        | AON         | Yes                               | SQIDI                        | 2              | subsliceid[01] |

| 00000C00            | 00000DFF          | 512        | AON         | No                                | -                            | 1              | -              |

| 00000E00            | 00000FFF          | 512        | AON         | No                                | -                            | 1              | -              |

| 00001000            | 00001FFF          | 4096       | AON         | Yes                               | SQIDI                        | 2              | subsliceid[01] |

| 00002000            | 000026FF          | 1792       | RENDER      | No                                | -                            | 1              | -              |

| 00002700            | 000027FF          | 256        | GT          | No                                | -                            | 1              | -              |

| 00002800            | 00002AFF          | 768        | RENDER      | No                                | -                            | 1              | -              |

| 00002B00            | 00002FFF          | 1280       | GT          | No                                | -                            | 1              | -              |

| 00003000            | 00003FFF          | 4096       | RENDER      | No                                | -                            | 1              | -              |

| 00004000            | 000041FF          | 512        | GT          | No                                | -                            | 1              | -              |

| 00004200            | 000043FF          | 512        | GT          | No                                | -                            | 1              | -              |

| 00004400            | 000048FF          | 1280       | GT          | No                                | -                            | 1              | -              |

| 00004900            | 00004FFF          | 1792       |             |                                   |                              |                |                |

| 00005000            | 000051FF          | 512        |             |                                   |                              |                |                |

| 00005200            | 000052FF          | 256        | RENDER      | No                                | -                            | 1              | -              |

| 00005300            | 000053FF          | 256        | RENDER      | No                                | -                            | 1              | -              |

| 00005400            | 000054FF          | 256        |             |                                   |                              |                |                |

| 00005500            | 00005FFF          | 2816       | RENDER      | No                                | -                            | 1              | -              |

| 00006000            | 00006FFF          | 4096       | RENDER      | No                                | -                            | 1              | -              |

| 00007000            | 00007FFF          | 4096       | RENDER      | No                                | -                            | 1              | -              |

| 00008000            | 000080FF          | 256        | GT          | No                                | -                            | 1              | -              |

| 00008100            | 0000813F          | 64         | GT          | No                                | -                            | 1              | -              |

| 00008140            | 0000814F          | 16         | RENDER      | No                                | -                            | 1              | -              |

| 00008150            | 0000815F          | 16         | RENDER      | Yes                               | DSS                          | 6              | subsliceid[05] |

| 00008160            | 0000817F          | 32         |             |                                   |                              |                |                |

| 00008180            | 000081FF          | 128        | AON         | No                                | -                            | 1              | -              |

| 00008200            | 000082FF          | 256        | GT          | No                                | -                            | 1              | -              |

| 00008300            | 000084FF          | 512        | RENDER      | No                                | -                            | 1              | -              |

| 00008500            | 000085FF          | 256        | GT          | No                                | -                            | 1              | -              |

| 00008600 | 000086FF | 256   | GT     | No  | -      | 1 | -              |

|----------|----------|-------|--------|-----|--------|---|----------------|

| 00008700 | 000087FF | 256   | GT     | Yes | SQIDI  | 2 | subsliceid[01] |

| 0008800  | 00008FFF | 2048  |        |     |        |   |                |

| 00009000 | 000093FF | 1024  | GT     | No  | -      | 1 | -              |

| 00009400 | 0000947F | 128   | GT     | No  | -      | 1 | -              |

| 00009480 | 000094CF | 80    |        |     |        |   |                |

| 000094D0 | 0000951F | 80    | RENDER | No  | -      | 1 | -              |

| 00009520 | 0000955F | 64    | RENDER | Yes | DSS    | 6 | subsliceid[05] |

| 00009560 | 000095FF | 160   | AON    | No  | -      | 1 | -              |

| 00009600 | 000097FF | 512   |        |     |        |   |                |

| 00009800 | 00009FFF | 2048  | GT     | No  | -      | 1 | -              |

| 0000A000 | 0000AFFF | 4096  | GT     | No  | -      | 1 | -              |

| 0000B000 | 0000B0FF | 256   | RENDER | No  | -      | 1 | -              |

| 0000B100 | 0000B3FF | 768   | RENDER | Yes | L3BANK | 8 | subsliceid[07] |

| 0000B400 | 0000B47F | 128   | GT     | No  | -      | 1 | -              |

| 0000B480 | 0000BFFF | 2944  |        |     |        |   |                |

| 0000C000 | 0000C7FF | 2048  | GT     | No  | -      | 1 | -              |

| 0000C800 | 0000CFFF | 2048  | GT     | No  | -      | 1 | -              |

| 0000D000 | 0000D3FF | 1024  | AON    | No  | -      | 1 | -              |

| 0000D400 | 0000D7FF | 1024  | AON    | No  | -      | 1 | -              |

| 0000D800 | 0000D8FF | 256   | RENDER | No  | -      | 1 | -              |

| 0000D900 | 0000DBFF | 768   | GT     | No  | -      | 1 | -              |

| 0000DC00 | 0000DDFF | 512   | RENDER | No  | -      | 1 | -              |

| 0000DE00 | 0000DE7F | 128   |        |     |        |   |                |

| 0000DE80 | 0000DEFF | 128   | RENDER | Yes | DSS    | 6 | subsliceid[05] |

| 0000DF00 | 0000DFFF | 256   | RENDER | Yes | DSS    | 6 | subsliceid[05] |

| 0000E000 | 0000E0FF | 256   | RENDER | Yes | DSS    | 6 | subsliceid[05] |

| 0000E100 | 0000E1FF | 256   | RENDER | Yes | DSS    | 6 | subsliceid[05] |

| 0000E200 | 0000E3FF | 512   | RENDER | Yes | DSS    | 6 | subsliceid[05] |

| 0000E400 | 0000E7FF | 1024  | RENDER | Yes | DSS    | 6 | subsliceid[05] |

| 0000E800 | 0000E8FF | 256   | RENDER | Yes | DSS    | 6 | subsliceid[05] |

| 0000E900 | 0000EFFF | 1792  |        |     |        |   |                |

| 0000F000 | 0000F0FF | 256   | GT     | No  | -      | 1 | -              |

| 0000F100 | 0000FFFF | 3840  | GT     | No  | -      | 1 | -              |

| 00010000 | 000147FF | 18432 |        |     |        |   |                |

| 00014800 | 00014FFF | 2048  | RENDER | No  | -      | 1 | -              |

| 00015000 | 00016DFF | 7680  |        |     |        |   |                |

| 00016E00 | 00016FFF | 512   | RENDER | No  | -      | 1 | -              |

| 00017000 | 00017FFF | 4096  | RENDER | No  | -      | 1 | -              |

| 00018000 | 00019FFF | 8192  | RENDER | No  | -   | 1 | -              |

|----------|----------|-------|--------|-----|-----|---|----------------|

| 0001A000 | 0001BFFF | 8192  | RENDER | No  | -   | 1 | -              |

| 0001C000 | 0001DFFF | 8192  |        |     |     |   |                |

| 0001E000 | 0001FFFF | 8192  |        |     |     |   |                |

| 00020000 | 00020FFF | 4096  | VD0    | No  | -   | 1 | -              |

| 00021000 | 00021FFF | 4096  | VD2    | No  | -   | 1 | -              |

| 00022000 | 00022FFF | 4096  | GT     | No  | -   | 1 | -              |

| 00023000 | 00023FFF | 4096  | GT     | No  | -   | 1 | -              |

| 00024000 | 0002407F | 128   | AON    | No  | -   | 1 | -              |

| 00024080 | 0002417F | 256   |        |     |     |   |                |

| 00024180 | 000241FF | 128   | GT     | No  | -   | 1 | -              |

| 00024200 | 000249FF | 2048  |        |     |     |   |                |

| 00024A00 | 00024A7F | 128   | RENDER | Yes | DSS | 6 | subsliceid[05] |

| 00024A80 | 000251FF | 1920  |        |     |     |   |                |

| 00025200 | 0002527F | 128   | GT     | No  | -   | 1 | -              |

| 00025280 | 000252FF | 128   | GT     | No  | -   | 1 | -              |

| 00025300 | 000255FF | 768   |        |     |     |   |                |

| 00025600 | 0002567F | 128   | VD0    | No  | -   | 1 | -              |

| 00025680 | 000256FF | 128   | VD2    | No  | -   | 1 | -              |

| 00025700 | 000259FF | 768   |        |     |     |   |                |

| 00025A00 | 00025A7F | 128   | VD0    | No  | -   | 1 | -              |

| 00025A80 | 00025AFF | 128   | VD2    | No  | -   | 1 | -              |

| 00025B00 | 00025FFF | 1280  |        |     |     |   |                |

| 00026000 | 00027FFF | 8192  |        |     |     |   |                |

| 00028000 | 0002FFFF | 32768 |        |     |     |   |                |

| 00030000 | 0003FFFF | 65536 | GT     | No  | -   | 1 | -              |

| MMIO Range   | MMIO Range      | #                    |                    | Replicated<br>/<br>Multicast | Replication<br>Group | Inst. |          |

|--------------|-----------------|----------------------|--------------------|------------------------------|----------------------|-------|----------|

| <b>Start</b> | End<br>001C07FF | <b>Bytes</b><br>2048 | Wake Target<br>VD0 | ?                            | Туре                 | Count | Steering |

| 001C0000     |                 | 2048                 | VD0<br>VD0         | No                           | -                    | 1     | -        |

| 001C0800     | 001C0FFF        |                      |                    | No                           | -                    | 1     | -        |

| 001C1000     | 001C1FFF        | 4096                 | VD0                | No                           | -                    | 1     | -        |

| 001C2000     | 001C27FF        | 2048                 | VD0                | No                           | -                    | 1     | -        |

| 001C2800     | 001C2AFF        | 768                  | VD0                | No                           | -                    | 1     | -        |

| 001C2B00     | 001C2BFF        | 256                  | VD0                | No                           | -                    | 1     | -        |

| 001C2C00     | 001C2CFF        | 256                  |                    |                              |                      |       |          |

| 001C2D00     | 001C2DFF        | 256                  | VD0                | No                           | -                    | 1     | -        |

| 001C2E00     | 001C3EFF        | 4352                 |                    |                              |                      |       |          |

| 001C3F00     | 001C3FFF        | 256                  | VD0                | No                           | -                    | 1     | -        |

| 001C4000     | 001C47FF        | 2048                 |                    |                              |                      |       |          |

| 001C4800     | 001C4FFF        | 2048                 |                    |                              |                      |       |          |

| 001C5000     | 001C5FFF        | 4096                 |                    |                              |                      |       |          |

| 001C6000     | 001C67FF        | 2048                 |                    |                              |                      |       |          |

| 001C6800     | 001C6AFF        | 768                  |                    |                              |                      |       |          |

| 001C6B00     | 001C6BFF        | 256                  |                    |                              |                      |       |          |

| 001C6C00     | 001C6CFF        | 256                  |                    |                              |                      |       |          |

| 001C6D00     | 001C6DFF        | 256                  |                    |                              |                      |       |          |

| 001C6E00     | 001C7EFF        | 4352                 |                    |                              |                      |       |          |

| 001C7F00     | 001C7FFF        | 256                  |                    |                              |                      |       |          |

| 001C8000     | 001C9FFF        | 8192                 | VE0                | No                           | -                    | 1     | -        |

| 001CA000     | 001CA0FF        | 256                  | VE0                | No                           | -                    | 1     | -        |

| 001CA100     | 001CBEFF        | 7680                 |                    |                              |                      |       |          |

| 001CBF00     | 001CBFFF        | 256                  | VE0                | No                           | -                    | 1     | -        |

| 001CC000     | 001CCFFF        | 4096                 | VD0                | No                           | -                    | 1     | -        |

| 001CD000     | 001CDFFF        | 4096                 |                    |                              |                      |       |          |

| 001CE000     | 001CEFFF        | 4096                 |                    |                              |                      |       |          |

| 001CF000     | 001CFFFF        | 4096                 |                    |                              |                      |       |          |

| 001D0000     | 001D07FF        | 2048                 | VD2                | No                           | _                    | 1     | -        |

| 001D0800     | 001D0FFF        | 2048                 | VD2                | No                           | _                    | 1     | -        |

| 001D1000     | 001D1FFF        | 4096                 | VD2                | No                           | -                    | 1     | _        |

| 001D2000     | 001D27FF        | 2048                 | VD2                | No                           | _                    | 1     | -        |

| 001D2800     | 001D2AFF        | 768                  | VD2                | No                           | -                    | 1     | -        |

| 001D2B00     | 001D2BFF        | 256                  | VD2                | No                           | -                    | 1     | -        |

| 001D2C00     | 001D2CFF        | 256                  |                    |                              |                      |       |          |

| 001D2E00         001D3FFF         4352         No         1           001D3F00         001D3FFF         256         VD2         No         -         1         -           001D4000         001D4FFF         2048             -           001D5000         001D5FFF         4096              -          -              -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 001D2D00 | 001D2DFF | 256  | VD2 | No | - | 1 | - |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|------|-----|----|---|---|---|

| 001D3F00         001D3FFF         256         VD2         No         -         1         -           001D4000         001D47FF         2048                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |          |      | 102 | NO | _ | 1 |   |

| 001D4000         001D47FF         2048             001D5000         001D5FFF         4096             001D5000         001D5FFF         4096             001D6800         001D6AFF         2048              001D6800         001D6AFF         768               001D6000         001D6FF         256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |          | 1    | VD2 | No |   | 1 | _ |

| 001D4800         001D4FFF         2048              001D5000         001D5FFF         4096               001D6000         001D6AFF         2648                001D6800         001D6AFF         256                                                                                          <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |          |      | 102 | NO |   | 1 |   |

| 001D5000         001D5FFF         4096              001D6000         001D67FF         2048              001D6800         001D68FF         256              001D6000         001D60FF         256              001D6000         001D60FF         256              001D6000         001D60FF         256              001D6000         001D7FF         256               001D7F00         001D7FF         256                001DA000         001D8FF         7680                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |          |      |     |    |   |   |   |

| 001D6000         001D67FF         2048              001D6800         001D6AFF         768              001D6000         001D6CFF         256               001D6C00         001D6CFF         256                001D6C00         001D6FF         256 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |          |      |     |    |   |   |   |

| 001D6800         001D6AFF         768              001D6800         001D6BFF         256 <td></td> <td></td> <td>1</td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |          | 1    |     |    |   |   |   |

| 001D6B00         001D6BFF         256             001D6C00         001D6CFF         256              001D6D00         001D6DFF         256               001D6E00         001D7FFF         4352 <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |          |      |     |    |   |   |   |

| 001D6C00         001D6CFF         256            001D6D00         001D6DFF         256             001D6E00         001D7FF         4352              001D8000         001D7FF         256               001D8000         001D8FF         8192                001DA000         001D8FF         256 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |          |      |     |    |   |   |   |

| 001D6D00         001D6DFF         256             001D6E00         001D7EFF         4352              001D7F00         001D7FFF         256               001D8000         001D9FFF         8192                001DA000         001DA0FF         256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |          |      |     |    |   |   |   |

| 001D6E00         001D7FFF         4352             001D7F00         001D7FFF         256              001D8000         001D9FFF         8192               001DA000         001DA0FF         256                001DA000         001DBFFF         256                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |          |      |     |    |   |   |   |

| 001D7F00         001D7FFF         256              001D8000         001D9FFF         8192               001DA000         001DA0FF         256                                                                                                    <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |          |      |     |    |   |   |   |

| 001D8000         001D9FFF         8192            001DA000         001DA0FF         256             001DA100         001DBEFF         7680              001DA100         001DBFFF         256               001DBF00         001DFFFF         16384                001E0000         001E0FFF         2048                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |          |      |     |    |   |   |   |

| 001DA000         001DA0FF         256             001DA100         001DBEFF         7680              001DBF00         001DBFFF         256                                                                                                      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |          |      |     |    |   |   |   |

| 001DA100         001DBFFF         7680            001DBF00         001DBFFF         256             001DC000         001DFFFF         16384              001E0000         001E0FFF         2048               001E0800         001E0FFF         2048                001E1000         001E1FFF         2048                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |          | ł    |     |    |   |   |   |

| 001DBF00         001DBFFF         256              001DC000         001DFFFF         16384 </td <td></td> <td></td> <td>1</td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |          | 1    |     |    |   |   |   |

| 001DC000         001DFFFF         16384              001E0000         001E07FF         2048                                                                                                             <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |          | ł    |     |    |   |   |   |

| 001E0000         001E07FF         2048              001E0800         001E0FFF         2048               001E1000         001E1FFF         4096 <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |          |      |     |    |   |   |   |

| 001E0800         001E0FFF         2048              001E1000         001E1FFF         4096 </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |          |      |     |    |   |   |   |

| 001E1000         001E1FFF         4096              001E2000         001E27FF         2048 </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |          |      |     |    |   |   |   |

| 001E2000         001E27FF         2048              001E2800         001E2AFF         768 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |          |      |     |    |   |   |   |

| 001E2800         001E2AFF         768              001E2B00         001E2BFF         256 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |          |      |     |    |   |   |   |

| 001E2B00         001E2BFF         256             001E2C00         001E2CFF         256              001E2D00         001E2DFF         256               001E2D00         001E3EFF         4352                001E3F00         001E3FFF         256                                                                                   <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |          |      |     |    |   |   |   |

| 001E2C00         001E2CFF         256              001E2D00         001E2DFF         256 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |          |      |     |    |   |   |   |

| 001E2D00         001E2DFF         256             001E2E00         001E3EFF         4352 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |          |      |     |    |   |   |   |

| 001E2E00         001E3EFF         4352              001E3F00         001E3FFF         256 <td></td> <td></td> <td>1</td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |          | 1    |     |    |   |   |   |