# Intel<sup>®</sup> Open Source HD Graphics Programmers' Reference Manual (PRM)

### Volume 7: 3D Media GPGPU

For the 2014-2015 Intel Atom<sup>™</sup> Processors, Celeron<sup>™</sup> Processors and Pentium<sup>™</sup> Processors based on the "Cherry Trail/Braswell" Platform (Cherryview/Braswell graphics)

October 2015, Revision 1.1

## **Creative Commons License**

**You are free to Share** - to copy, distribute, display, and perform the work under the following conditions:

- **Attribution.** You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

- **No Derivative Works.** You may not alter, transform, or build upon this work.

## **Notices and Disclaimers**

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\* Other names and brands may be claimed as the property of others.

**Copyright © 2015, Intel Corporation. All rights reserved.**

## **Table of Contents**

| Registers in Render Engine                          | 1  |

|-----------------------------------------------------|----|

| Predication                                         | 2  |

| Predicate Render Registers                          | 2  |

| MI_SET_PREDICATE                                    | 3  |

| MI_PREDICATE                                        | 3  |

| Predicated Rendering Support in HW                  | 4  |

| Registers in Render Engine                          | 5  |

| Context Save Registers                              | 5  |

| VF Instance Count Registers                         | 5  |

| Mode and Misc Ctrl Registers                        | 6  |

| Pipelines Statistics Counter Registers              | 7  |

| AUTO_DRAW Registers                                 | 9  |

| MMIO Registers for GPGPU Indirect Dispatch          | 9  |

| CS ALU Programming and Design                       | 10 |

| CS ALU Programming and Design                       | 10 |

| Generic Purpose Registers                           | 10 |

| ALU BLOCK Diagram                                   | 11 |

| Instruction Set                                     | 12 |

| Instruction Format                                  | 12 |

| LOAD Operation                                      | 12 |

| Arithmetic/Logical Operations                       | 13 |

| STORE Operation                                     | 13 |

| Summary for ALU                                     | 13 |

| Summary of Instructions Supported                   | 14 |

| Table for ALU OPCODE Encodings                      | 14 |

| Table for Register Encodings                        | 16 |

| CS_GPR - Command Streamer General Purpose Registers | 16 |

| Memory Interface Commands for Rendering Engine      | 16 |

| State Commands                                      | 17 |

| STATE_BASE_ADDRESS                                  | 17 |

| Synchronization of the 3D Pipeline                  | 18 |

| Top-of-Pipe Synchronization                    |    |

|------------------------------------------------|----|

| End-of-Pipe Synchronization                    |    |

| Synchronization Actions                        |    |

| Writing a Value to Memory                      |    |

| PS_DEPTH_COUNT                                 | 20 |

| Generating an Interrupt                        | 20 |

| Invalidating of Caches                         | 20 |

| PIPE_CONTROL Command                           | 20 |

| PIPE_CONTROL                                   | 21 |

| Programming Restrictions for PIPE_CONTROL      |    |

| Post-Sync Operation                            | 23 |

| Flush Types                                    | 24 |

| Stall                                          | 24 |

| Render Logical Context Data                    | 25 |

| Overall Context Layout                         | 25 |

| Context Layout                                 | 25 |

| Register State Context                         | 26 |

| Register State Context                         | 27 |

| Ring Buffer                                    |    |

| Ring Context                                   |    |

| The Per-Process Hardware Status Page           |    |

| Render Engine Power Context                    |    |

| Command Ordering Rules                         |    |

| PIPELINE_SELECT                                | 43 |

| PIPE_CONTROL                                   | 43 |

| Common Pipeline State-Setting Commands         | 43 |

| 3D Pipeline-Specific State-Setting Commands    |    |

| Media Pipeline-Specific State-Setting Commands | 44 |

| 3DPRIMITIVE                                    | 44 |

| MEDIA_OBJECT                                   |    |

| Resource Streamer                              | 45 |

| Resource Streamer Sync Commands                | 45 |

| Introduction                                   |    |

| Glossary                                            | 46 |

|-----------------------------------------------------|----|

| Common Abbreviations                                | 46 |

| Theory of Operation                                 | 47 |

| Resource Streamer Functions                         | 47 |

| Detailed Resource Streamer Operations               | 49 |

| Introduction                                        | 49 |

| Resource Streamer Operation Descriptions            | 49 |

| Batch Processing                                    | 49 |

| Context Save                                        | 49 |

| HW Binding Table Image                              | 50 |

| Gather Push Constants Image                         | 50 |

| Push Constant Image                                 | 51 |

| HW Binding Table Generation                         | 52 |

| Gather Push Constants                               | 53 |

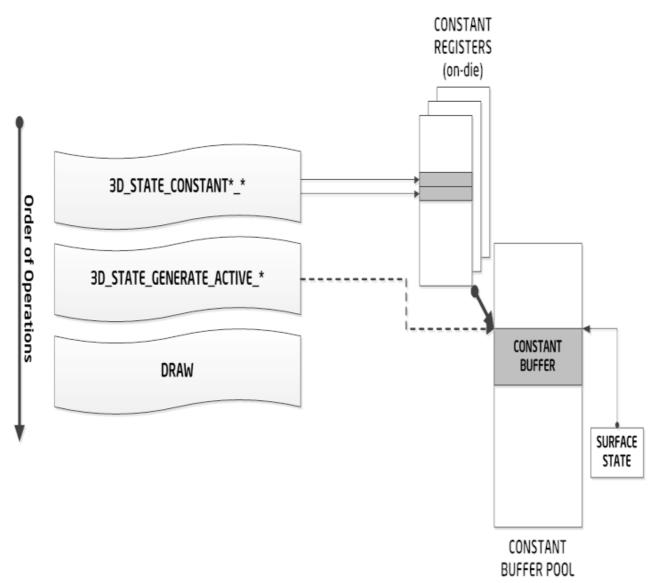

| Constant Buffer Generation (not DX9)                | 54 |

| Commands Actions in the RS                          | 55 |

| Resource Streamer Programming Guidelines            | 61 |

| RS Interactions with the 3D Command Streamer        | 61 |

| RS Interactions with Memory Requests                | 61 |

| Fundamental Programming and Operational Assumptions | 61 |

| Non-Operational Activities                          | 62 |

| Hardware Binding Tables                             | 62 |

| 3DSTATE_BINDING_TABLE_POOL_ALLOC [CHV, BSW]         | 63 |

| Gather Constants                                    | 64 |

| Dx9 Constant Buffer Generation                      | 65 |

| Vertex Shader Constant                              | 66 |

| Pixel Shader Constant                               | 67 |

| Shared Functions                                    | 68 |

| 3D Sampler                                          | 68 |

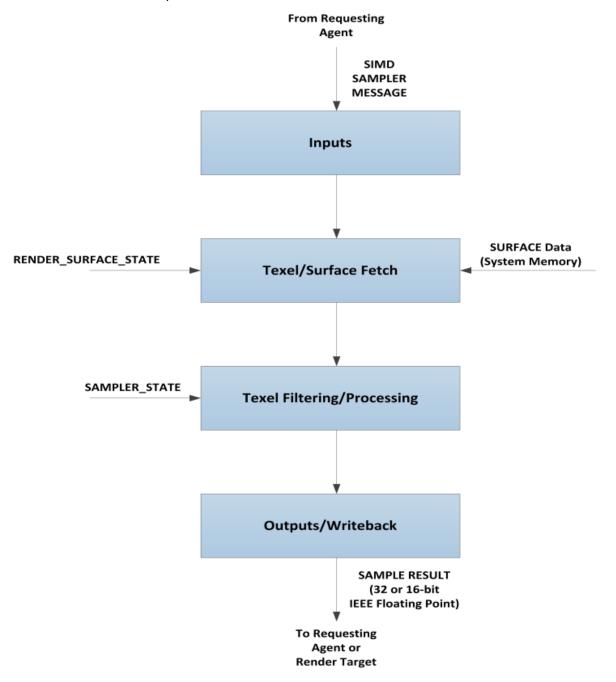

| Sampling Engine                                     | 69 |

| Texture Coordinate Processing                       | 71 |

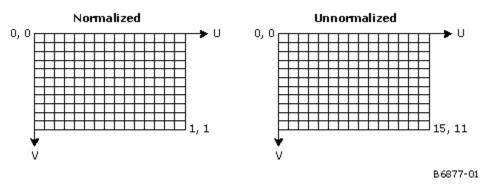

| Texture Coordinate Normalization                    | 71 |

| Texture Coordinate Computation                      | 71 |

| Texel Address Generation                 | 73 |

|------------------------------------------|----|

| Level of Detail Computation (Mipmapping) | 73 |

| Base Level Of Detail (LOD)               | 74 |

| LOD Bias                                 | 74 |

| LOD Pre-Clamping                         | 75 |

| Min/Mag Determination                    | 75 |

| LOD Computation Pseudocode               | 76 |

| Intra-Level Filtering Setup              | 77 |

| MAPFILTER_NEAREST                        |    |

| MAPFILTER_LINEAR                         |    |

| Bilinear Filter Sampling                 | 79 |

| MAPFILTER_ANISOTROPIC                    | 79 |

| MAPFILTER_MONO                           | 80 |

| Inter-Level Filtering Setup              |    |

| Texture Address Control                  |    |

| TEXCOORDMODE_MIRROR Mode                 |    |

| TEXCOORDMODE_MIRROR_ONCE Mode            | 85 |

| TEXCOORDMODE_WRAP Mode                   |    |

| TEXCOORDMODE_CLAMP Mode                  |    |

| TEXCOORDMODE_CLAMPBORDER Mode            |    |

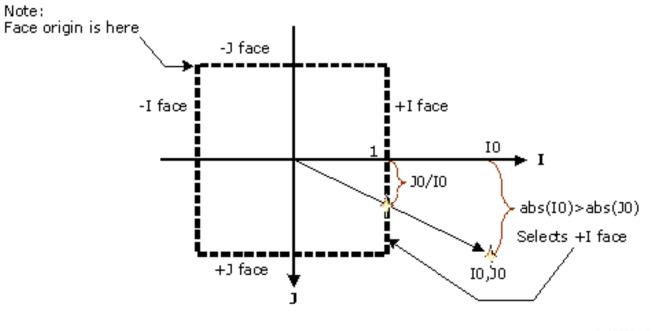

| TEXCOORDMODE_CUBE Mode                   |    |

| Texel Fetch                              |    |

| Texel Chroma Keying                      |    |

| Chroma Key Testing                       |    |

| Chroma Key Effects                       |    |

| Shadow Prefilter Compare                 |    |

| Texel Filtering                          |    |

| Texel Color Gamma Linearization          |    |

| Multisampled Surface Behavior            |    |

| Multisample Control Surface              |    |

| State                                    |    |

| Surface State Fetch                      |    |

| Sampler State Fetch                      | 93 |

| State Caching                                        | 94  |

|------------------------------------------------------|-----|

| SURFACE_STATE                                        | 94  |

| Sampler Output Channel Mapping                       | 96  |

| SURFACE_STATE for Deinterlace sample_8x8 and VME     | 102 |

| SAMPLER_STATE                                        | 103 |

| Border Color Programming for Integer Surface Formats | 104 |

| Messages                                             | 106 |

| Message Descriptor and Execution Mask                | 106 |

| Execution Mask                                       | 106 |

| Message Descriptor                                   | 106 |

| Message Header                                       | 107 |

| Parameter Types                                      | 111 |

| SIMD Payloads                                        | 112 |

| Writeback Message                                    | 114 |

| SIMD16                                               | 114 |

| Return Format = 32-bit                               | 114 |

| Return Format = 16-bit                               | 115 |

| SIMD8/SIMD8D                                         | 116 |

| Return Format = 32-bit                               | 116 |

| Return Format = 16-bit                               | 117 |

| SIMD4x2                                              | 118 |

| Shared Functions – Data Port                         | 119 |

| Data Cache                                           | 120 |

| Sampler Cache                                        | 121 |

| Surfaces                                             | 121 |

| Surface State Model                                  | 121 |

| Stateless Model                                      | 121 |

| Shared Local Memory (SLM)                            | 122 |

| Write Commit                                         | 123 |

| ReadWrite Ordering                                   | 123 |

| Accessing Buffers                                    | 124 |

| Accessing Media Surfaces                             | 125 |

| Boundary Behavior                                    | 125 |

| State                              |     |

|------------------------------------|-----|

| BINDING_TABLE_STATE                | 126 |

| SURFACE_STATE                      | 126 |

| COLOR_PROCESSING_STATE             | 126 |

| Messages                           | 127 |

| Global Definitions                 | 127 |

| Data Port Messages                 | 127 |

| Message Descriptor                 | 130 |

| Message Descriptor                 | 130 |

| Message Header                     | 133 |

| Write Commit Writeback Message     | 134 |

| OWord Block ReadWrite              | 134 |

| Message Descriptor                 | 136 |

| Message Payload (Write)            | 136 |

| Writeback Message (Read)           | 137 |

| Unaligned OWord Block Read         | 137 |

| Message Descriptor                 | 138 |

| Writeback Message (Read)           | 138 |

| OWord Dual Block ReadWrite         | 139 |

| Message Descriptor                 | 140 |

| Message Payload                    | 141 |

| Additional Message Payload (Write) | 141 |

| Writeback Message (Read)           | 142 |

| Media Block ReadWrite              | 142 |

| Message Descriptor                 | 144 |

| Message Header                     | 146 |

| Message Payload (Write)            | 149 |

| Writeback Message (Read)           | 150 |

| DWord Scattered ReadWrite          | 150 |

| Message Descriptor                 | 151 |

| Message Payload                    | 151 |

| Additional Message Payload (Write) | 152 |

| Writeback Message (Read)           | 152 |

| Message Descriptor                                               |     |

|------------------------------------------------------------------|-----|

| Message Payload                                                  |     |

| Source Payload                                                   |     |

| Writeback Message                                                | 155 |

| Byte Scattered ReadWrite                                         |     |

| Message Descriptor                                               |     |

| Message Payload                                                  |     |

| Additional Message Payload (Write)                               |     |

| Writeback Message (Read)                                         |     |

| TypedUntyped Surface ReadWrite and TypedUntyped Atomic Operation |     |

| Typed Surface ReadWrite Message Descriptor                       |     |

| Typed Surface Read/Write Message Descriptor                      |     |

| Untyped Surface ReadWrite Message Descriptor                     |     |

| Typed Atomic Operation Message Descriptor                        |     |

| Typed Atomic Operation SIMD4x2 Message Descriptor                |     |

| Untyped Atomic Operation Message Descriptor                      |     |

| Untyped Atomic Operation SIMD4x2 Message Descriptor              | 172 |

| Atomic Counter Operation Message Descriptor                      |     |

| Atomic Counter Operation SIMD4x2 Message Descriptor              |     |

| Message Header                                                   |     |

| Message Payload                                                  |     |

| SIMD16 Address Payload                                           |     |

| SIMD16 Source Payload (Atomic Operation Message Only)            |     |

| SIMD16 Source Payload (AOP_CMPWR8B Only)                         |     |

| SIMD16 Write Data Payload (Write Message Only)                   |     |

| SIMD8 Address Payload                                            |     |

| SIMD8 Source Payload (Atomic Operation Message Only)             |     |

| SIMD8 Write Data Payload (Write Message Only)                    |     |

| SIMD8 Write Data Payload (Tile W Write Message Only)             |     |

| SIMD4x2 Address Payload                                          |     |

| SIMD4x2 Source Payload (Atomic Operation Message Only)           |     |

| SIMD4x2 Source Payload (AOP_CMPWR8B Only)                        |     |

| SIMD4x2 Write Data Payload (Write Message Only)                  |     |

| Writeback Message                                          | 185 |

|------------------------------------------------------------|-----|

| SIMD8 DWORD Read                                           | 186 |

| SIMD8 QWORD Read                                           |     |

| SIMD16 Read                                                | 187 |

| SIMD8 Read                                                 |     |

| SIMD8 Read (Tile W)                                        | 189 |

| SIMD4x2 Read                                               | 190 |

| SIMD16 Atomic Operation                                    | 191 |

| SIMD16 Atomic Operation (AOP_CMPWR8B Only)                 | 192 |

| SIMD8 Atomic Operation                                     | 193 |

| SIMD8 Atomic Operation (AOP_CMPWR8B Only)                  | 194 |

| SIMD4x2 Atomic Operation                                   | 195 |

| SIMD4x2 Atomic Operation (AOP_CMPWR8B Only)                | 195 |

| A64 Scattered Read or Write                                | 196 |

| Message Descriptor                                         | 197 |

| Message Address Payload                                    | 198 |

| Additional Message Payload (QWord Write)                   | 199 |

| Additional Message Payload (DWord Write)                   | 201 |

| Additional Message Payload (8 Byte Write)                  | 202 |

| Additional Message Payload (1 or 2 or 4 Byte Write)        | 203 |

| Writeback Message (QWord Read)                             | 203 |

| Writeback Message (DWord Read)                             | 204 |

| Writeback Message (8 Byte Read)                            | 206 |

| Writeback Message (1 or 2 or 4 Byte Read)                  | 206 |

| A64 Untyped Atomic Operation                               | 207 |

| A64 Untyped Atomic Operation Message Descriptor            | 209 |

| Message Payload                                            | 211 |

| SIMD8 Address Payload                                      | 212 |

| SIMD4x2 Address Payload                                    | 213 |

| SIMD8 Source Payload (QWORD Atomic Operation Message Only) | 214 |

| SIMD8 Source Payload (DWORD Atomic Operation Message Only) | 215 |

| SIMD8 Source Payload (AOP_CMPWR16B Only)                   | 216 |

| SIMD8 Source Payload (AOP_CMPWR8B Only)                    | 216 |

| SIMD4x2 Source Payload (QWORD Atomic Operation Message Only) | 217 |

|--------------------------------------------------------------|-----|

| SIMD4x2 Source Payload (DWORD Atomic Operation Message Only) | 218 |

| SIMD4x2 Source Payload (AOP_CMPWR16B Only)                   | 218 |

| SIMD4x2 Source Payload (AOP_CMPWR8B Only)                    | 219 |

| Writeback Message                                            | 219 |

| SIMD8 Atomic Operation (QWord)                               | 219 |

| SIMD8 Atomic Operation (DWord)                               | 220 |

| SIMD8 Atomic Operation (AOP_CMPWR16B Only)                   | 221 |

| SIMD8 Atomic Operation (AOP_CMPWR8B Only)                    | 222 |

| SIMD4x2 Atomic Operation (QWord)                             | 223 |

| SIMD4x2 Atomic Operation (DWord)                             | 223 |

| SIMD4x2 Atomic Operation (AOP_CMPWR16B Only)                 | 224 |

| SIMD4x2 Atomic Operation (AOP_CMPWR8B Only)                  | 224 |

| A64 Untyped Atomic Float Add Operation                       | 225 |

| Untyped Atomic Float Add Operation Message Descriptor        | 225 |

| Message Payload                                              | 226 |

| SIMD8 Address Payload                                        | 226 |

| SIMD8 Source Payload (QWORD Atomic Operation Message Only)   | 227 |

| SIMD8 Source Payload (DWORD Atomic Operation Message Only)   | 228 |

| Writeback Message                                            | 228 |

| A64 Untyped Surface Read or Write Operation                  | 228 |

| Untyped Surface Read or Write Message Descriptor             | 230 |

| Message Payload                                              | 230 |

| SIMD8 Address Payload                                        | 231 |

| SIMD4x2 Address Payload                                      | 232 |

| SIMD8 DWORD Write Data Payload (Write Message Only)          | 233 |

| SIMD4x2 DWORD Write Data Payload (Write Message Only)        | 234 |

| Writeback Message                                            | 234 |

| SIMD8 DWORD Read                                             | 235 |

| SIMD4x2 DWORD Read                                           | 236 |

| A64 Block Read or Write Operation                            | 236 |

| Message Descriptor                                           | 237 |

| Message Header                                               | 238 |

| Message Payload (OWord Write)                         | 239 |

|-------------------------------------------------------|-----|

| Writeback Message (OWord Read)                        | 239 |

| Writeback Message (Unaligned OWord Read)              | 239 |

| Message Payload (Dual OWord Write)                    | 240 |

| Writeback Message (Dual Oword Read)                   | 240 |

| Message Payload (HWord Write)                         | 241 |

| Writeback Message (HWord Read)                        | 241 |

| Untyped Atomic Float Add Operation                    | 241 |

| Untyped Atomic Float Add Operation Message Descriptor | 243 |

| Message Header                                        | 244 |

| Message Payload                                       | 245 |

| SIMD16 Address Payload                                | 245 |

| SIMD8 Address Payload                                 | 246 |

| SIMD16/SIMD8 DWORD Source Payload                     | 246 |

| SIMD16/SIMD8 QWORD Source Payload                     | 247 |

| Writeback Message                                     | 248 |

| SIMD16 SIMD8 DWORD Atomic Float Add                   | 248 |

| SIMD16/SIMD8 QWORD Atomic Float Add                   | 248 |

| Read Surface Info                                     | 249 |

| Message Descriptor                                    | 249 |

| Address Payload                                       | 249 |

| Writeback Message                                     | 249 |

| Transpose Read                                        | 251 |

| Message Descriptor                                    | 252 |

| Message Header                                        | 252 |

| Writeback Message                                     | 254 |

| Scratch Block Read or Write                           | 254 |

| Message Descriptor                                    | 255 |

| Message Header                                        | 256 |

| Message Payload (Write)                               | 256 |

| Message Payload (Read)                                | 256 |

| Writeback Message (Read)                              | 256 |

| Memory Fence                                          | 257 |

| Message Descriptor                          | 258 |

|---------------------------------------------|-----|

| Message Header                              | 259 |

| Writeback Message                           | 259 |

| Pixel Data Port                             |     |

| Cache Agents                                |     |

| Accessing Render Targets                    |     |

| Message Sequencing Summary                  |     |

| Single Source                               |     |

| Dual Source                                 |     |

| Replicate Data                              |     |

| Multiple Render Targets (MRT)               |     |

| Render Target Read and Write                |     |

| SubspanPixel to Slot Mapping                |     |

| Message Descriptor                          | 270 |

| Message Header                              | 270 |

| Message Header                              | 271 |

| Writeback Message (Read)                    | 272 |

| Header for SIMD8_IMAGE_WRITE                | 273 |

| Source 0 Alpha Payload                      | 277 |

| oMask Payload                               | 278 |

| Color Payload SIMD16 Single Source          | 279 |

| Color Payload                               | 279 |

| Color Payload SIMD8 Single Source           |     |

| Color Payload SIMD16 Replicated Data        |     |

| Color Payload SIMD8 Dual Source             |     |

| Render Target Read and Write                |     |

| Message Header                              |     |

| Shared Functions Pixel Interpolater         |     |

| Messages                                    |     |

| Initiating Message                          |     |

| Message Descriptor                          |     |

| "Per Message Offset" Message Descriptor     |     |

| "Sample Position Offset" Message Descriptor |     |

| "Centroid Position" and "Per Slot Offset" Message Descriptor |     |

|--------------------------------------------------------------|-----|

| Message Payload for Most Messages                            | 293 |

| SIMD8 Per Slot Offset Message Payload                        |     |

| SIMD16 Per Slot Offset Message Payload                       | 294 |

| Writeback Message                                            |     |

| SIMD8                                                        |     |

| SIMD16                                                       |     |

| Shared Functions - Unified Return Buffer (URB)               |     |

| URB Size                                                     |     |

| URB Access                                                   |     |

| State                                                        |     |

| FF_SYNC Messages                                             |     |

| FF_SYNC Message Header                                       |     |

| FF_SYNC Writeback Message                                    |     |

| URB Messages                                                 |     |

| Execution Mask                                               |     |

| Message Descriptor                                           |     |

| URB_WRITE and URB_READ                                       |     |

| Message Header                                               |     |

| URB_WRITE_HWORD Write Data Payload                           |     |

| URB_NOSWIZZLE                                                |     |

| URB_INTERLEAVED                                              |     |

| URB_READ_HWORD Writeback Message                             |     |

| URB_NOSWIZZLE                                                |     |

| URB_INTERLEAVED                                              |     |

| URB_WRITE_OWORD Write Data Payload                           |     |

| URB_NOSWIZZLE                                                |     |

| URB_INTERLEAVED                                              |     |

| URB_READ_OWORD Writeback Message                             |     |

| URB_NOSWIZZLE                                                |     |

| URB_INTERLEAVED                                              |     |

| URB_ATOMIC                                                   |     |

| Message Header                                               |     |

| Writeback Message                                      |  |

|--------------------------------------------------------|--|

| URB_SIMD8_Write and URB_SIMD8_Read                     |  |

| Message Descriptor                                     |  |

| Message Header                                         |  |

| Per Slot Offset Message Phase                          |  |

| Channel Mask Message Phase                             |  |

| Write Data Payload                                     |  |

| Writeback Message                                      |  |

| Message Gateway                                        |  |

| Messages                                               |  |

| Message Descriptor                                     |  |

| OpenGateway Message                                    |  |

| Message Payload                                        |  |

| Writeback Message to Requester Thread                  |  |

| CloseGateway Message                                   |  |

| Message Payload                                        |  |

| Writeback Message to Requester Thread                  |  |

| ForwardMsg Message                                     |  |

| Message Payload                                        |  |

| Writeback Message to Requester Thread                  |  |

| Writeback Message to Recipient Thread                  |  |

| GetTimeStamp Message                                   |  |

| Message Payload                                        |  |

| Writeback Message to Requester Thread                  |  |

| BarrierMsg Message                                     |  |

| Message Payload                                        |  |

| Writeback Message to Requester Thread                  |  |

| Broadcast Writeback Message                            |  |

| MMIOReadWrite Message                                  |  |

| Message Payload                                        |  |

| Writeback Message to Requester Thread (MMIO Read Only) |  |

| Media Sampler                                          |  |

| Shared Functions – Video Motion Estimation             |  |

| Theory of Operation                   |     |

|---------------------------------------|-----|

| Shape Decision                        |     |

| Minor Shape Decision Prior to FME     |     |

| Major Shape Decision Prior to FME     |     |

| Shape Update after FME                |     |

| Final Code Decision after BME         |     |

| Early Decisions                       |     |

| Surfaces                              |     |

| State                                 |     |

| BINDING_TABLE_STATE                   |     |

| SURFACE_STATE                         |     |

| VME_STATE                             |     |

| VME_SEARCH_PATH_LUT_STATE             |     |

| Software Interface – Bspec Highlights | 350 |

| Message Structure Overview            | 350 |

| IME and IDM Message Descriptor        | 351 |

| Input GRFs                            |     |

| Input Message Phases by Type          |     |

| Output GRFs                           |     |

| Output Message Phases by Type         | 354 |

| Binding Table Pointers                |     |

| Progressive Content                   |     |

| Interlaced Content                    |     |

| RDE Packet Mapping                    |     |

| Glossary of Messages                  |     |

| Universal Input Message Phases        |     |

| SIC Input Message Phases              |     |

| IME Input Message Phases              |     |

| FBR Input Message Phases              |     |

| IDM Input Message Phases              |     |

| Return Data Message Phases            |     |

| IME StreamOut                         | 408 |

| IDM Stream-Out                        |     |

| IDM16x16 Streamout Message Format                                |     |

|------------------------------------------------------------------|-----|

| IDM8x8 Streamout Message Format                                  | 410 |

| Sample_8x8 State                                                 |     |

| SURFACE_STATE for Deinterlace, sample_8x8, and VME               |     |

| SAMPLER_STATE for Sample_8x8 Message                             |     |

| Media Object Dispatch Pseudocode                                 |     |

| Calculate Residual Blocks Pseudocode                             |     |

| Dispatch Media Object Pseudocode                                 | 414 |

| SIMD32/64 Payload                                                | 414 |

| SIMD32 Payload                                                   | 414 |

| SIMD64 Payload                                                   |     |

| Vertical Block Number Restrictions                               |     |

| Payload Parameter Definition                                     |     |

| SIMD32_64 Message Descriptor                                     |     |

| SIMD32_64 Message Header                                         |     |

| Message Header                                                   |     |

| SIMD32_64 Payload Parameter Definition                           |     |

| SIMD32_64 Message Types                                          |     |

| Writeback Message                                                |     |

| SIMD32                                                           |     |

| Sample_unorm*                                                    |     |

| Cache_flush                                                      |     |

| Sample_8x8 Writeback Messages                                    |     |

| "16 bit Full" Output Format Control Mode                         | 434 |

| Sampler_8x8 – Writeback Message for Convolve and 1 Pixel Convolu |     |

| Sampler_8x8 – Writeback Message for MinMaxFilter                 |     |

| "16 Bit Full" Output Format Control Mode                         |     |

| "8 Bit Full" Output Format Control Mode:                         |     |

| Sampler_8x8 – Writeback Message for MinMax                       |     |

| Sampler_8x8 – Writeback Message for Dilate or Erode              |     |

| Sampler_8x8 – Writeback Message for Centroid                     |     |

| Sampler_8x8 – Writeback Message for BoolCentroid/BoolSum         |     |

| Sampler_8x8 – Writeback Message for AVS                          |     |

|                                                                  |     |

| "16 bit Full" Output Format Control Mode                    | 445 |

|-------------------------------------------------------------|-----|

| "16 Bit Chrominance Downsampled" Output Format Control Mode | 447 |

| "8 Bit Full" Output Format Control Mode                     | 449 |

| "8 Bit Chrominance Downsampled" Output Format Control Mode  | 450 |

| SIMD32 Surface State                                        | 452 |

| SIMD32 Sampler State                                        | 452 |

| 3D Pipeline Stages                                          | 452 |

| 3D Pipeline-Level State                                     | 453 |

| Statistics                                                  | 455 |

| Statistics Gathering                                        | 455 |

| 3D Pipeline Geometry                                        | 457 |

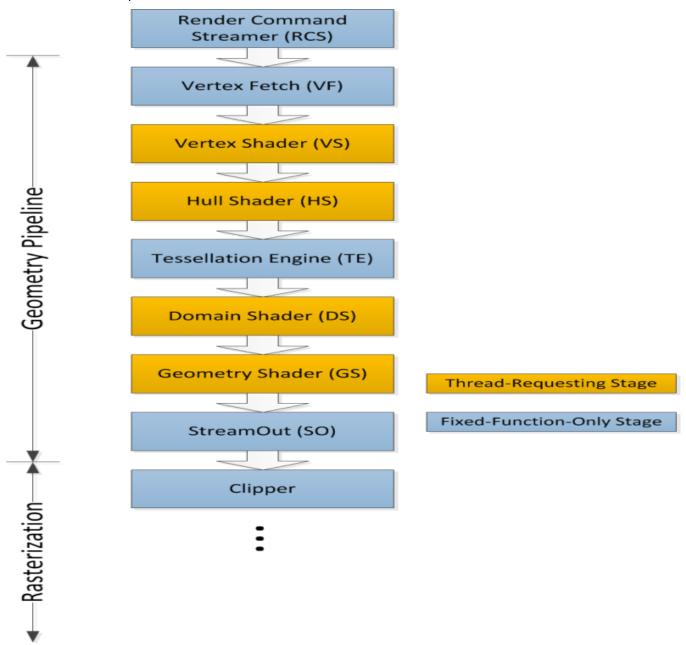

| Block Diagram                                               | 457 |

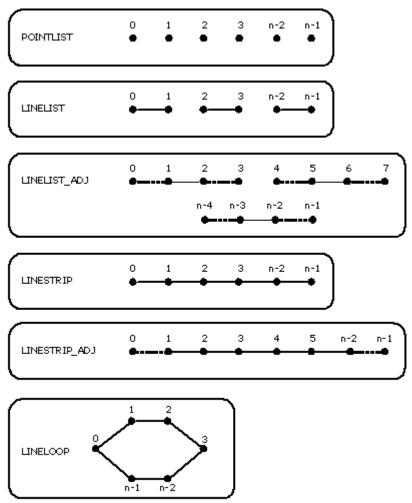

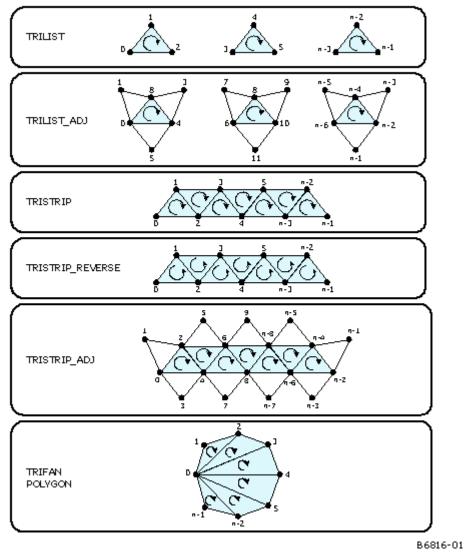

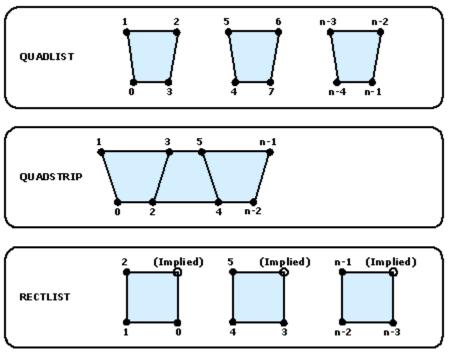

| 3D Primitives Overview                                      | 458 |

| Vertex Data Overview                                        | 466 |

| Vertex Positions                                            | 466 |

| Clip Space Position                                         | 467 |

| NDC Space Position                                          | 467 |

| Screen-Space Position                                       | 467 |

| Vertex Fetch (VF) Stage                                     | 468 |

| State                                                       | 468 |

| Control State                                               | 468 |

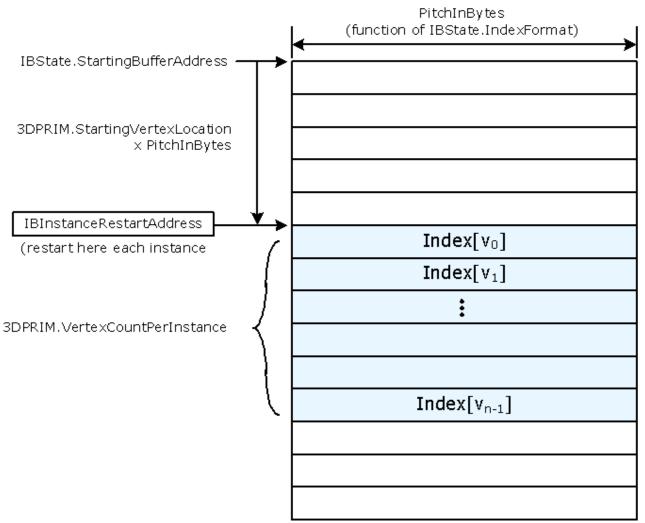

| Index Buffer (IB) State                                     | 468 |

| Vertex Buffers (VB) State                                   | 469 |

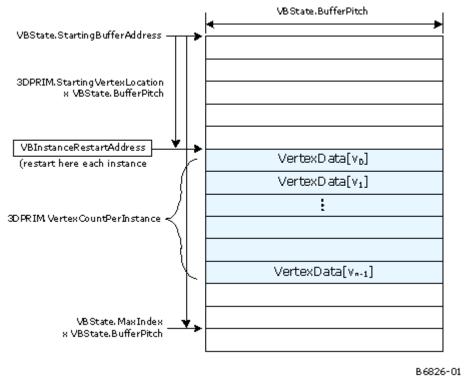

| VERTEXDATA Buffers – SEQUENTIAL Access                      | 469 |

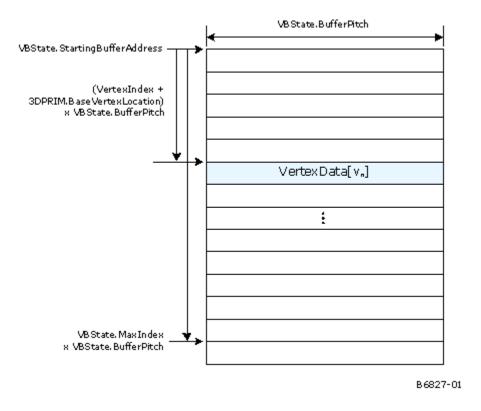

| VERTEXDATA Buffers – RANDOM Access                          | 470 |

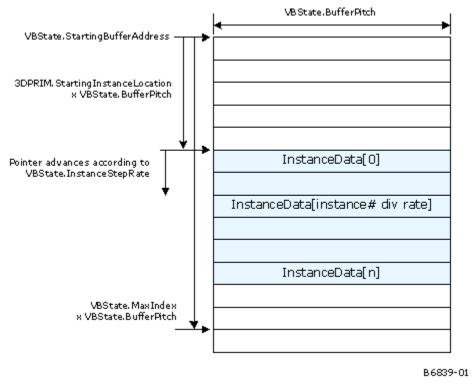

| INSTANCEDATA Buffers                                        | 471 |

| Vertex Definition State                                     | 472 |

| Input Vertex Definition                                     | 472 |

| 3D Primitive Command                                        | 473 |

| Functions                                                   | 473 |

| Input Assembly                                              | 473 |

| Vertex Assembly                                             | 473 |

| Vertex Cache                                                |     |

| Input Data: Push Model vs. Pull Model | 475 |

|---------------------------------------|-----|

| Generated IDs                         |     |

| 3D Primitive Processing               |     |

| Index Buffer Access                   |     |

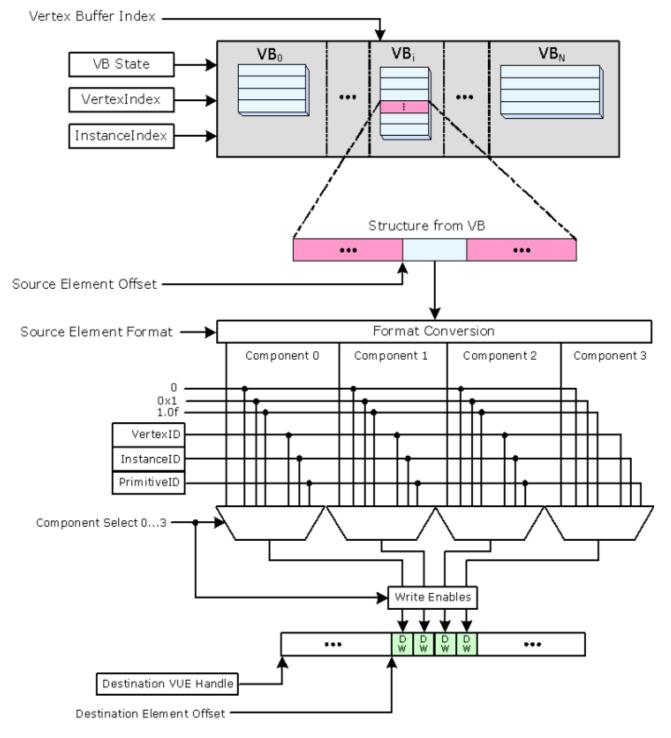

| Vertex Element Data Path              | 477 |

| FormatConversion                      |     |

| DestinationFormatSelection            |     |

| Dangling Vertex Removal               |     |

| Vertices Generated                    |     |

| Objects Generated                     |     |

| Vertex Shader (VS) Stage              |     |

| State                                 |     |

| Functions                             |     |

| Vertex Shader Cache (VS\$)            |     |

| SIMD4x2 VS Thread Request Generation  |     |

| SIMD4x2 VS Thread Execution           |     |

| VS Thread Dispatch Masks              |     |

| Vertex Output                         |     |

| Thread Termination                    |     |

| Primitive Output                      |     |

| Statistics Gathering                  |     |

| Payloads                              |     |

| SIMD4x2 Payload                       |     |

| SIMD8 Payload                         |     |

| Hull Shader (HS) Stage                |     |

| State                                 |     |

| Functions                             |     |

| Patch Object Staging                  |     |

| HS Thread Execution                   |     |

| HS Thread Dispatch Mask               |     |

| Patch URB Entry (Patch Record) Output |     |

| Please Provide Title                  |     |

| DOMAIN_POINT Structure                |     |

| Statistics Gathering               |  |

|------------------------------------|--|

| HS Invocations                     |  |

| Payloads                           |  |

| SINGLE_PATCH Payload               |  |

| Tessellation Engine (TE) Stage     |  |

| State                              |  |

| Functions                          |  |

| Patch Culling                      |  |

| Tessellation Factor Limits         |  |

| Partitioning                       |  |

| Domain Types and Output Topologies |  |

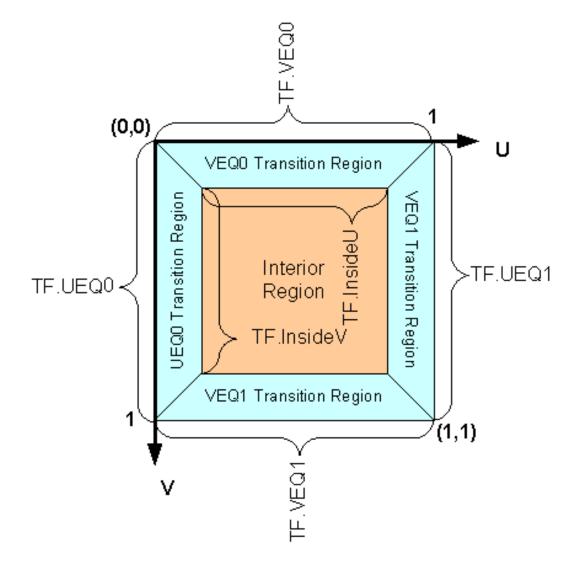

| QUAD Domain Tessellation           |  |

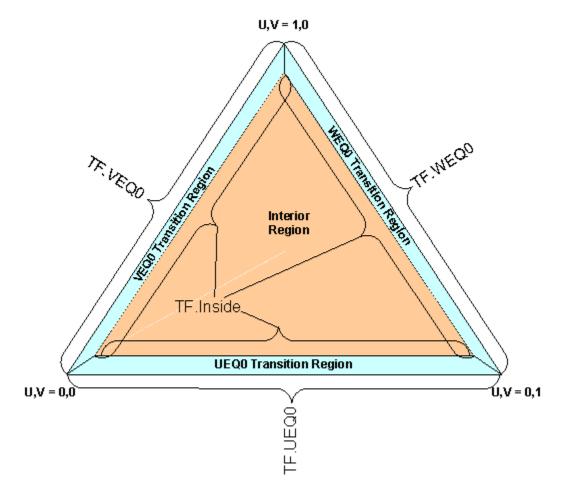

| TRI Domain Tessellation            |  |

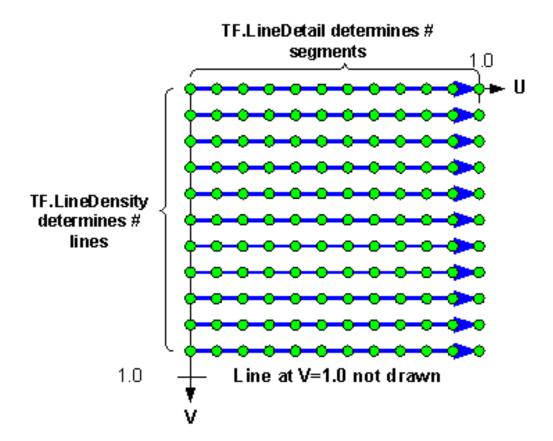

| ISOLINE Domain Tessellation        |  |

| Domain Shader (DS) Stage           |  |

| State                              |  |

| Functions                          |  |

| SIMD4x2 Thread Execution           |  |

| Statistics Gathering               |  |

| Payloads                           |  |

| SIMD4x2 Payload                    |  |

| SIMD8 Payload                      |  |

| Geometry Shader (GS) Stage         |  |

| GS Stage Overview                  |  |

| State                              |  |

| Functions                          |  |

| Object Staging                     |  |

| Thread Request Generation          |  |

| Object Vertex Ordering             |  |

| Thread Execution                   |  |

| Thread Execution                   |  |

| GS URB Entry                       |  |

| GS URB Entry - Output Vertex Count |  |

| GS Output Topologies              |     |

|-----------------------------------|-----|

| GS Output StreamID                |     |

| Primitive Output                  |     |

| Statistics Gathering              |     |

| Payloads                          |     |

| Thread Payload High-Level Layout  |     |

| SIMD 4x2 Thread Payload           |     |

| SIMD8 Thread Payload              | 534 |

| Thread Request Generation         | 541 |

| Thread Control Information        | 542 |

| Thread Payload Generation         | 543 |

| Fixed Payload Header              | 543 |

| Extended Payload Header           | 546 |

| Payload URB Data                  | 546 |

| Stream Output Logic (SOL) Stage   | 548 |

| State                             | 548 |

| Functions                         | 550 |

| Input Buffering                   | 550 |

| Stream Output Function            | 553 |

| Stream Output Buffers             | 554 |

| Rendering Disable                 | 554 |

| Statistics                        | 555 |

| 3D Pipeline Rasterization         | 555 |

| Common Rasterization State        | 555 |

| 3D Pipeline – CLIP Stage Overview | 556 |

| Clip Stage – 3D Clipping          | 556 |

| Fixed Function Clipper            | 556 |

| Concepts                          | 557 |

| CLIP Stage Input                  | 557 |

| State                             | 557 |

| VUE Readback                      | 558 |

| VertexClipTest Function           | 559 |

| Object Staging                    |     |

| Partial Object Removal                        |     |

|-----------------------------------------------|-----|

| ClipDetermination Function                    |     |

| ClipMode State                                | 564 |

| NORMAL ClipMode                               |     |

| CLIP_ALL ClipMode                             |     |

| CLIP_NON_REJECT ClipMode                      |     |

| REJECT_ALL ClipMode                           | 565 |

| ACCEPT_ALL ClipMode                           |     |

| Object Pass-Through                           | 566 |

| Primitive Output                              | 567 |

| Other Functionality                           |     |

| Statistics Gathering                          | 568 |

| CL_INVOCATION_COUNT                           | 568 |

| 3D Pipeline - Strips and Fans (SF) Stage      | 569 |

| Inputs from CLIP                              | 569 |

| Attribute Setup/Interpolation Process         | 570 |

| Attribute Setup/Interpolation Process         | 570 |

| Outputs to WM                                 | 570 |

| Primitive Assembly                            | 571 |

| Point List Decomposition                      | 575 |

| Line List Decomposition                       | 576 |

| Line Strip Decomposition                      | 576 |

| Triangle List Decomposition                   | 578 |

| Triangle Strip Decomposition                  | 579 |

| Triangle Fan Decomposition                    |     |

| Polygon Decomposition                         | 581 |

| Rectangle List Decomposition                  | 581 |

| Object Setup                                  | 583 |

| Invalid Position Culling (Pre/Post-Transform) | 583 |

| Viewport Transformation                       | 583 |

| Destination Origin Bias                       | 583 |

| Point Rasterization Rule Adjustment           | 584 |

| Drawing Rectangle Offset Application          | 585 |

|    | Point Width Application                    | 587   |

|----|--------------------------------------------|-------|

|    | Rectangle Completion                       | 587   |

|    | Vertex XY Clamping and Quantization        | 588   |

|    | Degenerate Object Culling                  | 589   |

|    | Triangle Orientation (Face) Culling        | 589   |

|    | Scissor Rectangle Clipping                 | 590   |

|    | Viewport Extents Test                      | . 591 |

|    | Line Rasterization                         | . 591 |

|    | Zero-Width (Cosmetic) Line Rasterization   | . 591 |

|    | GIQ (Diamond) Sampling Rules – Legacy Mode | . 592 |

|    | GIQ (Diamond) Sampling Rules – DX10 Mode   | 593   |

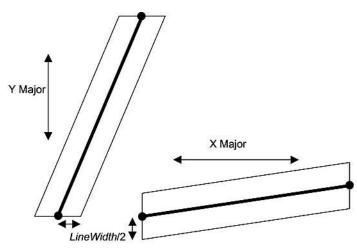

|    | Non-Antialiased Wide Line Rasterization    | 595   |

|    | Anti-Aliased Line Rasterization            | . 596 |

|    | SF Pipeline State Summary                  | . 597 |

|    | 3DSTATE_RASTER [CHV, BSW]                  | 597   |

|    | 3DSTATE_SF                                 | . 598 |

| At | tribute Interpolation Setup                | 603   |

|    | Attribute Swizzling                        | 603   |

|    | Interpolation Modes                        | 604   |

|    | Point Sprites                              | 604   |

|    | Barycentric Attribute Interpolation        | 606   |

| De | epth Offset                                | 606   |

| Ot | her SF Functions                           | 606   |

|    | Statistics Gathering                       | 606   |

| W  | indower (WM) Stage                         | 607   |

|    | Overview                                   | 607   |

|    | Inputs from SF to WM                       | . 608 |

|    | Windower Pipelined State                   | 608   |

|    | 3DSTATE_WM                                 | . 608 |

|    | 3DSTATE_SAMPLE_MASK                        | 613   |

|    | Rasterization                              | 619   |

|    | Drawing Rectangle Clipping                 | 620   |

|    | Line Rasterization                         | 620   |

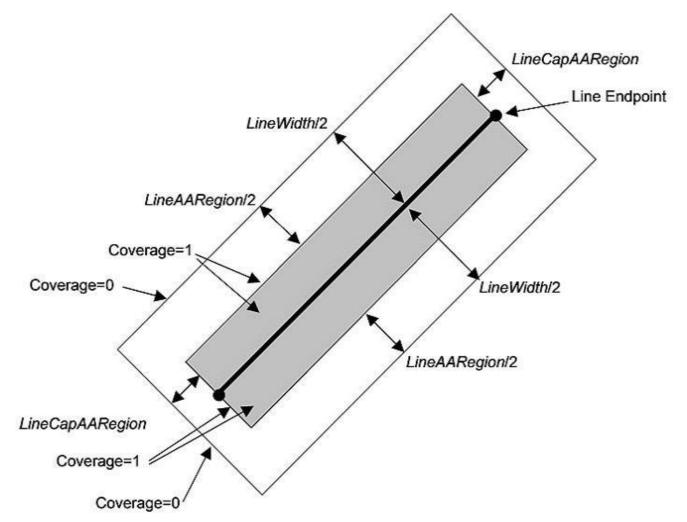

| Coverage Values for Anti-Aliased Lines                   | 620 |

|----------------------------------------------------------|-----|

| 3DSTATE_AA_LINE_PARAMS [CHV, BSW]                        | 620 |

| Line Stipple                                             | 621 |

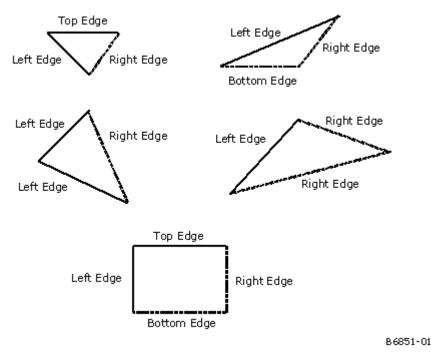

| Polygon (Triangle and Rectangle) Rasterization           | 621 |

| Polygon Stipple                                          | 622 |

| Multisampling                                            | 623 |

| Multisample ModesState                                   | 623 |

| Other WM Functions                                       | 629 |

| Statistics Gathering                                     | 629 |

| Pixel                                                    | 629 |

| Early Depth/Stencil Processing                           | 630 |

| Depth Offset                                             | 630 |

| Early Depth Test/Stencil Test/Write                      | 631 |

| Software-Provided PS Kernel Info                         | 632 |

| Hierarchical Depth Buffer                                | 632 |

| Depth Buffer Clear                                       | 634 |

| Depth Buffer Resolve                                     | 635 |

| Hierarchical Depth Buffer Resolve                        | 636 |

| Optimized Depth Buffer Clear and/or Stencil Buffer Clear | 637 |

| Optimized Depth Buffer Resolve                           | 638 |

| Optimized Hierarchical Depth Buffer Resolve              | 638 |

| Separate Stencil Buffer                                  | 638 |

| DepthStencil Buffer State                                | 639 |

| Pixel Shader Thread Generation                           | 639 |

| 3DSTATE_PS                                               | 640 |

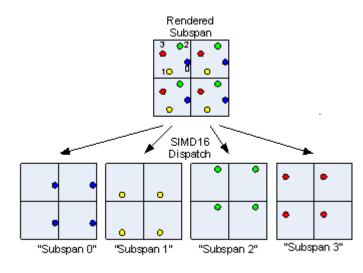

| Pixel Grouping (Dispatch Size) Control                   | 642 |

| Multisampling Effects on Pixel Shader Dispatch           | 644 |

| MSDISPMODE_PERPIXEL Thread Dispatch                      | 644 |

| MSDISPMODE_PERSAMPLE Thread Dispatch                     | 644 |

| PS Thread Payload for Normal Dispatch                    | 647 |

| PS Thread Payload for Normal Dispatch                    | 647 |

| Pixel Backend                                            | 661 |

| Color Calculator (Output Merger)                         | 661 |

| Overview                                           |     |

|----------------------------------------------------|-----|

| Alpha Coverage                                     |     |

| Alpha Test                                         |     |

| Depth Coordinate Offset                            |     |

| Stencil Test                                       |     |

| Depth Test                                         |     |

| Pre-Blend Color Clamping                           |     |

| Pre-Blend Color Clamping When Blending is Disabled |     |

| Pre-Blend Color Clamping When Blending is Enabled  |     |

| Color Buffer Blending                              |     |

| Post-Blend Color Clamping                          |     |

| Dithering                                          |     |

| Logic Ops                                          |     |

| Buffer Update                                      | 671 |

| Stencil Buffer Updates                             | 671 |

| Depth Buffer Updates                               |     |

| Color Gamma Correction                             |     |

| Color Buffer Updates                               |     |

| Pixel Pipeline State Summary                       |     |

| COLOR_CALC_STATE                                   |     |

| 3DSTATE_BLEND_STATE_POINTERS                       |     |

| 3DSTATE_DEPTH_STENCIL_STATE_POINTERS               |     |

| COLOR_CALC_STATE                                   |     |

| DEPTH_STENCIL_STATE                                |     |

| BLEND_STATE                                        |     |

| CC_VIEWPORT                                        |     |

| Other Pixel Pipeline Functions                     |     |

| Statistics Gathering                               |     |

| MCS Buffer for Render Target(s)                    |     |

| Render Target Fast Clear                           |     |

| Render Target Resolve                              |     |

| Media GPGPU Pipeline                               | 679 |

| Media GPGPU Pipeline                               |     |

|    | Programming the GPGPU Pipeline              |     |

|----|---------------------------------------------|-----|

|    | GPGPU Thread Limits                         |     |

|    | GPGPU Commands                              |     |

|    | GPGPU Command Workarounds                   |     |

|    | GPGPU Indirect Thread Dispatch              |     |

|    | GPGPU Context Switch                        |     |

|    | GPGPU Context Switch                        |     |

|    | GPGPU Context Switch Workarounds            |     |

|    | Media GPGPU Payload Limitations             |     |

|    | Synchronization of the Media/GPGPU Pipeline |     |

|    | Mode of Operations                          |     |

|    | GPGPU Thread R0 Header                      |     |

|    | GPGPU Mode                                  |     |

|    | Automatic Thread Generation                 |     |

|    | Thread Payload                              |     |

|    | Execution Masks                             |     |

|    | URB Management                              |     |

|    | Indirect Payload Storage                    |     |

|    | MEDIA_OBJECT_GRPID                          |     |

|    | Starting Offset for a Thread Group ID       |     |

| Th | nread Group Tracking                        |     |

|    | Shared Local Memory Allocation              |     |

|    | Software Managed Shared Local Memory        |     |

|    | Automatic Barrier Management                |     |

|    | Dispatch Payload                            |     |

| Ge | eneric Media                                |     |

|    | Product Evolution                           |     |

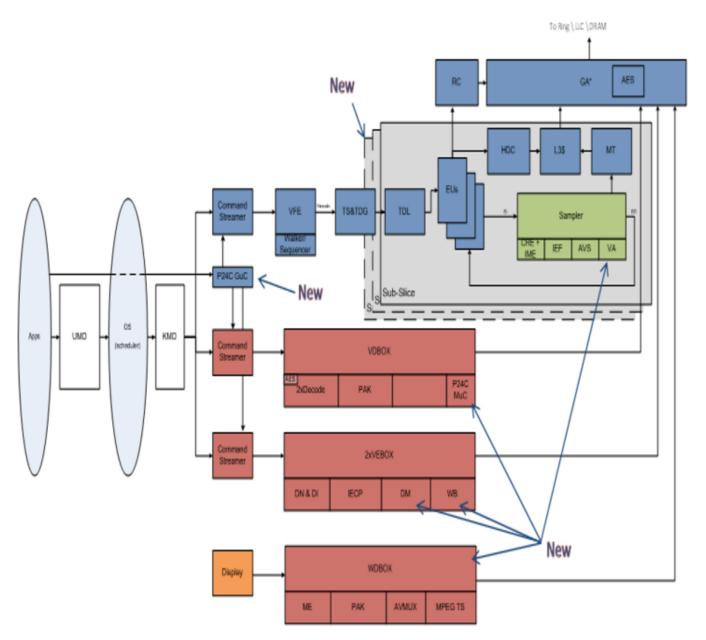

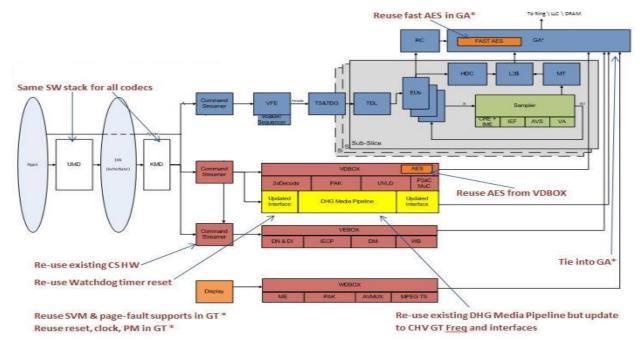

|    | Media and General Purpose Pipeline          | 705 |

|    | Introduction                                |     |

|    | Terminologies                               |     |

|    | Hardware Feature Map in Products            |     |

|    | Media Pipeline Overview                     |     |

|    | Generic Mode                                |     |

| Programming Media Pipeline                    | 710 |

|-----------------------------------------------|-----|

| Command Sequence                              | 710 |

| Command Sequence                              | 710 |

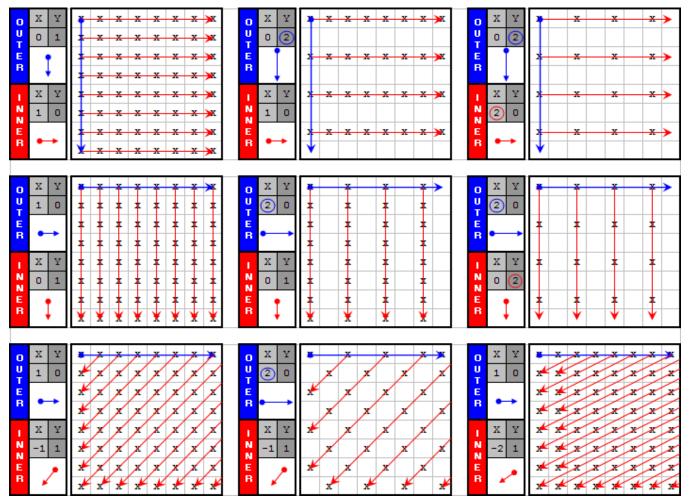

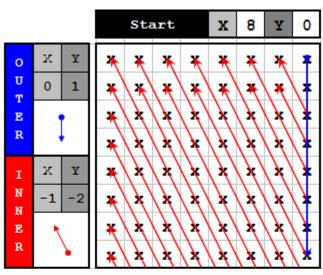

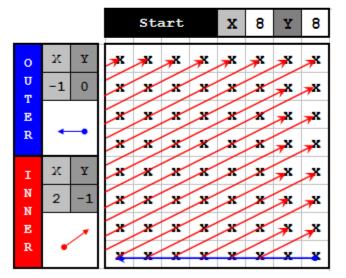

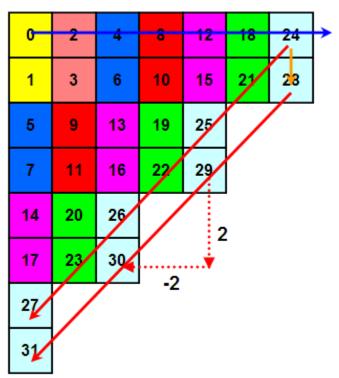

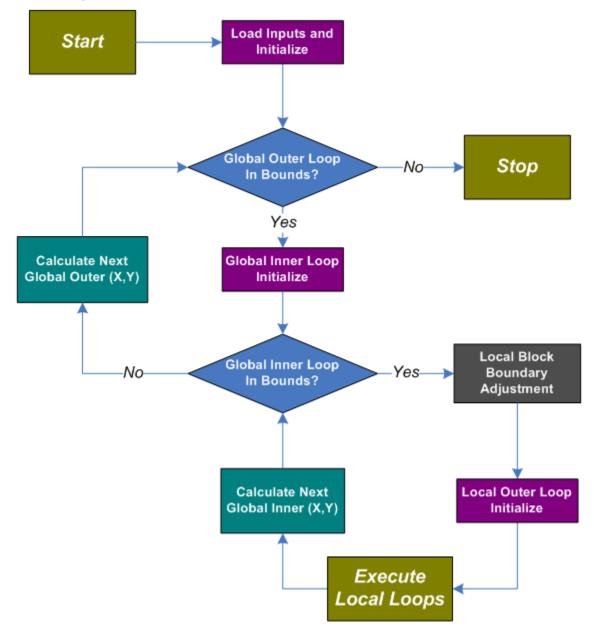

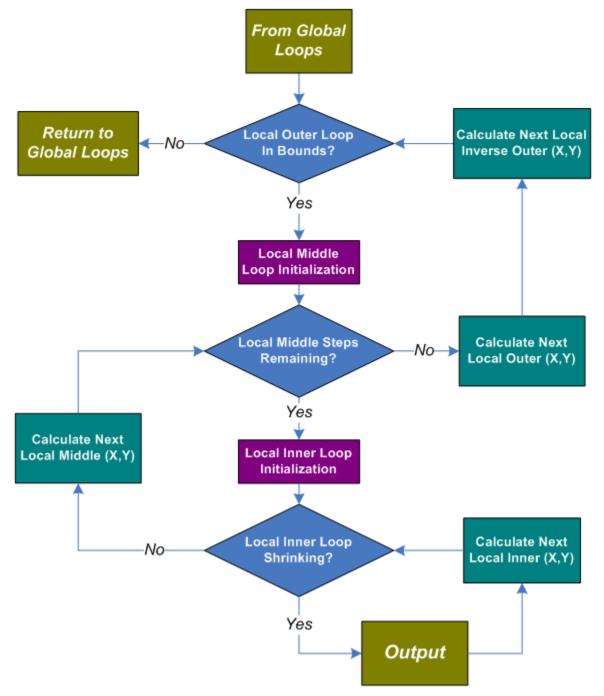

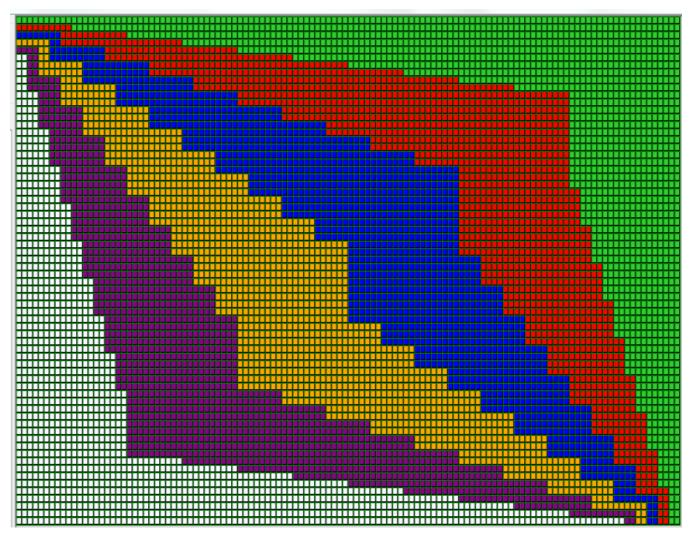

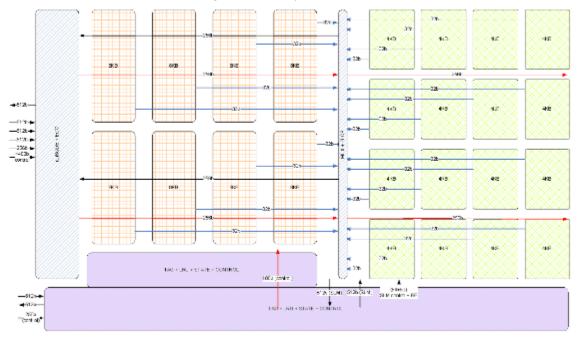

| Parameterized Media Walker                    | 712 |

| Walker Parameter Description                  | 713 |

| Basic Parameters for the Local Loop           | 714 |

| MbAff-Like Special Case in Local Loop         | 716 |

| Global Loop                                   | 717 |

| Walker Algorithm Description                  | 718 |

| Barriers and Shared Local Memory              | 722 |

| Flexible Dispatch of Local Loop               | 723 |

| Scoreboard Control                            | 724 |

| AVC-Style Dependency Example                  | 725 |

| Interface Descriptor Selection                | 727 |

| VC1-Style Dependency Example                  | 729 |

| Multiple Slice Considerations                 | 729 |

| Interrupt Latency                             | 729 |

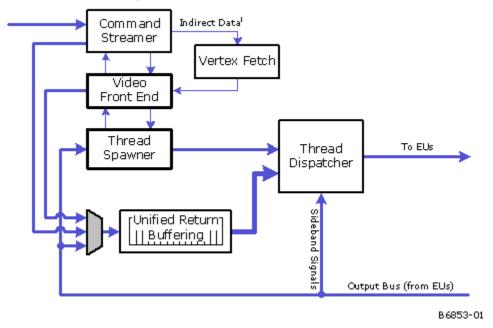

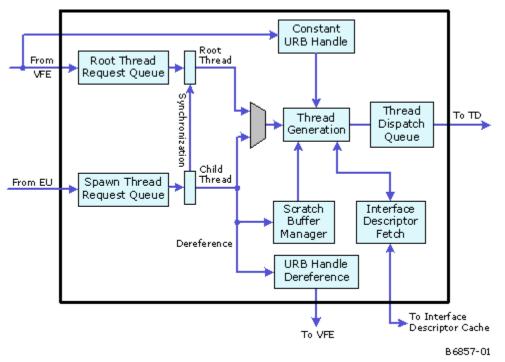

| Thread Spawner Unit                           | 730 |

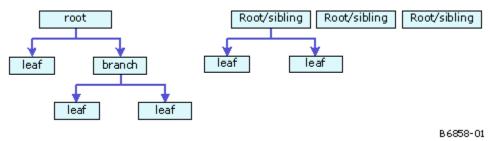

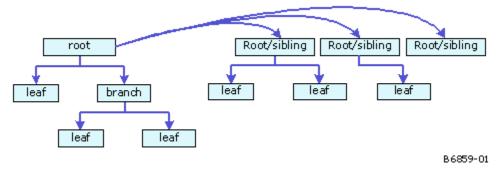

| Root Threads and Child Threads                | 731 |

| Root Threads                                  | 731 |

| URB Handles                                   | 732 |

| Root to Child Responsibilities                | 732 |

| Multiple Simultaneous Roots                   | 732 |

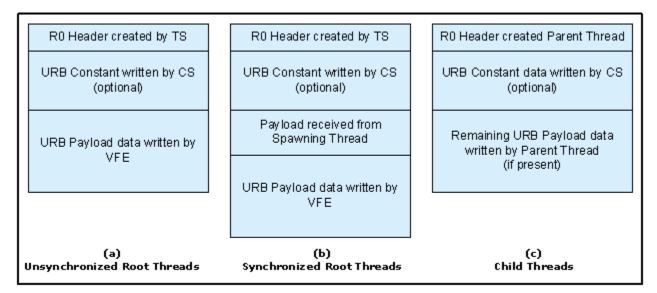

| Synchronized Root Threads                     | 733 |

| Deadlock Prevention                           | 733 |

| Child Thread Life Cycle                       | 734 |

| Arbitration between Root and Child Threads    | 735 |

| Persistent Root Thread                        | 735 |

| Media State Model                             | 736 |

| Media State and Primitive Commands            | 737 |

| Media State and Primitive Command Workarounds | 737 |

| Media Messages                                | 738 |

| Thread Payload Messages                       | 738 |

| Generic Mode Root Thread                                       | 739 |

|----------------------------------------------------------------|-----|

| Root Thread from MEDIA_OBJECT_PRT                              | 740 |

| Root Thread from MEDIA_OBJECT_WALKER                           | 742 |

| MEDIA_OBJECT_GRPID and MEDIA_OBJECT_WALKER with Groups Payload | 742 |

| Thread Spawn Message                                           | 744 |

| Message Descriptor                                             | 745 |

| Message Payload                                                | 745 |

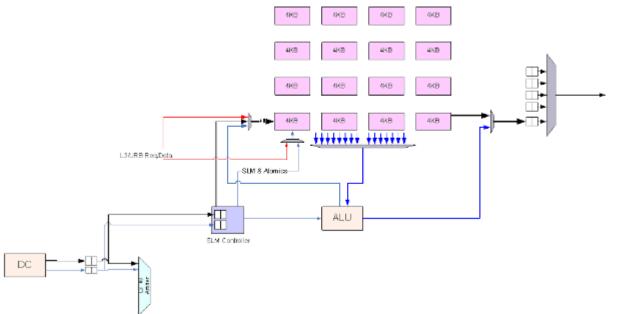

| L3 Cache and URB                                               | 747 |

| L3 Cache and URB                                               | 747 |

| Vol 1i L3\$/URB                                                | 748 |

| Overview (8th Generation)                                      | 748 |

| L3\$ Cache Configuration                                       | 749 |

| Blocks(s) Overview                                             | 749 |

| Size of L3 for 8 <sup>th</sup> Generation                      | 750 |

| ECC Protection                                                 | 750 |

| L3\$ Theory of Operation                                       | 750 |

| Atomics                                                        | 752 |

| L3 Coherency                                                   | 757 |

| Thread level Coherency                                         | 757 |

| Thread Group Coherency                                         | 757 |

| GPU/IA level Coherency                                         | 757 |

| Coherency Usage Models                                         | 758 |

| Fixed Func. Producing (URB)                                    | 758 |

| Fixed Func. Producing (Push Constants)                         | 758 |

| EUs Producing via HDC                                          | 758 |

| Invalidation and Flushes                                       | 759 |

| Node Architecture Impact                                       | 759 |

| Command Streamer Flows                                         | 759 |

| Non-IA Coherent Flows                                          | 760 |

| Top of the Pipe Invalidations                                  | 760 |

| End of the Pipe Flush - Pipeline Flush                         | 760 |

| End of the Pipe Flush - GT3/GT4                                | 760 |

| End of the Pipe Flush - GT2/GT1                                | 760 |

| IA-Coherent Flows                   | 760 |

|-------------------------------------|-----|

| EU/Thread Flows                     |     |

| Global Invalidation                 | 761 |

| Power Management Invalidation       | 761 |

| L3 Allocation and Programming       |     |

| Non-SLM Mode Allocation             |     |

| SLM Mode Allocation                 | 763 |

| Shared Local Memory (SLM)           | 764 |

| Save and Restore Requirements       | 765 |

| SLM Context Save in SuperQ          | 766 |

| 6SLM Context Restore in SuperQ      |     |

| SLM Context Save in L3              | 767 |

| SLM Context Restore in L3           | 767 |

| EU Overview                         | 768 |

| Colssue/Dual Issue:                 | 769 |

| Thread scheduling:                  |     |

| Primary Usage Models                | 770 |

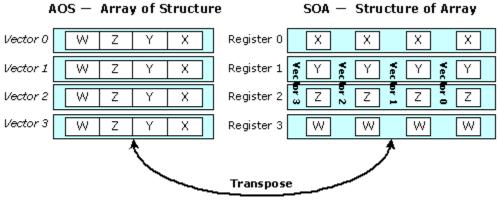

| AOS and SOA Data Structures         | 771 |

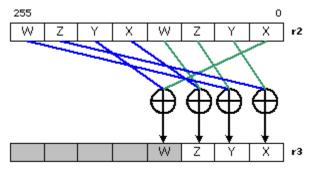

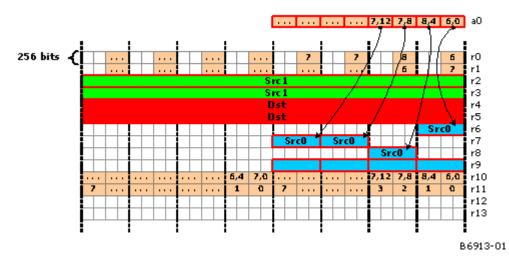

| SIMD4 Mode of Operation             | 773 |

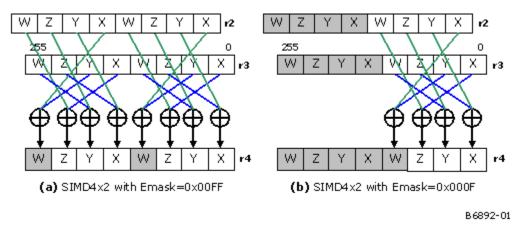

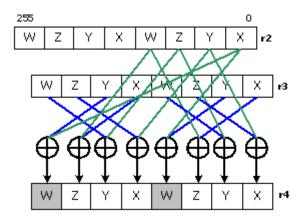

| SIMD4x2 Mode of Operation           | 774 |

| SIMD16 Mode of Operation            | 776 |

| SIMD8 Mode of Operation             | 778 |

| Messages                            | 779 |

| Message Payload Containing a Header |     |

| Writebacks                          |     |

| Message Delivery Ordering Rules     |     |

| Execution Mask and Messages         |     |

| End-Of-Thread (EOT) Message         |     |

| Performance                         |     |

| Message Description Syntax          |     |

| Message Errors                      |     |

| Registers and Register Regions      |     |

| Register Files                      |     |

| GRF Registers                                                 | 787 |

|---------------------------------------------------------------|-----|

| ARF Registers                                                 | 788 |

| ARF Registers Overview                                        | 788 |

| Access Granularity                                            | 789 |

| Null Register                                                 | 790 |

| Address Register                                              | 791 |

| Accumulator Registers                                         | 795 |

| Flag Register                                                 | 800 |

| Channel Enable Register                                       | 801 |

| Message Control Registers                                     |     |

| Example                                                       |     |

| SP Register                                                   |     |

| State Register                                                | 805 |

| Control Register                                              | 811 |

| Notification Registers                                        | 817 |

| IP Register                                                   |     |

| TDR Registers                                                 |     |

| Performance Registers                                         |     |

| Flow Control Registers                                        | 825 |

| Immediate                                                     |     |

| Region Parameters                                             | 830 |

| Region Addressing Modes                                       |     |

| Direct Register Addressing                                    |     |

| Register-Indirect Register Addressing with a 1x1 Index Region | 835 |

| Register-Indirect Register Addressing with a Vx1 Index Region | 836 |

| Register-Indirect Register Addressing with a VxH Index Region | 837 |

| Access Modes                                                  | 839 |

| Execution Data Type                                           |     |

| Register Region Restrictions                                  |     |

| Destination Operand Description                               | 850 |

| Destination Region Parameters                                 | 850 |

| SIMD Execution Control                                        | 851 |

| Predication                                                   |     |

| No Predication                                                        | 853 |

|-----------------------------------------------------------------------|-----|

| Predication with Horizontal Combination                               | 853 |

| Predication with Vertical Combination                                 | 855 |

| End of Thread                                                         | 855 |

| Assigning Conditional Flags                                           | 856 |

| Destination Hazard                                                    | 859 |

| Non-present Operands                                                  | 860 |

| Instruction Prefetch                                                  | 860 |

| ISA Introduction                                                      | 861 |

| Introducing the Execution Unit                                        | 862 |

| EU Terms and Acronyms                                                 | 865 |

| Execution Units (EUs)                                                 | 870 |

| EU Changes by Processor Generation                                    | 871 |

| EU Notation                                                           | 874 |

| Execution Environment                                                 | 875 |

| EU Data Types                                                         | 875 |

| Fundamental Data Types                                                | 875 |

| Numeric Data Types                                                    | 876 |

| Integer Numeric Data Types                                            | 876 |

| Floating-Point Numeric Data Types                                     | 878 |

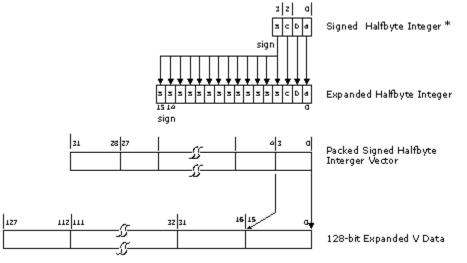

| Packed Signed Half-Byte Integer Vector                                | 880 |

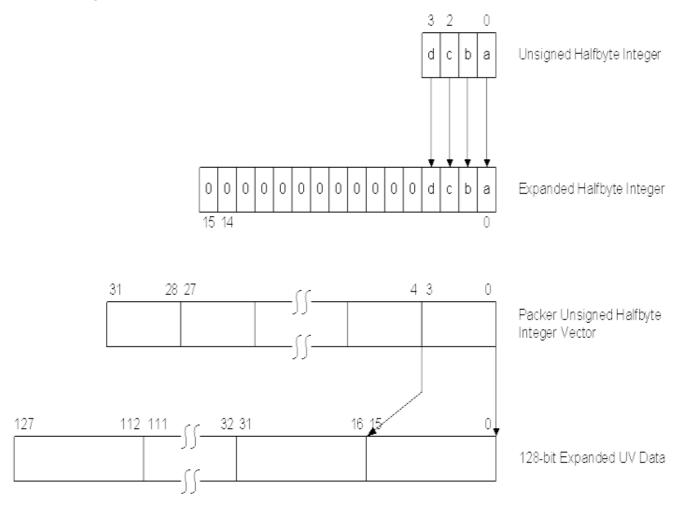

| Packed UnSigned Half-Byte Integer Vector                              | 882 |

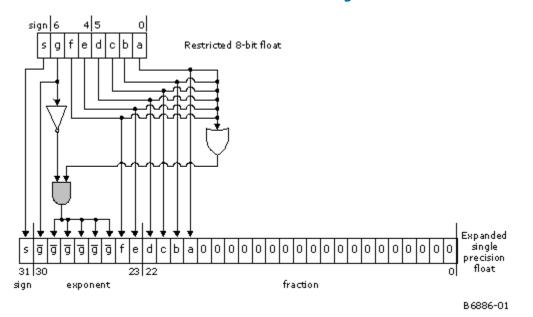

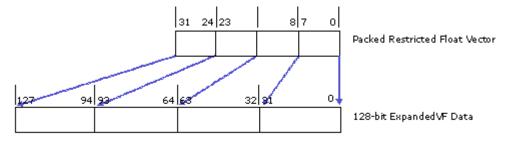

| Packed Restricted Float Vector                                        | 883 |

| Floating Point Modes                                                  | 885 |

| IEEE Floating Point Mode                                              | 885 |

| Partial Listing of Honored IEEE-754 Rules                             | 885 |

| Complete Listing of Deviations or Additional Requirements vs IEEE-754 | 886 |

| Min Max of Floating Point Numbers                                     | 887 |

| Alternative Floating Point Mode                                       | 889 |

| Floating-Point Support                                                | 891 |

| Floating-Point Types and Values                                       | 891 |

| Not a Number (NaN) Formats                                            | 892 |

| Floating-Point Rounding Modes                                         | 893 |

| Floating-Point Operations and Precision                     |     |

|-------------------------------------------------------------|-----|

| Single Precision Floating-Point Rounding to Integral Values |     |

| Floating-Point to Integer Conversion                        |     |

| Integer to Floating-Point Conversion                        |     |

| Floating-Point Min/Max Operations                           |     |

| IEEE Floating-Point Exceptions                              |     |

| Signaling Floating-Point Exceptions                         |     |

| Invalid Operation Exception                                 |     |

| Division by Zero Exception                                  |     |

| Overflow Exception                                          |     |

| Underflow Exception                                         |     |

| Inexact Exception                                           | 901 |

| Floating-Point Compare Operations                           |     |

| Type Conversion                                             |     |

| Float to Integer                                            |     |

| Integer to Integer with Same or Higher Precision            |     |

| Integer to Integer with Lower Precision                     |     |

| Integer to Float                                            |     |

| Double Precision Float to Single Precision Float [CHV, BSW] |     |

| Single Precision Float to Double Precision Float [CHV, BSW] |     |

| Exceptions                                                  |     |

| Exception-Related Architecture Registers                    | 910 |

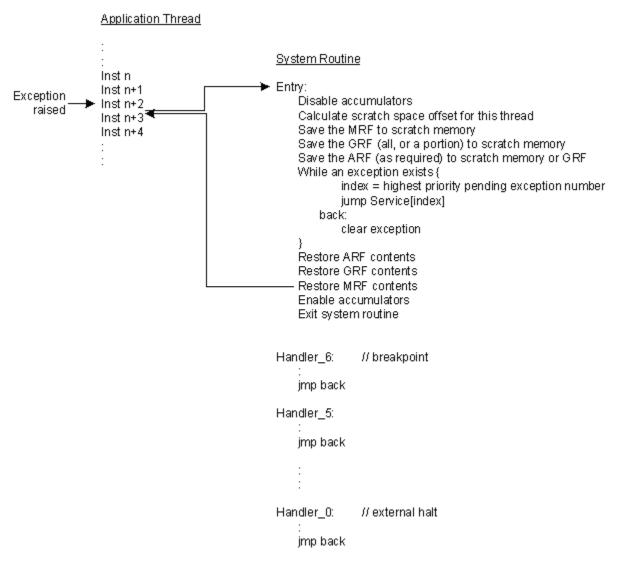

| System Routine                                              | 911 |

| Invoking the System Routine                                 | 911 |

| Returning to the Application Thread                         | 912 |

| System IP (SIP)                                             | 913 |

| System Routine Register Space                               | 913 |

| System Scratch Memory Space                                 | 914 |

| Conditional Instructions Within the System Routine          | 914 |

| Use of NoDDCIr                                              | 915 |

| Exception Descriptions                                      | 916 |

| Illegal Opcode                                              | 916 |

| Undefined Opcodes                                           | 916 |

| Software Exception                        | 916 |

|-------------------------------------------|-----|

| Context Save and Restore                  | 916 |

| Events That Do Not Generate Exceptions    | 918 |

| Illegal Instruction Format                | 918 |

| Malformed Message                         | 918 |

| GRF Register Out of Bounds                | 918 |

| Hung Thread                               | 918 |

| Instruction Fetch Out of Bounds           | 918 |

| FPU Math Errors                           | 919 |

| Computational Overflow                    | 919 |

| System Routine Example                    | 920 |

| Instruction Set Summary                   | 923 |

| Instruction Set Characteristics           | 923 |

| SIMD Instructions and SIMD Width          | 923 |

| Instruction Operands and Register Regions | 923 |

| Instruction Execution                     | 924 |

| Instruction Formats                       | 924 |

| Native Instruction Layouts                | 929 |

| Instruction Fields                        | 933 |

| EU Compact Instructions                   | 951 |

| EU Compact Instruction Format             | 951 |

| EU Instruction Compaction Tables          | 957 |

| Opcode Encoding                           | 963 |

| Move and Logic Instructions               | 963 |

| Flow Control Instructions                 | 964 |

| Miscellaneous Instructions                | 965 |

| Parallel Arithmetic Instructions          | 965 |

| Vector Arithmetic Instructions            |     |

| Special Instructions                      | 968 |

| Native Instruction BNF                    | 969 |

| Instruction Groups                        | 969 |

| Destination Register                      | 970 |

| Source Register                           | 971 |

| Address Registers                   | 972  |

|-------------------------------------|------|

| Register Files and Register Numbers | 972  |

| Relative Location and Stack Control | 973  |

| Regions                             | 974  |

| Types                               | 974  |

| Write Mask                          | 974  |

| Swizzle Control                     | 974  |

| Immediate Values                    | 974  |

| Predication and Modifiers           | 975  |

| Instruction Options                 | 976  |

| Instruction Set Summary Tables      | 977  |

| Accumulator Restrictions            |      |

| Instruction Set Reference           |      |

| Conventions                         |      |

| Pseudo Code Format                  |      |

| General Macros and Definitions      |      |

| Evaluate Write Enable               |      |

| EUISA Instructions                  |      |

| Round Instructions                  |      |

| rndd – Round Down                   |      |

| rnde – Round to Nearest or Even     |      |

| rndu – Round Up                     |      |

| rndz – Round to Zero                |      |

| Send Message                        |      |

| Send Message [CHV, BSW]             |      |

| EUISA Structures                    |      |

| EUISA Enumerations                  |      |

| EU Programming Guide                |      |

| Assembler Pragmas                   |      |

| Declarations                        |      |

| Defaults and Defines                |      |

| Example Pragma Usages               |      |

| Assembly Programming Guideline      | 1001 |

| Usage Examples                                              |      |

|-------------------------------------------------------------|------|

| Vector Immediate                                            |      |

| Supporting DirectX 10 Pixel Shader Indexing                 | 1002 |

| Supporting OpenGL Vertex Shader Instruction SWZ             | 1003 |

| Destination Mask for DP4 and Destination Dependency Control |      |

| Null Register as the Destination                            |      |

| Use of LINE Instruction                                     | 1005 |

| Mask for SEND Instruction                                   | 1006 |

| Channel Enables for Extended Math Unit                      | 1006 |

| Channel Enables for Scratch Memory                          |      |

| Flow Control Instructions                                   | 1010 |

| Execution Masking                                           | 1010 |

| Branching                                                   | 1011 |

| Fast-If                                                     | 1011 |

| Cascade Branching                                           | 1012 |

| Compound Branches                                           |      |

| Looping                                                     | 1014 |

| Indexed Jump                                                |      |

# **Registers in Render Engine**

This chapter describes the memory-mapped registers associated with the Memory Interface, including brief descriptions of their use. Refer to each registers description and related feature for more information on each individual bit. Unless noted otherwise within the description of the bit must only be updated following a flush to ensure the pipeline is idle.

The registers detailed in this chapter are used across the CHV, BSW family of products and are extentions to previous projects. However, slight changes may be present in some registers (i.e., for features added or removed), or some registers may be removed entirely. These changes are clearly marked within this chapter.

# **Predication**

# **Predicate Render Registers**

MI\_PREDICATE\_SRC0 - Predicate Rendering Temporary Register0 MI\_PREDICATE\_SRC1 - Predicate Rendering Temporary Register1 MI\_PREDICATE\_DATA - Predicate Rendering Data Storage MI\_PREDICATE\_RESULT - Predicate Rendering Data Result MI\_PREDICATE\_RESULT\_1 - Predicate Rendering Data Result 1 MI\_PREDICATE\_RESULT\_2 - Predicate Rendering Data Result 2

# **MI\_SET\_PREDICATE**

MI\_SET\_PREDICATE is a command that allows the driver to conditionally choose to execute or skip a command during execution time.

Below is a table of command(s) that are allowed to be programmed when the MI\_SET\_PREDICATE PREDICATE ENABLE field allows any type of predication. If a command is not in the table, then it will have undefined behavior when executed with predication enabled:

### **MI\_SET\_PREDICATE**

| Command                         |

|---------------------------------|

| 3DSTATE_URB_VS                  |

| 3DSTATE_URB_HS                  |

| 3DSTATE_URB_DS                  |

| 3DSTATE_URB_GS                  |

| 3DSTATE_PUSH_CONSTANT_ALLOC_VS  |

| 3DSTATE_PUSH_CONSTANT_ALLOC_HS  |

| 3DSTATE_PUSH_CONSTANT_ALLOC_DS  |

| 3DSTATE_PUSH_CONSTANT_ALLOC_GS  |

| 3DSTATE_PUSH_CONSTANT_ALLOC_PS  |

| MI_LOAD_REGISTER_IMM            |

| 3DSTATE_WM_HZ_OP                |

| MEDIA_VFE_STATE                 |

| MEDIA_OBJECT                    |

| MEDIA_OBJECT_WALKER             |

| MEDIA_INTERFACE_DESCRIPTOR_LOAD |

### MI\_PREDICATE

The MI\_PREDICATE command is used to control the Predicate state bit, which in turn can be used to enable/disable the processing of 3DPRIMITIVE commands.

#### **MI\_PREDICATE**

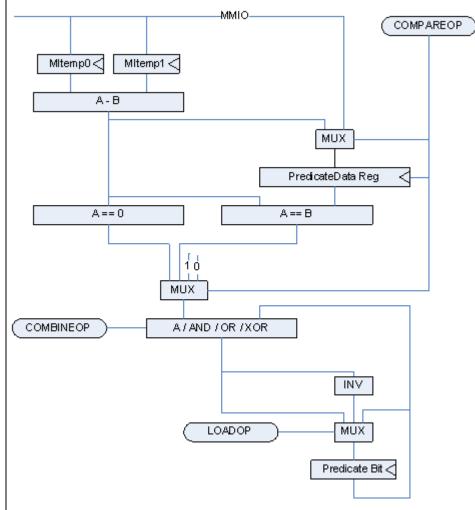

# Predicated Rendering Support in HW

DX10 defines predicated rendering, where sequences of rendering commands can be discarded based on the result of a previous predicate test. A new state bit, Predicate, has been added to the command stream. In addition, a PredicateEnable bit is added to 3DPRIMITIVE. When the PredicateEnable bit is set, the command is ignored if the Predicate state bit is set.

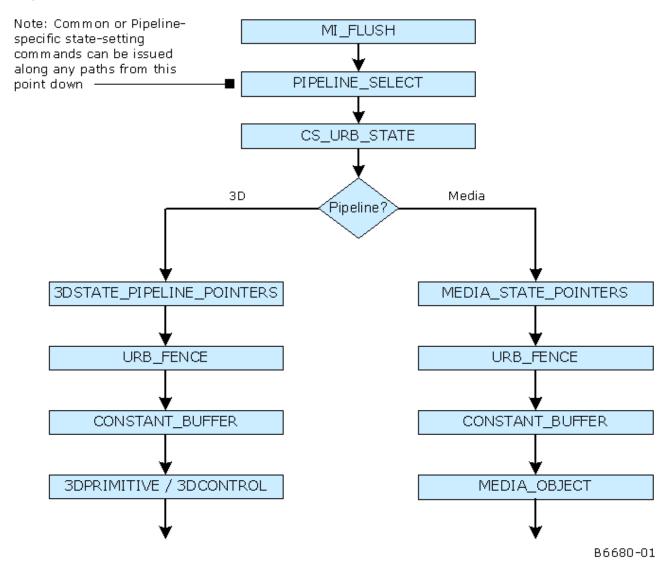

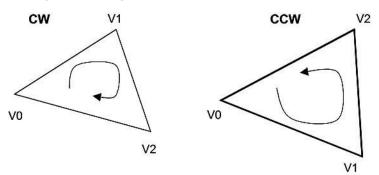

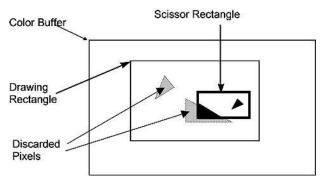

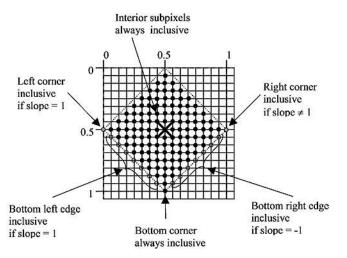

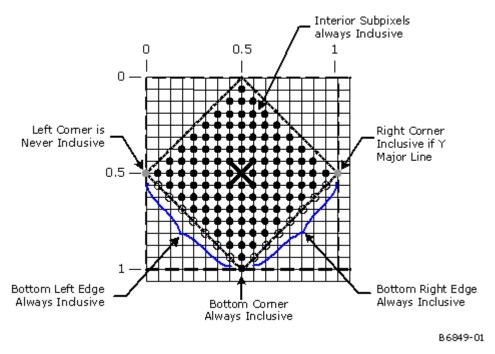

A new command, MI\_PREDICATE, is added. It contains several control fields which specify how the Predicate bit is generated.