# Intel<sup>®</sup> Open Source HD Graphics Programmers' Reference Manual (PRM)

## **Volume 11: Graphics Interface**

For the 2014 Intel Atom™ Processors, Celeron™ Processors, and Pentium™ Processors based on the "BayTrail" Platform (ValleyView graphics)

© April 2014, Intel Corporation

#### **Creative Commons License**

**You are free to Share** — to copy, distribute, display, and perform the work

Under the following conditions:

**Attribution.** You must attribute the work in the manner specified by the author or licensor (but not in any way that suggests that they endorse you or your use of the work).

No Derivative Works. You may not alter, transform, or build upon this work

#### **Notices and Disclaimers**

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Implementations of the I2C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

**Copyright © 2014, Intel Corporation. All rights reserved.**

## **Table of Contents**

| GenLC Registers                                     | 5            |

|-----------------------------------------------------|--------------|

| Memory Map                                          | 6            |

| Relocatable Address Ranges                          |              |

| Legacy Video Area (A_0000h – B_FFFFh)               | 7            |

| VGA Paged                                           | <del>7</del> |

| GTT Stolen Memory (GSM)                             |              |

| GTT Table Format Change                             | 3            |

| Graphics Stolen Memory                              | <u>C</u>     |

| BAR1 – GTTMMADR (GTT and Regs)                      | <u>C</u>     |

| BAR2 – GMADR (Gfx Aperture Memory)                  | 10           |

| IOBAR Indirect MMIO or GTT access                   | 11           |

| Register Range Assignments                          | 12           |

| Register Clock Domains                              | 12           |

| Domain Registers                                    | 12           |

| PCI Configuration Registers                         | 12           |

| Vendor ID and Device ID                             | 13           |

| PCICMD                                              | 14           |

| PCISTS                                              | 15           |

| Revision ID (RID)                                   | 15           |

| HDR                                                 | 16           |

| GTTMMADR                                            | 17           |

| GMADR – Gfx Memory Address Range (ie. Gfx Aperture) | 18           |

| IOBAR                                               | 19           |

| Subsystem Vendor Identification (SSID)              | 19           |

| Subsystem Identification (SID)                      | 20           |

| CAPPOINT                                            | 20           |

| Interrupt Line Register (INTRLINE)                  | 21           |

| INTR                                                | 21           |

| GGC                                                 | 22           |

| BDSM – Base of Data Stolen Memory                   | 24           |

| MSAC – Multi-Size Aperture Control                  | 25           |

| BGSM – Base of GTT Stolen Memory                    | 26           |

| MSI_CAPID                                           | 26           |

| Message Control (MC)                                | 27           |

| MA                                                  | 28           |

| MD                                                  | 28           |

| VCID                                                | 29           |

| VC                                                  | 29           |

| FD                                                  | 30           |

| PM Capabilities ID                                  | 30           |

| PM Capabilities                                | 32 |

|------------------------------------------------|----|

| PMCS                                           | 32 |

| SWSMISCI                                       | 33 |

| ASLE                                           | 34 |

| ASLS                                           | 35 |

| Memory Interface Registers (MIR)               | 35 |

| IIR_RW – Alternate IIR Access                  | 37 |

| SCPD0 – Scratch Pad 0 Register                 | 37 |

| IER – Interrupt Enable Register                | 38 |

| IIR – Interrupt Identity Register              | 40 |

| IMR – Interrupt Mask Register                  | 43 |

| ISR – Interrupt Status Register                | 46 |

| EIR – Error Identity Register                  | 4  |

| EMR – Error Mask Register                      | 49 |

| ESR – Error Status Register                    | 50 |

| Power Context Base Register (PCBR)             | 50 |

| GTLC: SA MMIO Registers                        | 52 |

| Fence Registers                                | 52 |

| Gfx_FLSH_CNTL                                  | 53 |

| GTFIFOCTL                                      | 52 |

| GTLC Wake Control                              | 52 |

| GTLC Power Well Status                         | 50 |

| Render Force wake req                          | 50 |

| Render Force wake ack                          | 57 |

| Media Force wake req                           | 57 |

| Media Force wake ack                           | 58 |

| Render RC6 (Standby) counter                   | 58 |

| Media RC6 (Standby) counter                    | 59 |

| GTLC: "Render/Media/PM" Interrupt Architecture | 59 |

| GTLC: Master Interrupt Register                | 59 |

| GTLC: "Render/Media" Interrupts                | 62 |

| ISR – Interrupt Status Register                | 62 |

| GTLC: "Power Management" Interrupts            | 66 |

| GTLC: Scratch Registers                        |    |

| SWF – Software Flags                           | 7  |

| GTSCRATCH – GT Scratch registers               | 7  |

## **GenLC Registers**

The figure below shows the different types of registers that reside within the GenLC block.

| Configuration<br>Registers | Memory Mapped<br>Registers | Private Registers | IO Registers                |

|----------------------------|----------------------------|-------------------|-----------------------------|

| 256B                       | 2MB                        |                   | 0x0h : Index<br>0x4h : Data |

**Figure: High-level GenLC Registers**

## **Memory Map**

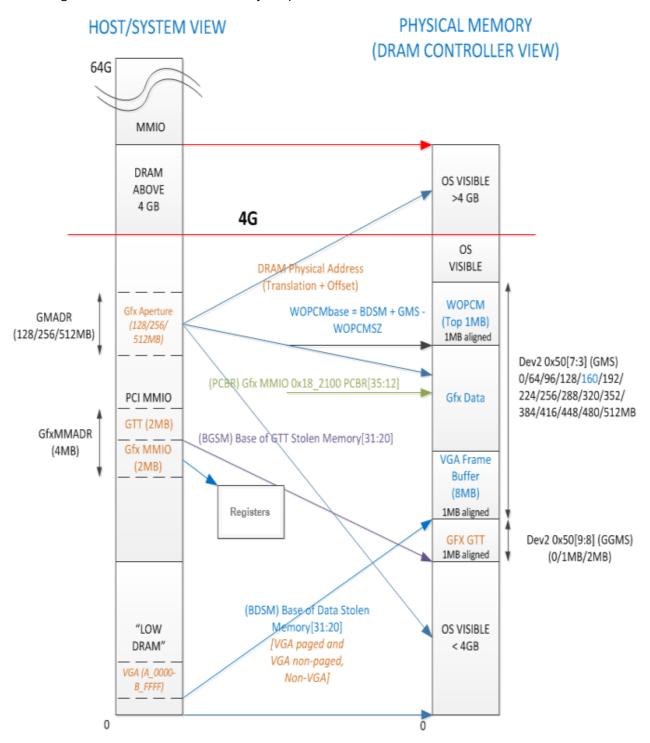

The diagram below shows the memory map for Gfx Device 2.

**Figure: Device 2 Memory Map**

### **Relocatable Address Ranges**

Bus 0, Device 2, Function 0:

- IOBAR IO access window for internal graphics. Though this window address/data register pair, using I/O semantics, the IGD and internal graphics instruction port registers can be accessed.

Note, this allows accessing the same registers as GTTMMADR. The IOBAR can be used to issue writes to the GTTMMADR or the GTT table.

- 2. **GMADR** Internal graphics translation window (128MB, 256MB, 512MB window).

- 3. **GTTMMADR** This register requests a 4MB allocation for combined Graphics Translation Table Modification Range and Memory Mapped Range. GTTADR will be at GTTMMADR + 2MB while the MMIO base address will be the same as GTTMMADR.

- 4. **GGC.GMS** Graphics Mode Select. Used to select the amount of main memory that is preallocated to support the internal graphics device in VGA (non-linear) and Native (linear) modes.

- 5. **GGC.GGMS** GTT Graphics Memory Size. Used to select the amount of main memory that is pre-allocated to support the Internal Graphics Translation Table. (0-2MB options).

VGA memory and VGA IO addresses are also supported.

## Legacy Video Area (A\_0000h - B\_FFFFh)

The legacy 128KB VGA memory range, frame buffer, (000A\_0000h – 000B\_FFFFh) can be mapped to Device #2. The VGA memory space is a 128KB space. The space's virtual address range, as seen on the IOSF bus, is A0000h-BFFFFh. The space's starting physical address is given by the Base of Data Stolen Memory register value (Dev 2 register BDSM[31:20]).

**Table: Frame Buffer Accesses (VGA Memory Map Mode Register)**

| VRH_HT_<br>GR06[3:2] | A0000h - AFFFFh | B0000h - B7FFFh | B8000h - BFFFFh |

|----------------------|-----------------|-----------------|-----------------|

| 00                   | X               | X               | X               |

| 01                   | Х               |                 |                 |

| 10                   |                 | Х               |                 |

| 11                   |                 |                 | X               |

#### **VGA Paged**

The VGA frame buffer is 8MB (similar to client). The space's virtual address range, as seen on the IOSF bus, is A0000h-AFFFFh.

## **GTT Stolen Memory (GSM)**

The base of the GTT table memory is contained in register BGSM. GSM is allocated to store the GFX translation table entries. This space is allocated to store accesses as page table entries get updated through virtual GTTMMADR range. Hardware is responsible to map PTEs into this physical space.

Direct accesses to GSM are not allowed. The memory map programming and North Cluster IMR programming prevents direct GSM accesses. Only hardware translations and fetches can be directed to GSM.

ValleyView North Cluster has IMR registers that define stolen memory regions. The GSM will be mapped into an IMR region. The SAI attribute, driven on PFI, ensures the North Cluster does not invalidate GSM directed translations or fetches.

#### **GTT Table Format Change**

The GTT entry will be redefined to use bit 2 to indicate whether a page is snooped or not.

Only the Graphics-initiated accesses need this field; IOSF Host initiated cycles are already coherent, so the aperture translation path can ignore this GTT entry bit.

####

**Graphics Page Table Entry Format**

**Figure: GTT Table Format**

**Table: GTT Table Entry Description**

| Bit    | Description                                                                                                                                                                                                  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31: 12 | <b>Physical Page Address 31:12:</b> If the Valid bit is set, This field provides the page number of the physical memory page backing the corresponding Graphics Memory page.                                 |

| 11:4   | Physical Start Address Extension: This field specified Bits 39:32 of the page table entry. This field must be zero for 32 bit addresses.                                                                     |

| 3      | Graphics Data Type (GFDT)  This field contains the GFDT bit for this surface when writes occur. GFDT can also be set by various state commands and indirect objects. The effective GFDT is the logical OR of |

|        | the GTT entry with this field. This field is ignored for reads.                                                                                                                                              |

|        | Format = U1                                                                                                                                                                                                  |

|        | 0: No GFDT (default)                                                                                                                                                                                         |

|        | 1: GFDT                                                                                                                                                                                                      |

| Bit | Description                                                                                                         |

|-----|---------------------------------------------------------------------------------------------------------------------|

| 2:1 | Coherency Control (when GT is a non-caching agent – VLV LCIA)                                                       |

|     |                                                                                                                     |

|     | This field controls coherency with the CPU core caches                                                              |

|     | 0x: data in this page is not coherent with the CPU caches                                                           |

|     | 1x: data accesses in this page must be snooped in the CPU caches                                                    |

| 0   | <b>Valid PTE:</b> This field indicates whether the mapping of the corresponding Graphics Memory page is valid.      |

|     | 1: Valid                                                                                                            |

|     | 0: Invalid. An access (other than a CPU Read) through an invalid PTE will result in Page Table Error (Invalid PTE). |

## **Graphics Stolen Memory**

The Gen graphics engine relies on a sections of memory that are accessible to graphics but not to CPU software. This is called *stolen memory* or sometimes just *graphics memory*. This consists of 2 ranges, set up by BIOS:

- 1. GTT stolen memory: Programmable 1MB or 2MB space, used to store virtual->physical graphics translation tables. CPU software cannot access this directly; a section of the GTTMMADR BAR accessible to the Device 2 driver is mapped to this range.

- a. TLB fetch requests are mapped to this range

- 2. Data stolen memory: Programmable 32MB-512MB space, used for general graphics data (including frame buffers and other local structures). This range will be the target of some of the virtual address pages via the GTT.

- a. Lower 8MB VGA frame buffer. VGA client can only access this region

For VLV, the Northbridge "IMR" mechanism will be used to reserve these 2 spaces for graphics hidden from the OS.

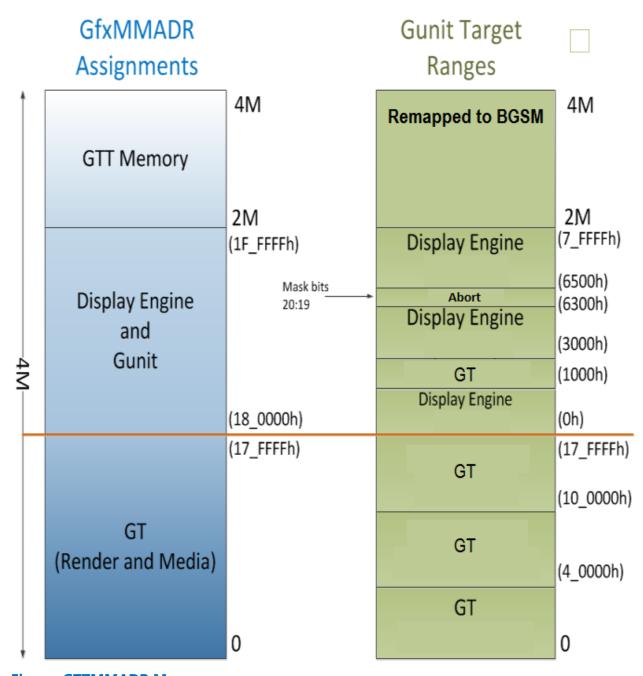

## **BAR1 – GTTMMADR (GTT and Regs)**

This range will be marked as UC (Un-cacheable). This BAR is split in half. The bottom portion is registers while the top portion is the window to the GTT (Graphics Translation Table).

**Figure: GTTMMADR Map**

## **BAR2 – GMADR (Gfx Aperture Memory)**

IOSF primary accesses targeting GMADR range are translated using the GTT translation table. The resulting physical addressed request is then sent to system memory. The GMADR range can be subdivided using the fence registers within Gfx MMIO space. TileY, TileX, and linear formats will be supported.

#### **IOBAR Indirect MMIO or GTT access**

The graphics interface (Device 2) contains an IOBAR register. If Device 2 is enabled, then IGD registers or the GTT table can be accessed using this IOBAR. The IOBAR is composed of an index register and a data register.

**MMIO\_Index:** MMIO\_INDEX is a 32 bit register. An IO write to this port loads the offset of the MMIO register or offset into the GTT that needs to be accessed. An IO Read returns the current value of this register. See IOBAR rules for detailed information.

**MMIO\_Data:** MMIO\_DATA is a 32 bit register. An IO write to this port is re-directed to the MMIO register pointed to by the MMIO-index register. An IO read to this port is re-directed to the MMIO register pointed to by the MMIO-index register.

The result of accesses through IOBAR can be:

- a. Accesses directed to the GTT table. (i.e. route to DRAM)

- b. Accesses to Graphics MMIO registers.

**Note:** GTT table space writes (GTTADR) are supported through this mapping mechanism.

This mechanism to access internal graphics MMIO registers must not be used to access VGA IO registers which are mapped through the MMIO space. VGA registers must be accessed directly through the dedicated VGA IO ports.

## **Register Range Assignments**

- Gfx registers:

- o PCI Configuration registers (housed in Gfx)

- o Gfx "MIR" MMIO registers

- Gfx related registers

- Display "MIR" MMIO registers

- 1. Housed in Gfx as a service to Display.

- o Gfx "GTLC" MMIO registers

- SA,

- GTLC interrupt registers

- GTLC MMIO registers

- Display MMIO registers

## **Register Clock Domains**

This topic is still under development.

## **Domain Registers**

#### **PCI Configuration Registers**

#### **Table: PCI Configuration Register Summary**

| Name     | Address | Functionality                                           | Notes                                                                                                                   |

|----------|---------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| DID      | 0x0000  | PCI Device and Vendor ID<br>Register                    | rtotes                                                                                                                  |

| PCICMD   | 0x0004  | PCI Command and Status<br>Register                      |                                                                                                                         |

| PCISTS   | 0x0006  |                                                         |                                                                                                                         |

| RIDCC    | 0x0008  | Revision Identification and<br>Class Codes              |                                                                                                                         |

| HDR      | 0x000C  | Header Type                                             |                                                                                                                         |

| GTTMMADR | 0x0010  | BAR for Memory Mapped<br>Registers and GTT Table        |                                                                                                                         |

| GMADR    | 0x0018  | BAR for Gfx Aperture                                    |                                                                                                                         |

| IOBAR    | 0x0020  | I/O BAR, BAR for the MMIO_INDEX and MMIO_DATA registers | Used only by SBIOS                                                                                                      |

| SSID     | 0x002C  | Subsystem Identifiers.                                  | Only the BIOS can write this register, and only once after reset. After the first write, this register becomes readonly |

| Name      | Address | Functionality                                                        | Notes                                                                                                                          |

|-----------|---------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| CAPPOINT  | 0x0034  | Capabilities Pointer                                                 |                                                                                                                                |

| INTR      | 0x003C  | Interrupt                                                            | This register is programmed by SBIOS. It is not used by the graphics/display driver                                            |

| MGGC      | 0x0050  | Graphics Control                                                     | Used to select the amount of memory pre-allocated to support the graphics device in VGA (non-linear) and Native (linear) modes |

| BDSM      | 0x005c  | Base of Gfx Data Stolen<br>Memory                                    | Contains the VGA frame buffer and other Gfx data and command structures.                                                       |

| MSAC      | 0x0062  | Multi-Size Aperture Control                                          |                                                                                                                                |

| BGSM      | 0x0070  | Base of GTT Stolen Memory                                            |                                                                                                                                |

| MSI_CAPID | 0x0090  | Message Signaled Interrupts<br>Capability ID and Control<br>Register |                                                                                                                                |

| MA        | 0x0094  | Message Address                                                      | Used for upstream IOSF Primary messages                                                                                        |

| MD        | 0x0098  | Message Data                                                         | Data used for upstream IOSF Primary MSI messages                                                                               |

| VCID      | 0x00B0  | Vendor Capability ID                                                 |                                                                                                                                |

| VC        | 0x00B4  | Vendor Capabilities                                                  |                                                                                                                                |

| FD        | 0x00C4  | Functional Disable                                                   | Used by SBIOS, not by driver                                                                                                   |

| PMCAP     | 0x00D0  | Power Management<br>Capabilities                                     |                                                                                                                                |

| PMCS      | 0x00D4  | Power Management<br>Control/Status                                   | Driver and SBIOS don't use this register                                                                                       |

| SWSMISCI  | 0x00E0  | Software SMI or SCI                                                  | The graphics driver writes to this register as a means to interrupt the SBIOS                                                  |

| ASLE      | 0x00E4  | System Display Event Register                                        | SBIOS writes this register to generate an interrupt to the graphics/display driver                                             |

| ASLS      | 0x00FC  | ASL Storage                                                          |                                                                                                                                |

#### **Vendor ID and Device ID**

PCI Address: 00h

**Description:** D2: PCI Device ID and Vendor ID Register

| Field Name                       | Bit   | Access | Reset<br>Value | Description                                                   |

|----------------------------------|-------|--------|----------------|---------------------------------------------------------------|

| DEVICE_IDENTIFICATION_NUMB ER    | 31:16 | RO     | 0F31           | DID: Identifier assigned to the Device 2 Graphics PCI device. |

| VENDOR_IDENTIFICATION_NU<br>MBER | 15:0  | RO     | 8086h          | VID: PCI standard identification for Intel                    |

#### **PCICMD**

PCI Address: 04h

**Description:** PCI Command Register

|                   |       |        | Reset |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------|-------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field Name        | Bit   | Access | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Reserved          | 15:11 | RO     | 00h   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| INTERRUPT_DISABLE | 10    | RW     | 0b    | ID: 0: Legacy interrupt message is enabled. 1: Disables legacy interrupt message generation on IOSF Sideband.  Note: The interrupt status is not blocked from being reflected in PCISTS.IS. Note: MSI interrupt generation :(PCISTS.IS & PCICMD.BME & MSI_CAPID.MSIE) changes from 0 to 1.  Note: Message bus interrupt assert is sent: (PCISTS.IS & ~PCICMD.ID & ~MSI_CAPID.MSIE) changes from 0 to 1.  Note: Message bus interrupt de-assert is sent: (PCISTS.IS & ~PCICMD.ID & ~MSI_CAPID.MSIE) changes from 1 to 0                                  |

| Reserved          | 9:3   | RO     | 00h   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BUS_MASTER_ENABLE | 2     | RW     | 0b    | BME:(BME & MAE are observed. But context save/restore can occur.) 0: Blocks the sending of MSI interrupts. 1: Permits the sending of MSI interrupts                                                                                                                                                                                                                                                                                                                                                                                                     |

| Reserved          | 1     | RW     | 0b    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IO_SPACE_ENABLE   | 0     | RW     | 0b    | O: I/O space is disabled. IORD and IOWr cycles will not be claimed.  1: I/O space is enabled. VGA_IO and Gfx_IOBAR are checked. If an IORD/IOWR matches (VGA IO address range or GFX_IOBAR), the cycle will be claimed. Care should be taken in setting up GFX_IOBAR that more than 1 match is not made as this will result in unpredictable behavior.  VGA_IO: Address[15:0] is checked to determine if it falls in the VGA IO range.  (The VGA IO range is 03B0h –03BBh and 03C0h – 03DFh.)  Gfx_IOBAR: Address[15:3] is compared to GFX_IOBAR[15:3]. |

#### **PCISTS**

PCI Address: 06h

**Description:** PCI Status Register

| Field Name       | Bit  | Access | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                                        |

|------------------|------|--------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved         | 15:5 | RO     | 000h           | Reserved                                                                                                                                                                                                                                                                                                                                                           |

| CAPABILITY_LIST  | 4    | RO     | 1b             | CAP: Indicates that the CAPPOINT register at 34h provides an offset into PCI Configuration Space containing a pointer to the location of the first item in the list                                                                                                                                                                                                |

| INTERRUPT_STATUS | 3    | RO     | 0b             | IS: Reflects the state of the interrupt in the graphics device.  1: Determined by IIR and IER memory interface registers. Indicates a device 2 (Display/Media/Render) interrupt request.  0: No interrupt pending.  Only when the Interrupt Disable bit in the command register is a 0 and this Interrupt Status bit is a 1, will the assert_IntX message be sent. |

| Reserved         | 2:0  | RO     | 000b           | Reserved                                                                                                                                                                                                                                                                                                                                                           |

### **Revision ID (RID)**

PCI Address: 08h

**Description:** Revision Identification

| Field Name  | Bit | Access | Reset<br>Value | Description                                                     |

|-------------|-----|--------|----------------|-----------------------------------------------------------------|

| REVISION_ID | 7:0 | RO     | From<br>metal  | RID: The value in this field reflects the value of Revision ID. |

|             |     |        | straps         | This register is read-able by any agent.                        |

Class Codes (CC)

PCI Address: 09h

**Description:** Class Codes

|                       |       |        | Reset |                                                                                                                                                                                                                                                                                                                                     |

|-----------------------|-------|--------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field Name            | Bit   | Access | Value | Description                                                                                                                                                                                                                                                                                                                         |

| BASE_CLASS_CODE       | 23:16 | RO     | 03h   | BCC: This is an 8-bit value that indicates the base class code. When MGGC0[VAMEN] is 0 this code has the value 03h, indicating a Display Controller. When MGGC0[VAMEN] is 1 this code has the value 04h, indicating a Multimedia Device.                                                                                            |

| SUB_CLASS_CODE        | 15:8  | RO     | 00h   | When MGGC0[VAMEN] is 1, this value is 80h, indicating other multimedia device.  When MGGC0[VAMEN] is 0 this value will be determined based on GGC register, GMS and IVD fields. When cfg_MGGC[17] = 1 or cfg_MGGC[22:20] = 3'b000 this value is 80h, otherwise its 00h 00h: VGA compatible 80h: Non VGA (GMS = "00h" or IVD = "1b") |

| PROGRAMMING_INTERFACE | 7:0   | RO     | 00h   | PI: When MGGC0[VAMEN] is 0 this value is 00h, indicating a Display Controller. When MGGC0[VAMEN] is 1 this value is 00h, indicating a NOP.                                                                                                                                                                                          |

#### **HDR**

PCI Address: 0Ch

**Description:** Header Type

| Field Name            | Bit   | Access | Reset<br>Value | Description                                               |

|-----------------------|-------|--------|----------------|-----------------------------------------------------------|

| Reserved              | 31:24 | RO     | 00h            | Reserved                                                  |

| MULTI_FUNCTION_STATUS | 23    | RO     | 0b             | MFUNC: Integrated graphics is a single function           |

| HEADER_CODE           | 22:16 | RO     | 00h            | HDR: Indicates a type 0 configuration space header format |

| Reserved              | 15:0  | RO     | 0000h          | Reserved                                                  |

#### **GTTMMADR**

PCI Address: 10-17h

**Description:** Gfx Memory Mapped Address Range. This is the base address for all memory mapped

registers and GTT table.

This register requests allocation for the combined Graphics Translation Table Modification Range and Memory Mapped Range. The range requires 4 MB combined for MMIO and Global GTT aperture, with 512K of that used by MMIO and 2MB used by GTT. GTTADR will begin at (GTTMMADR + 2 MB) while the MMIO base address will be the same as GTTMMADR.

For the Global GTT, this range is defined as a memory BAR in graphics device config space. It is an alias into which software is required to write Page Table Entry values (PTEs). Software may read PTE values from the global Graphics Translation Table (GTT). PTEs cannot be written directly into the global GTT memory area.

The allocation is for 4MB and the base address is defined by bits [31:22].

| Field Name | Bit   | Access | Reset<br>Value | Description                                                                                                      |

|------------|-------|--------|----------------|------------------------------------------------------------------------------------------------------------------|

| Reserved   | 63:36 | RO     | 000000h        | Reserved for Memory Base Address (RSVD):  Must be set to 0 since addressing above 64GB is not supported.         |

| Reserved   | 35:32 | RO     | 0h             | Reserved – since 32 bit BAR.                                                                                     |

| MBA        | 31:22 | RW     | 0000h          | Memory Base Address (MBA):  4MB combined for MMIO and Global GTT table aperture (2MB for MMIO and 2 MB for GTT). |

| Reserved   | 21:4  | RO     | 00000h         | Reserved (RSVD): Hardwired to 0's to indicate at least 4MB address range.                                        |

| Reserved   | 3     | RO     | 0b             | Prefetchable Memory (PREFMEM): Hardwired to 0 to prevent prefetching.                                            |

| МЕМТҮР     | 2:1   | RO     | 00b            | Memory Type (MEMTYP): 00: To indicate 32 bit base address 01: Reserved 10: To indicate 64 bit base address       |

| Reserved   | 0     | RO     | 0b             | Memory/IO Space (MIOS): Hardwired to 0 to indicate memory space.                                                 |

#### **GMADR – Gfx Memory Address Range (ie. Gfx Aperture)**

PCI Address: 18-1Fh

**Description:** Gfx Aperture location.

GMADR is a Prefetchable range in order to apply USWC attribute (from the processor point of view) to that range. The USWC attribute is used by the processor for write combining.

Accesses to this range will be translated to DRAM Physical memory addresses. Fence registers may be used to sub-divide this range and allow tiled surfaces (determined by fence registers).

The following sizes are supported: 128MB, 256MB, 512MB. (Determined by the MSAC register).

| Field Name | Bit   | Access | Reset<br>Value | Description                                                                                                                                                                                                       |

|------------|-------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved   | 63:36 | RO     | 00000000h      | Memory Base Address (MBA2): Memory Base Address (MBA): Set by the OS, these bits correspond to address signals [63:36].                                                                                           |

| Reserved   | 35:32 | RO     | 0h             | Reserved – 32 bit BAR supported                                                                                                                                                                                   |

| МВА        | 31:29 | RW     | 0000000Ь       | Memory Base Address (MBA): Memory Base Address (MBA): Set by the OS, these bits correspond to address signals [31:29].                                                                                            |

| ADMSK512   | 28    | RW-L   | 0b             | 512MB Address Mask (512ADMSK): This bit is either part of the Memory Base Address (R/W) or part of the Address Mask (RO), depending on the value of MSAC[2:1]. See MSAC (Dev2, Func 0, offset 62h) for details.   |

| ADMSK256   | 27    | RW-L   | 0b             | 256 MB Address Mask (256ADMSK): This bit is either part of the Memory Base Address (R/W) or part of the Address Mask (RO), depending on the value of MSAC[2:1]. See MSAC (Dev 2, Func 0, offset 62h) for details. |

| Reserved   | 26:4  | RO     | 0000000h       | Address Mask (ADM): Hardwired to 0s to indicate at least 128MB address range.                                                                                                                                     |

| PREFMEM    | 3     | RO     | 1b             | Prefetchable Memory (PREFMEM): Hardwired to 1 to enable prefetching.                                                                                                                                              |

| МЕМТҮР     | 2:1   | RO     | 00b            | Memory Type (MEMTYP): 00: To indicate 32 bit base address 01: Reserved 10: To indicate 64 bit base address                                                                                                        |

| Reserved   | 0     | RO     | 0b             | Memory/IO Space (MIOS): Hardwired to 0 to indicate memory space.                                                                                                                                                  |

#### **IOBAR**

PCI Address: 20-23h

**Description:** I/O Base Address. This is used only by SBIOS. This register is the base address for the MMIO\_INDEX and MMIO\_DATA registers

This register provides the Base offset of the I/O registers within Device #2. Access to the 8Bs of IO space is allowed in PM state D0 when IO Enable (PCICMD bit 0) set. Access is disallowed:

- in PM states D1-D3 or

- if IO Enable is clear or

- if Device #2 is turned off or

- if Internal graphics is disabled thru the fuse or fuse override mechanisms.

Note that access to this IO BAR is independent of VGA functionality within Device #2.

If accesses to this IO bar is allowed then the GMCH claims all 8, 16 or 32 bit IO cycles from the CPU that falls within the 8B claimed.

| Field Name        | Bit   | Access | Reset<br>Value | Description                                                                                                                                                                                  |

|-------------------|-------|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved          | 31:16 | RO     | 0000h          | Reserved                                                                                                                                                                                     |

| BASE_ADDRESS      | 15:3  | RW     | 0000h          | BA: Set by the OS, these bits correspond to address signals [15:3]. The IOBAR is to be used for both GTLC register programming and GTT table programming. This is an indirect access method. |

| Reserved          | 2:1   | RO     | 0h             | Reserved                                                                                                                                                                                     |

| RESOURCE_TYPE_RTE | 0     | RO     | 1b             | Indicates a request for I/O space                                                                                                                                                            |

#### **Subsystem Vendor Identification (SSID)**

PCI Address: 2C-2Dh

**Description:** This register is used to uniquely identify the subsystem where the PCI device resides.

| Field Name | Bit  | Access | Reset<br>Value | Description                                                                                                                                                                                                         |

|------------|------|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUBVID     | 15:0 | RW-O   | 0000h          | This value is used to identify the vendor of the subsystem. This register should be programmed by BIOS during boot-up. Once written, this register becomes Read_Only. This register can only be cleared by a Reset. |

#### **Subsystem Identification (SID)**

PCI Address: 2E-2Fh

**Description:** This register is used to uniquely identify the subsystem where the PCI device resides.

| Field Name | Bit  | Access | Reset<br>Value | Description                                                                                                                                                                                                         |

|------------|------|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUBID      | 15:0 | RW-O   | 0000h          | This value is used to identify the vendor of the subsystem. This register should be programmed by BIOS during boot-up. Once written, this register becomes Read_Only. This register can only be cleared by a Reset. |

#### **CAPPOINT**

PCI Address: 34-37h

**Description:** This register points to a linked list of capabilities implemented by this device.

The capability linked list is:

(Head-34, PMCAP-D0, MSI-90, VID-B0, ... End)

| Field Name           | Bit  | Access | Reset<br>Value | Description                                                                                                                                                                                                                |

|----------------------|------|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved             | 31:8 | RO     | 000000h        | Reserved                                                                                                                                                                                                                   |

| CAPABILITIES_POINTER | 7:0  | RW-O   | D0h            | The first item in the capabilities list is at address D0h (PMCS).  This register should be programmed by BIOS during boot-up. Once written, this register becomes Read_Only. This register can only be cleared by a Reset. |

#### **Interrupt Line Register (INTRLINE)**

PCI Address: 3Ch

**Description:** Interrupt. This register is programmed by SBIOS. It is not used by the graphics/display driver. This 8-bit register is used to communicate interrupt line routing information. It is read/write and must be implemented by the device. POST software will write the routing information into this register as it initializes and configures the system.

The value in this register tells which input of the system interrupt controller(s) the device's interrupt pin is connected to. The device itself does not use this value, rather it is used by device drivers and operating systems to determine priority and vector information.

| Field Name | Bit | Access | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|-----|--------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTRLINE   | 7:0 | RW     | 00h            | ILIN: BIOS written value to communicate interrupt line routing information to the device driver Used to communicate interrupt line routing information. POST software writes the routing information into this register as it initializes and configures the system. The value in this register indicates to which input of the system interrupt controller the device's interrupt pin is connected. |

#### **INTR**

PCI Address: 3Dh

Description: Interrupt. This register is programmed by SBIOS. It is not used by the graphics/display

driver

| Field Name    | Bit | Access | Reset<br>Value | Description                                                                                                                                                                                            |

|---------------|-----|--------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTERRUPT_PIN | 7:0 | RO     | 01h            | IPIN: Value indicates which interrupt pin this device uses. This field is hard coded to 1h since Valleyview Device 2 is a single function device. The PCI spec requires that it use INTA#. 01h: INTA#. |

#### **GGC**

PCI Address: 50-51h

**Description:** GMCH Graphics Control Register

| Field Name | Bit   | Access | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------|-------|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved   | 15    | RO     | 0b             | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VAMEN      | 14    | RW-L   | 0b             | Enables the use of the iGFX engines for Versatile Acceleration.  1 – iGFX engines are in Versatile Acceleration Mode. Device 2 Class Code is 048000h.  0 – iGFX engines are in iGFX Mode. Device 2 Class Code is 030000h.                                                                                                                                                                                                                                                                                                                                                                                                  |

| Reserved   | 13:10 | RO     | 0h             | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GGMS       | 9:8   | RW-L   | 00b            | This field is used to select the amount of Main Memory that is pre-allocated to support the Internal Graphics Translation Table. The BIOS ensures that memory is pre-allocated only when Internal graphics is enabled.  GSM is assumed to be a contiguous physical DRAM space with DSM, and BIOS needs to allocate a contiguous memory chunk. Hardware will drive the base of GSM from DSM only using the GSM size programmed in the register.  Oh: No memory pre-allocated. GTT cycles (Mem and IO) are not claimed.  1h: 1 MB of memory pre-allocated for GTT.  2h: 2 MB of memory pre-allocated for GTT.  3h: Reserved. |

|            |       |        |                | All unspecified encodings of this register field are reserved,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Field Name | Bit | Access | Reset<br>Value | Description                                                                                                                                                                                                                                               |

|------------|-----|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |     |        |                | hardware functionality is not guaranteed if used.                                                                                                                                                                                                         |

| GMS        | 7:3 | RW-L   | 00101b         | Graphics Mode Select (GMS).                                                                                                                                                                                                                               |

|            |     |        |                | This field is used to select the amount of Main Memory that is pre-allocated to support the Internal Graphics device in VGA (non-linear) and Native (linear) modes. The BIOS ensures that memory is pre-allocated only when Internal graphics is enabled. |

|            |     |        |                | Hardware does not clear or set any of these bits automatically based on IGD being disabled/enabled.                                                                                                                                                       |

|            |     |        |                | BIOS Requirement: BIOS must not set this field to 0h if IVD (bit 1 of this register) is 0.                                                                                                                                                                |

|            |     |        |                | 0h = 0MB                                                                                                                                                                                                                                                  |

|            |     |        |                | 10h = 512MB                                                                                                                                                                                                                                               |

|            |     |        |                | 1h = Reserved (32 MB – encoding is only valid for steppings C0 and beyond.)                                                                                                                                                                               |

|            |     |        |                | 2h = 64MB                                                                                                                                                                                                                                                 |

|            |     |        |                | 3h = 96MB                                                                                                                                                                                                                                                 |

|            |     |        |                | 4h = 128MB                                                                                                                                                                                                                                                |

|            |     |        |                | 5h = 160MB                                                                                                                                                                                                                                                |

|            |     |        |                | 6h = 192MB                                                                                                                                                                                                                                                |

|            |     |        |                | 7h = 224MB                                                                                                                                                                                                                                                |

|            |     |        |                | 8h = 256MB                                                                                                                                                                                                                                                |

|            |     |        |                | 9h = 288MB                                                                                                                                                                                                                                                |

|            |     |        |                | Ah = 320MB                                                                                                                                                                                                                                                |

|            |     |        |                | Bh = 352MB                                                                                                                                                                                                                                                |

|            |     |        |                | Ch = 384MB                                                                                                                                                                                                                                                |

|            |     |        |                | Dh = 416MB                                                                                                                                                                                                                                                |

| Field Name  | Bit | Access | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-----|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |     |        |                | Eh = 448MB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |     |        |                | Fh = 480MB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |     |        |                | Other = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |     |        |                | When GMS != 000 (and VD=0):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             |     |        |                | When GMS == 000 :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|             |     |        |                | No address compare will occur<br>against VGA memory range or the<br>VGA IO register range. Also,<br>CC[15:8] is changed to 8'h80 from<br>8'h00                                                                                                                                                                                                                                                                                                                                                                                          |

| Reserved    | 2   | RO     | 0b             | Reserved ():                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| VGA_DISABLE | 1   | RW-L   | ОЬ             | VGA Disable (VD):  0: Enable. Device 2 (IGD) claims VGA memory and IO cycles, the Sub-Class Code within Device 2 Class Code register is 00.  1: Disable. Device 2 (IGD) does not claim VGA cycles (Mem and IO), and the Sub- Class Code field within Device 2 function 0 Class Code register is 80. BIOS Requirement: BIOS must not set this bit to 0 if the GMS field preallocates no memory.  This bit MUST be set to 1 if Device 2 is disabled either via a fuse or fuse override (CAPID0[38] = 1) or via a register (DEVEN[3] = 0). |

| GGCLCK      | 0   | RW-L   | 0b             | When set to 1b, this bit will lock all bits in this register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

### **BDSM – Base of Data Stolen Memory**

PCI Address: 5C-5Fh

**Description:** This register contains the base address of Graphics Data Stolen DRAM memory.

Graphics Stolen Memory is within DRAM space. The base of stolen memory will always be below 4G.

| Field Name | Bit   | Access | Reset<br>Value | Description                                                              |

|------------|-------|--------|----------------|--------------------------------------------------------------------------|

| BDSM       | 31:20 | RW-L   | 000h           | BDSM: BASE_OF_Data_STOLEN_MEMORY This register contains bits 31 to 20 of |

| Field Name | Bit  | Access | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                  |

|------------|------|--------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |      |        |                | the base address of Data stolen DRAM memory. For certain GTLC generated accesses, this base register will be added to the GTLC provided offset address, forming the full physical address for the PFI fabric. This is also used as a base for VGA paged accesses. The display engine also uses the register. |

| Reserved   | 19:1 | RO     | 00000h         | Reserved                                                                                                                                                                                                                                                                                                     |

| Lock       | 0    | RW-L   | 0b             | This bit will lock all writeable settings in this register, including itself.                                                                                                                                                                                                                                |

#### **MSAC – Multi-Size Aperture Control**

PCI Address: 62h

**Description:** This register determines the size of the graphics memory aperture. Only the system BIOS will write this register based on pre- boot address allocation efforts. Graphics may read this register to determine the correct aperture size. System BIOS needs to save this value on boot so that it can reset it correctly during S3 resume.

The size of the aperture must not be modified by software after its location is written into GMADR (offset 18h).

| Field Name | Bit | Access | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                |

|------------|-----|--------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved   | 7:3 | RO     | 00000b         | Reserved                                                                                                                                                                                                                                                                                                                                   |

| LHSAS      | 2:1 | RW     | 01b            | Untrusted Aperture Size (LHSAS): 00: bits [28:27] of GMADR register are made R/W allowing 128MB of GMADR 01: bit [28] of GMADR is made R/W and bit [27] of GMADR is forced to zero allowing 256MB of GMADR 10: Illegal programming. 11: bits [28:27] of GMADR register are made Read only and forced to zero, allowing only 512MB of GMADR |

| Reserved   | 0   | RO     | 0b             | Reserved                                                                                                                                                                                                                                                                                                                                   |

### **BGSM** – Base of GTT Stolen Memory

PCI Address: 70-73h

**Description:** Base of GTT table in Gfx Stolen Memory

The GTT table is located within Graphics Stolen Memory in DRAM space. The base of stolen memory

will always be below 4G.

| Field Name | Bit   | Access | Reset<br>Value | Description                                                                                                                                                                                                                                                                                                                                           |

|------------|-------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BGSM       | 31:20 | RW-L   | 000h           | BGSM: Gfx Base of GTT Stolen Memory This register contains bits 31 to 20 of the base address of GTT Table in stolen DRAM memory. BIOS determines the base of GTT stolen memory by subtracting the GTT graphics stolen memory size (PCI Device 2 offset 50 bits 9:8) from the Graphics Base of Data Stolen Memory (PCI Device 2 offset 5C bits 31:20). |

| Reserved   | 19:1  | RO     | 00000h         | Reserved                                                                                                                                                                                                                                                                                                                                              |

| Lock       | 0     | RW-L   | 0b             | This bit will lock all writeable settings in this register, including itself.                                                                                                                                                                                                                                                                         |

#### **MSI\_CAPID**

PCI Address: 90-91h

**Description:** Message Signaled Interrupts Capability ID

| Field Name                 | Bit  | Access | Reset<br>Value | Description                                                                                                                                                                                                                                           |

|----------------------------|------|--------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POINTER_TO_NEXT_CAPABILITY | 15:8 | RW-O   | B0h            | Points to the next item in the list (B0=VCID support). Next pointer changed with HSD#259253.  This register should be programmed by BIOS during boot-up. Once written, this register becomes Read_Only. This register can only be cleared by a Reset. |

| CAPABILITY_ID              | 7:0  | RO     | 05h            | CAPID: Indicates an MSI capability                                                                                                                                                                                                                    |

### **Message Control (MC)**

PCI Address: 92-93h

**Description:** Message Signaled Control Register