Intel® Arc<sup>™</sup> A-Series Graphics and Intel Data Center GPU Flex Series Open-Source Programmer's Reference Manual For the discrete GPUs code named "Alchemist" and "Arctic Sound-M"

Volume 13: SW/HW System Interface

March 2023, Revision 1.0

### **Notices and Disclaimers**

Intel technologies may require enabled hardware, software or service activation.

No product or component can be absolutely secure.

Code names are used by Intel to identify products, technologies, or services that are in development and not publicly available. These are not "commercial" names and not intended to function as trademarks

Customer is responsible for safety of the overall system, including compliance with applicable safetyrelated requirements or standards.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document, with the sole exceptions that a) you may publish an unmodified copy and b) code included in this document is licensed subject to Zero-Clause BSD open source license (0BSD). You may create software implementations based on this document and in compliance with the foregoing that are intended to execute on the Intel product(s) referenced in this document. No rights are granted to create modifications or derivatives of this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined". Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

© Intel Corporation. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

### **Table of Contents**

| SW/HW System Interface                       | 1  |

|----------------------------------------------|----|

| HW Graphics Virtualization                   | 1  |

| Introduction                                 | 1  |

| Exposing the Virtualization Capable Hardware | 3  |

| MMIO Space                                   | 3  |

| Global Address space and Graphics Aperture   | 4  |

| VM Workload Scheduling                       | 5  |

| VF Workload Execution in an Engine           | 6  |

| Managing Privilege Levels                    | 6  |

| Interrupt Interface                          | 11 |

| Resets                                       | 12 |

| Stolen Memory Management                     | 14 |

| Local Memory Virtualization                  | 15 |

| MMIO                                         | 21 |

| Force Wake and Steering Table                | 21 |

| Multicast Steering and Die Recovery          |    |

| SW Virtualization Reserved MMIO range        |    |

| Register Address Maps                        |    |

| Graphics Register Address Map                |    |

| VGA and Extended VGA Register Map            |    |

| GUC                                          |    |

| GuC Introduction                             |    |

| Arming Doorbells                             |    |

| GuC Shim (GUCSHIM) Register Functions        | 41 |

| Guc DMA (GUCDMA)                             | 42 |

| GuC Interrupt (GUCINT) Register Functions    | 44 |

| Observability                                | 48 |

| Observability Overview                       | 48 |

| DFD Configuration Restore                    | 48 |

| Trace                                        | 49 |

| Interrupts                                   | 84 |

| Introduction                                 |    |

| Memory Based Interrupt Status Reporting | 91 |

|-----------------------------------------|----|

| Gdie Interrupt and Errors               | 93 |

### **SW/HW System Interface**

### **HW Graphics Virtualization**

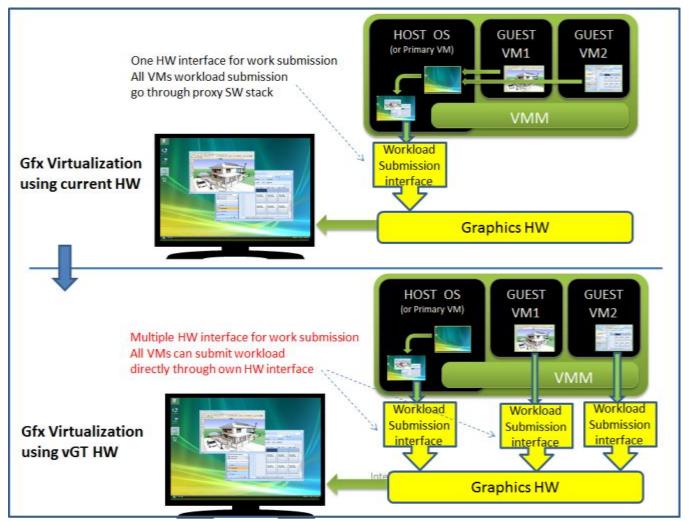

Graphics virtualization allows multiple Virtual Machines (VMs) to access high-quality, high-performance graphics, with minimal software overhead. The graphics virtualization feature adds hardware and firmware to improve performance and enable VMMs to support Intel(R) HD Graphics, Iris0x2122 graphics, and Iris0x2122 Pro graphics in a standard way, eliminating special requirements that could be barriers to adoption.

### Introduction

Intel platforms have supported Virtualization Technology for Directed I/O (VT-d) since 2007. In the original VT-d model, graphics is exposed as a single device that can be assigned to only one VM, thus limiting how workloads are submitted to hardware. Such limitations can degrade performance for all VMs, except the one that owns the graphics hardware.

The figure below shows the new concept of graphics virtualization, where each VM can access fully accelerated graphics capabilities.

#### **Fully Virtualized Graphics - Conceptual View**

The capability depicted above requires the following infrastructure:

- Graphics hardware that exposes multiple hardware interfaces, for assignment to different VMs;

- Resources to submit the graphics workload:

- o Memory (aperture) allowing each VM to submit workload and associated data surfaces;

- o A graphics translation table (GTT) to manage aperture pages;

- o Some MMIO registers exposed to each VM;

- A signaling mechanism to invoke the hardware to execute the workload;

- A signaling mechanism for the hardware to convey relevant information by sending interrupts;

- A mechanism to display the output produced by the execution of the workload.

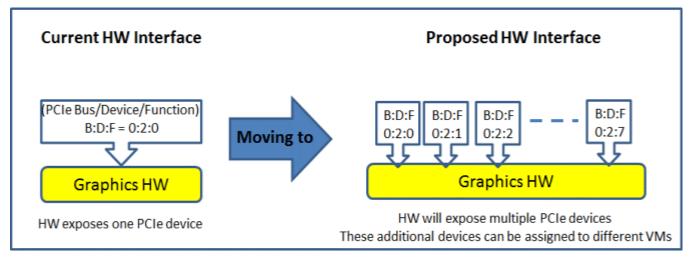

The figure below shows the proposed hardware interface used to allow multiple software stacks to each get their own "graphics device."

#### **Hardware Interface**

Display Output from a Virtualized Environment

There are several possible ways to display content from a virtualized graphics environment:

- Rely on the virtual machine monitor (VMM) or PF driver to composite rendered surfaces from different VMs;

- Assign a display engine exclusively to a virtual function (VF), preferably a trusted VF from the VMM perspective, and use the corresponding planes/pipes to output data;

- Assign a display pipe or plane to a VF.

For In-Vehicle Infotainment (IVI), some applications may require keeping keep the VMM very light weight, and letting a trusted VM manage the display (including composition). In such a scenario, the main dashboard might be owned by the trusted VM, while ancillary displays would be managed by a different VM.

#### **Exposing the Virtualization Capable Hardware**

The graphics virtualization infrastructure is exposed to system software by the Single Root I/O virtualization standard (SR-IOV), of the PCIe standard. The exposure is accomplished using a PCIe device Physical function that includes the SR-IOV Extended Capability structure, within the PCIe Extended Capabilities list.

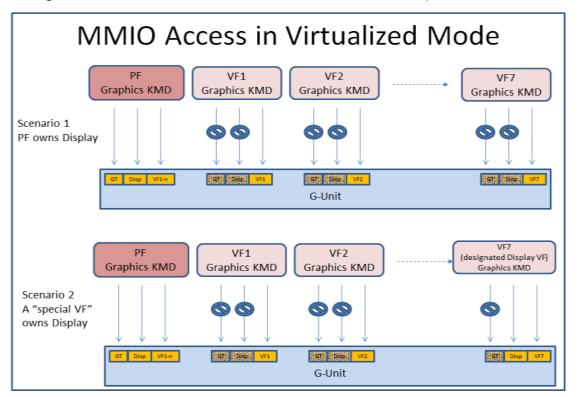

#### **MMIO Space**

The MMIO register space allocates 8MB for graphics hardware, but currently only a subset of that allocation is used for MMIO. All GT, Media, and Display MMIO registers are allocated within the lower 3MB of the MMIO range, so each VF needs a minimum of 4MB of MMIO space, after rounding up to the next power of two. To simplify design and validation, and provide additional MMIO space in the future, both VF and PF are allocated 8MB of MMIO register space each.

From a global perspective, only the PF graphics driver needs to access most MMIO registers. From a security viewpoint, the VF driver and software stack are less trusted than PF, so VF does not have access to the full graphics device MMIO range. However, the VM controlling a VF needs to access a small subset of MMIO registers, such as those used to communicate with GuC, and create a VMM-independent PF to VF communication channel. The registers are replicated within the MMIO space of each VF, and only those registers can be accessed by the VM via the VF MMIO.

Limiting VF access to hardware registers requires closing two access paths: direct CPU access and access via a graphics engine. This section covers restricting the CPU access path; the Privilege section covers restricting the graphics engines path.

The figure below shows how the various stacks view the MMIO space.

#### **MMIO Access in Virtualized Mode**

As with the PF, VF hardware allocates the MMIO register space and the Global GTT in the same PCI BAR (GTTMMADR), which is 16MB per VF.

#### **Global Address space and Graphics Aperture**

The graphics hardware currently supports graphics aperture, and global graphics address space, up to 4GB. When SRIOV is enabled, the global address space is 4GB and is shared among all Functions. System software running in a VM submits commands and data required for a workload through the graphics aperture. When the VMM assigns a VF to a VM, the VMM exposes the VF's graphics aperture range (VF GMADR) and GGTT range (VF GTTMMADR), so the VF graphics driver can access and manage the global address space assigned to it by the Host KMD:

- The Host graphics driver (PF KMD) manages the allocation of global address pages to Physical and Virtual Functions

- A field in the Global GTT contains the number of the Function to which that page has been assigned, and that page may only be accessed by that VF, or the PF

- The Guest graphics driver (VF KMD) can modify the address mapping (Global->GPA) for global address pages that have already been assigned to that VF by the Host KMD (Function field matches the VF)

- Graphics aperture accesses require two translations using the VF-GGTT to translate from Graphics address to GPA, then using the VF's BDF to translate from GPA to HPA.

- When the Host accesses a global page via the PF, VTd translation will be based on the Function Number stored in the GGTT entry.

A Guest Kernel Mode Driver can update GGTT Entries only for pages that have been assigned to that Guest, as determined by the Function Number field in the GGTT Entry. If the Function Number in the entry matches the Function Number of the VF assigned to the Guest, then the access is allowed, otherwise it is not. The exact behavior for matching and non-matching function numbers is described below.

#### **VF GTTMMADR Accesses**

| Read w/Matching VF                                                        | Read<br>w/Mismatch VF | Write with Matching VF                                         | Write<br>w/Mismatch VF |

|---------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------|------------------------|

| Returns all fields except Function<br>Number[7:2], which is returned as 0 |                       | Updates all fields except Function<br>Number[7:2] and Valid[0] | No Updates             |

#### **VF** Aperture Operations

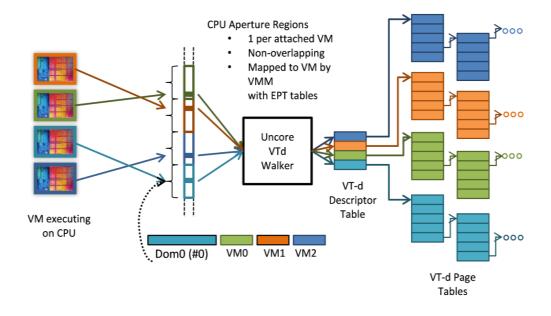

Graphics hardware supports the ability to determine the BDF used for aperture accesses, which may happen simultaneously (as shown in the following figure). The BDF to be associated with an aperture access is based on the per-VF BAR range.

#### VT-d Translation of Aperture Accesses

### VM Workload Scheduling

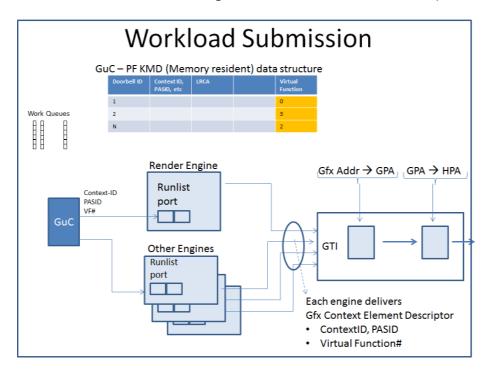

Allow PFs to submit workloads: for example, to do compositing or other operations that require using data from different VMs. The figure below shows the basic conceptual model for workload submission.

#### **Workload Submission**

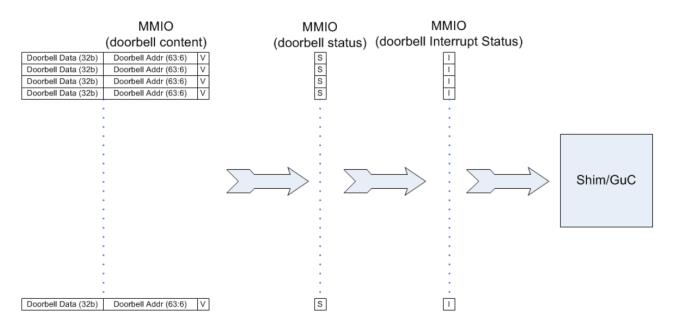

Memory-based doorbell queues are the primary mechanism for scheduling workloads on the graphics hardware. The PF KMD assigns some doorbells to each VM for requesting execution. Within a VM, the graphics driver allocates available doorbells to the entities that submit work. For example, the PF KMD may have 256 doorbells available and assign 32 to a VM, then the VM graphics driver may keep 16 doorbells for itself and grants 16 for direct submission by Ring3 (UMD) applications.

The graphics KMD and GuC have a shared data structure that stores workload-related characteristics (ContextID, PASID, Doorbell#, LRCA location, etc). The table for each workload queue also adds the VF number. When a doorbell ring results in a workload submittal, the GuC also submits a VF number from the queue table into the execlist port. The supplied VF number is added to the context attribute and relayed to GTI. In virtualized mode, GTI performs a nested translation: the first-level translation is based on PASID (advanced mode) or PPGTT (legacy mode); the second level translation is a standard VT-d translation based on the BDF, where "F" comes from the VF number.

#### **VF Workload Execution in an Engine**

Gang-scheduling all engines would be inefficient, so GuC supports the ability to schedule a workload from any VF to any engine. Hence each engine can be executing context on behalf of different VFs. Each engine delivers the PASID, the directory pointer for first-level translation, and BDF with VF for second-level translation. On a context switch, TLBs are flushed to avoid cross-domain access from stale TLBs.

#### **Managing Privilege Levels**

The hardware enforces privilege separation between Ring3 (UMD) and Ring0 (KMD) commands as follows:

- Only KMD is allowed to issue certain commands that are considered privileged.

- Only KMD commands are allowed to update the majority of graphics registers that are considered privileged.

- UMD-issued commands are allowed to access and update a small set of registers that are considered non-privileged.

This section describes how virtualization handles privileged commands and registers.

In general, KMD may create privileged command buffers and UMD creates non-privileged command buffers. From a hardware perspective, command buffers using the Global GTT are at a higher privilege level, while command buffers using Per Process GTT are non-privileged.

The MI\_BATCH\_BUFFER command contains an Address Space Indicator field that can determine whether the batch buffer uses the GGTT space or uses the PP GTT space. When a batch buffer command executes another batch buffer, the address space of the "child batch buffer" is determined by combining the Address Space Indicator fields of the parent batch buffer and child batch buffer. The privilege of a chained or second-level batch buffer is either equal to, or lower than, the privilege of the parent (e.g. a child cannot be GGTT if the parent is PP GTT).

The following table shows how privileged commands are handled in both virtualized and non-virtualized scenarios. In the non-virtualized case, a privileged command or access to GGTT in a non-privileged buffer

results in a no-op or modification to PPGTT access. In the virtualized scenario, the KMD in the VM can insert commands that use the VF GGTT, so commands that use GGTT can go through, with the restriction that they use the VF's GGTT.

| Category        | Command                      | Behavior in<br>Non-privileged<br>BB                                      | Behavior in VF with<br>privileged BB/Ring Buffer                                                                                                                       |  |  |

|-----------------|------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GTT Update      | MI_UPDATE_GTT                | No-op                                                                    | Allow only for PF                                                                                                                                                      |  |  |

| Display         | MI_DISPLAY_FLIP              | No-op                                                                    | Allow only for PF                                                                                                                                                      |  |  |

|                 | MI_LOAD_SCAN_LINES_INCL/EXCL | Non-privileged<br>instruction,<br>Allowed                                | Allow only for PF                                                                                                                                                      |  |  |

|                 | MI_WAIT_FOR_EVENT            | Non-privileged<br>instruction,<br>Allowed                                | Allow only for PF                                                                                                                                                      |  |  |

| Register Update | MI_LOAD_REGISTER_IMM         | No-op if target is<br>a Privileged<br>register                           | Continue UMD static whitelist and VF<br>KMD programmed whitelist. (Even though<br>OACONTROL (0x2B00) register is part of<br>the UMD static whitelist, this register is |  |  |

|                 | MI_LOAD_REGISTER_REG         | No-op if target is<br>a Privileged<br>register                           | privileged and only allowed by PF KMD<br>and will not be accessible by VF KMD or<br>UMD.)                                                                              |  |  |

|                 | MI_LOAD_REGISTER_MEM         | No-op if GGTT is<br>used or the<br>target is a<br>Privileged<br>register | VF KMD can access some registers using<br>an extended programmable whitelist<br>infrastructure.<br>Allow accesses within engine MMIO (e.g.                             |  |  |

|                 |                              |                                                                          | RenderCS can write to allowed registers<br>within the render engine).                                                                                                  |  |  |

|                 |                              |                                                                          | Allow register accesses to GAM/GAMT to enable context save/restore                                                                                                     |  |  |

| Memory write    | MI_STORE_DATA_INDEX          | No-op                                                                    | PF allowed to access Global or Per-<br>Process Hardware Status Page.                                                                                                   |  |  |

|                 |                              |                                                                          | VF allowed only to access Per-Process<br>Hardware Status Page.                                                                                                         |  |  |

|                 | MI_STORE_REGISTER_MEM        | No-op if GGTT is<br>used                                                 | Allow - target memory is always within VF                                                                                                                              |  |  |

|                 | MI_STORE_DATA_IMM            | No-op if GGTT is<br>used                                                 | Allow to VF GGTT or PPGTT                                                                                                                                              |  |  |

#### **Privileged Commands in Virtualized and Non-Virtualized Scenarios**

| Category | Command                                         | Behavior in<br>Non-privileged<br>BB                                                                                                            | Behavior in VF with<br>privileged BB/Ring Buffer                                                                                                                                                                                                                                                                                                                                        |

|----------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | MI_RS_STORE_DATA_IMM                            | No-op if GGTT is<br>used                                                                                                                       | Allow to VF GGTT or PPGTT                                                                                                                                                                                                                                                                                                                                                               |

| Sync     | MI_SEMAPHOR_MBOX, MI_SEMPHORE_<br>SIGNAL,/ WAIT | No-op if GGTT is<br>used                                                                                                                       | Not privileged. Semaphore address may be in GGTT or PP GTT                                                                                                                                                                                                                                                                                                                              |

|          | PIPE_CONTROL                                    | Send Flush<br>down.<br>Post Sync is No-<br>op if GGTT or<br>use store data<br>idx. Post sync LRI<br>to privileged<br>register is<br>discarded. | Allow - notify enable INT goes to GuC.<br>Post sync op for register write is subjected<br>to check (like MI_LOAD_REGISTER_IMM)<br>PF allowed to access Global or Per-<br>Process Hardware Status Page for "Post-<br>Sync Operation" with "Store Data Index".<br>VF allowed only to access Per-Process<br>Hardware Status Page when "Post-Sync<br>Operation" is with "Store Data Index". |

|          | MI_CLFLUSH                                      | Allow                                                                                                                                          | Allow                                                                                                                                                                                                                                                                                                                                                                                   |

|          | MI_FLUSH_DW                                     | No-op if GGTT or<br>use Store data<br>idx is enabled                                                                                           | Allow to VF GGTT or PPGTT<br>PF allowed to access Global or Per-<br>Process Hardware Status Page for "Post-<br>Sync Operation" with "Store Data Index".<br>VF allowed only to access Per-Process<br>Hardware Status Page when "Post-Sync<br>Operation" is with "Store Data Index".                                                                                                      |

|          | MI_ARB_CHECK                                    | Allow                                                                                                                                          | Allow                                                                                                                                                                                                                                                                                                                                                                                   |

|          | MI_ARB_ON_OFF                                   | No-ор                                                                                                                                          | Disallow - privileged                                                                                                                                                                                                                                                                                                                                                                   |

|          | MI_ATOMIC                                       | No-op if GGTT                                                                                                                                  | Allow - VF GGTT or PP GTT                                                                                                                                                                                                                                                                                                                                                               |

| Commands | MI_BATCH_BUFFER_START                           | Priv < = Parent<br>Privilege                                                                                                                   | Allow - not privileged                                                                                                                                                                                                                                                                                                                                                                  |

|          | MI_CONDITIONAL_BATCH_BUFFER_END                 | No-op if GGTT                                                                                                                                  | Allow - not privileged                                                                                                                                                                                                                                                                                                                                                                  |

|          | MI_USER_INTERRUPT                               | Allow                                                                                                                                          | Allow - GuC gets interrupt and notifies VF                                                                                                                                                                                                                                                                                                                                              |

|          | MI_NOOP                                         | Allow                                                                                                                                          | Allow                                                                                                                                                                                                                                                                                                                                                                                   |

|          | MI_COPY_MEM_MEM                                 | No-op if src or<br>dest addr is                                                                                                                | Allow                                                                                                                                                                                                                                                                                                                                                                                   |

| Category                                                                                        | Command                                                                                                                                   | Behavior in<br>Non-privileged<br>BB | Behavior in VF with privileged BB/Ring Buffer                                                                                                                                |

|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                 |                                                                                                                                           | GGTT                                |                                                                                                                                                                              |

|                                                                                                 | CRYPTO_INLINE_STATUS_READ                                                                                                                 | No-op if GGTT                       | Allow - status can be within VF GGTT or<br>PPGTT                                                                                                                             |

| Performance                                                                                     | MI_REPORT_PERF_COUNT                                                                                                                      | No-op if GGTT                       | No-op if GGTT and access are from VF.<br>VF are only allowed with PPGTT memory<br>type.<br>GGTT access are only allowed from PF ring<br>buffer or PF privilged batch buffer. |

| Legacy                                                                                          | MI_SET_CONTEXT                                                                                                                            | No-op                               | Allow within VF ring buffer, but not in non-privileged BB                                                                                                                    |

| GHWSP Access -<br>(Global Hadware<br>Status page-<br>setup through<br>HWS_PGA<br>MMIO register) | Updates to Context Status Buffer on a context<br>switch                                                                                   | -N.A-                               | Context Swtich Status update will only<br>happen on a PF context switch.<br>Context Switch status updates will not<br>happen on a VF context switch.                         |

|                                                                                                 | Interrupt status dword write to Hardware<br>Status Page on an interrupt when enabled<br>through HWSTAM (Hardwre status mask<br>register). | -N.A-                               | SW must not unmask HWSTAM for any interrupts in virtualized mode of operation.                                                                                               |

|                                                                                                 | Index writes in to GHWSP through<br>MI_STORE_DATA_INDEX, PIPE_CONTROL and<br>MI_FLUHS_DW                                                  | No-op if GGTT                       | No-op if access from VF.<br>PF allowed to access.                                                                                                                            |

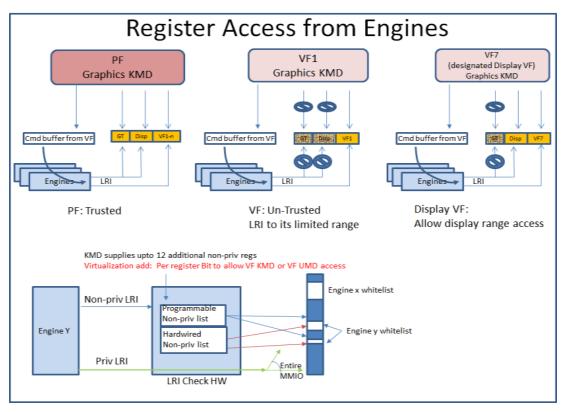

Access to device registers is by either of two methods: directly from the host CPU, or from a graphics engine using an MI\_LOAD\_REGISTER\_\* command. As described for the MMIO Space, the Host path allows VF software limited access to only a subset of device registers. This section describes details for limiting register access through an engine.

The hardware treats most registers as privileged. Functionally, UMD must be able to access certain registers, so a whitelist infrastructure provides limited register access, as described below:

- Specific registers in each engine are marked as non-privileged. Hardware allows non-privileged command buffers to complete accesses to these registers.

- However, such a hardwired whitelist is restrictive, and can be problematic if access to additional registers becomes necessary. So each engine provides a programmable means of converting twelve additional registers from privileged to non-privileged KMD is expected to do the programming. The converted registers are saved and restored as part of power context, not process context.

In a virtualized environment, an engine is allowed four levels of register accesses as follows:

- UMDs for both PF and VF can access the standard UMD whitelist.

- A non-display VF KMD needs access to a larger set of registers than the UMD whitelist, but not the entire register range. Additional infrastructure to allow the extended register accesses is described later in this document.

- A display VF KMD can access the same registers as a non-display VF KMD, in addition to registers associated with the Display Engine (e.g., to schedule flips via LRI).

- PF KMD can access any register.

The programmable whitelist registers are modified by adding a single bit in each register, to specify whether the non-privileging action is targeted for UMD or KMD access. The added bit allows a trusted agent to set up some of the twelve programmable registers to allow VF KMD access to specific registers. The PF driver or GuC is responsible for setting up the programmable register list.

**Register Access from Engines**

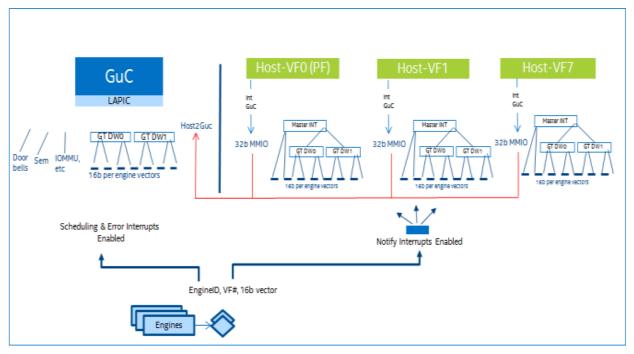

### **Interrupt Interface**

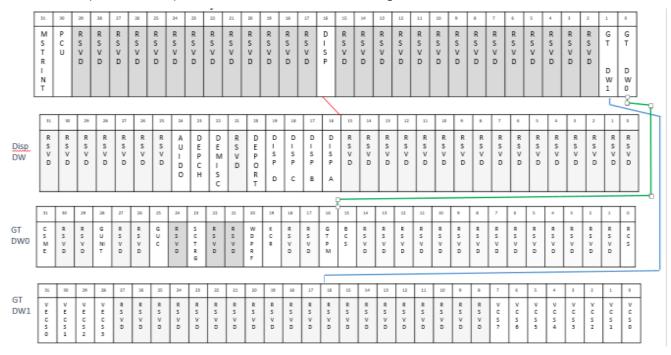

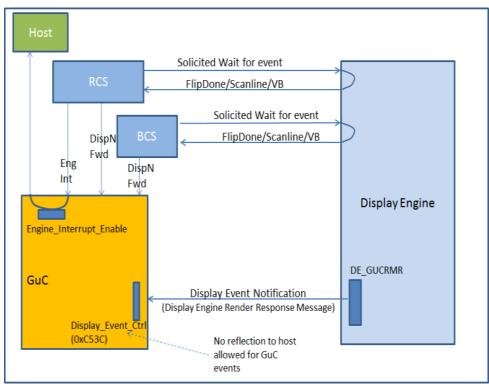

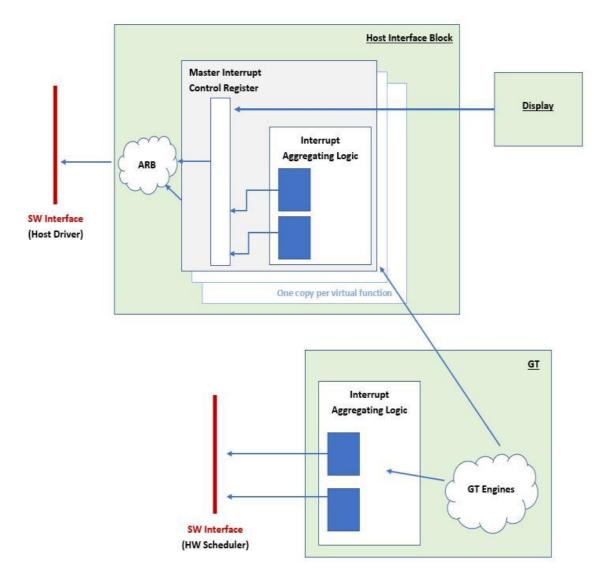

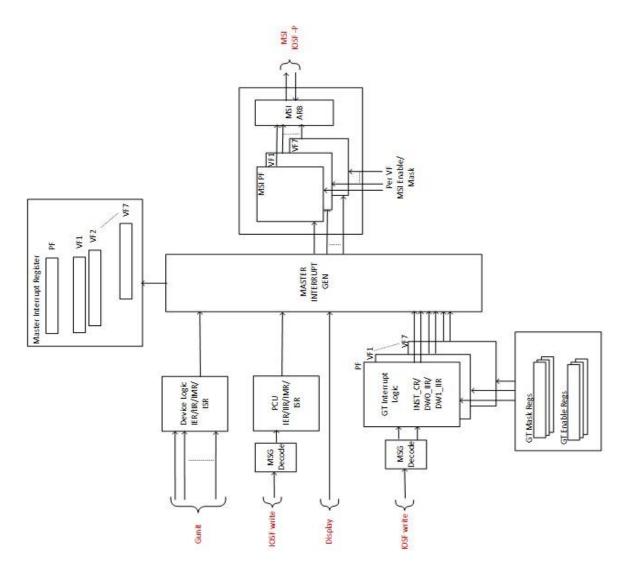

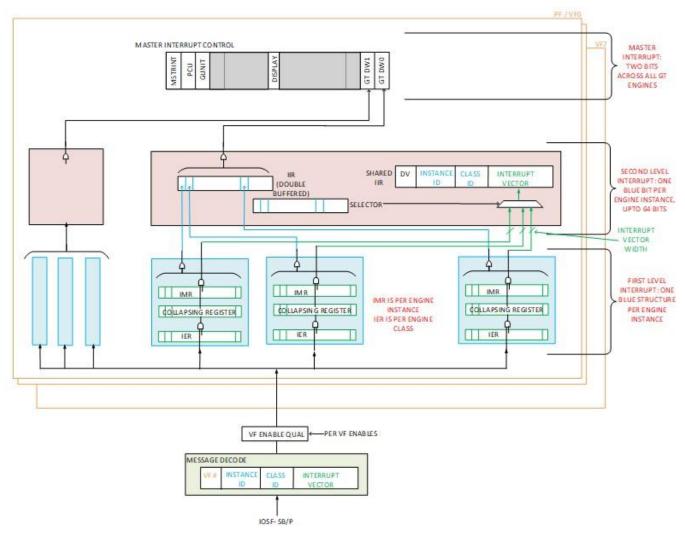

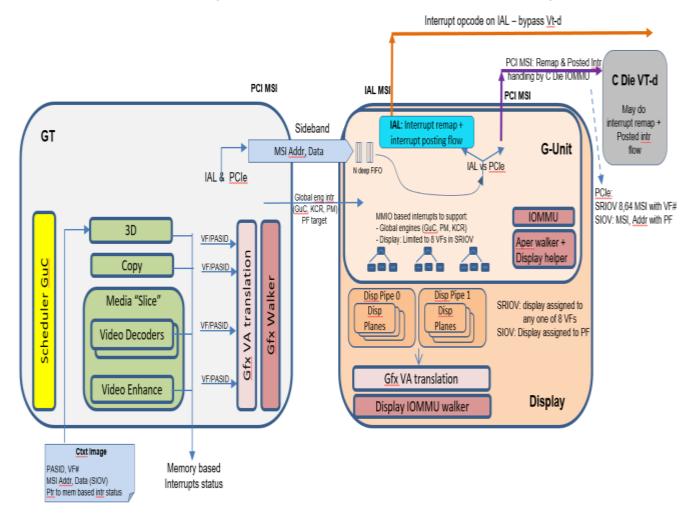

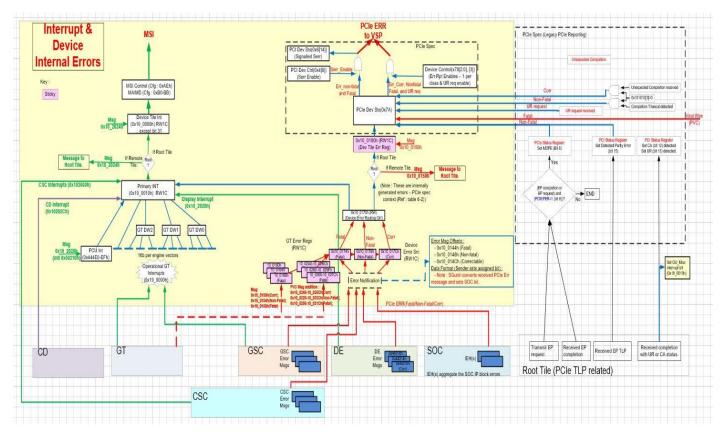

Hardware exposes interrupts to the Host as shown in the figure below.

#### **Pre-graphics Virtualization Scenario for Interrupt Delivery**

Each VF's address space replicates the virtualization interrupt infrastructure. This replication keeps hardware and interrupt delivery routing simple, trading cost for simplicity. The following figure shows the infrastructure replicated in each VF's domain.

#### Interrupt Infrastructure per Virtual Function

Display hardware propagates display events only to PF. GuC can virtualize some display events to a VF if desired.

**Display <=> Guc Interrupt Messages**

#### Resets

Hardware supports the following reset variations:

- Conventional Reset

- Function Level Reset targeting a PF

- Function Level Reset targeting a VF

- Clearing the VF Enable bit with the SR-IOV Control register

- Engine-specific Reset

#### **Conventional Reset (Bus Reset)**

A conventional reset returns all functions (including PFs and VFs) to their original power-on state, and clears VF Enable in the PF - so VFs do not exist after a conventional reset.

#### FLR Targeting a PF

A Functional Level Reset (FLR) targeting a PF resets the PF to the PCIe Specification. The PF FLR resets the SR-IOV Extended Capability, including VF Enable, so VFs do not exist after this type of reset. For a single-

function integrated device (not counting VFs), PF FLR is almost the same as Conventional Reset, except that "Sticky" bits in Cfg space are preserved.

#### FLR Targeting a VF

The SR-IOV requires that all VFs support FLR. A VF FLR must clear the VF's internal state, but FLR does not affect the VF's existence in PCI Configuration Space or PCI Bus address space. The VF FLR does not affect the VF's BARn values or VF MSE in the PF's SR-IOV Extended Capability. Also, a VF FLR does not affect other VFs.

VMMs can use FLR to reset a VF before assigning that VF to a new VM. For this use of VF FLR, hardware functions normally without a reset, so the reset just clears leftover states from the previous VM.

Initiating a VF FLR triggers the following events:

- The MMIO space BARs retain their contents.

- Host invocation of VF FLR generates an interrupt to GuC.

- GuC interrupts the PF KMD to indicate that a VF is going through FLR sequence. The VF number is passed in the interrupt data register.

- PF KMD deactivates all doorbells associated with the VF FLR, by clearing the "cookie" value in DW0 of each affected doorbell address. Clearing the cookie value causes the doorbell controller to clear the doorbell's Valid bit, which software cannot directly clear.

- Note: GuC may be able to disable the doorbell by clearing the cookie value in memory, if future driver architecture allows GuC firmware (instead of KMD) to allocate the doorbells. This software detail is addressed in the SAS.

- GuC discards all unscheduled workloads associated with the VF FLR.

- GuC pre-empts any workloads associated with the VF FLR that are currently running on engines. Note that software may choose use Engine-specific reset to terminate the workload (must not affect any workloads running on behalf of a different VF).

- Each CS running a context associated with the VF undergoing FLR initiates a TLB Invalidate that clears the PPGTT TLB associated with the CS engine.

- Note: an engine-specific reset would clear out the GAM resources for that Engine, including TLB.

- Clearing the PPGTT TLB for the CS engine does not affect second-level (VTd) intermediate walker caches.

- The VMM invalidates second-level TLB caches, if necessary.

- GuC discards any pending semaphores associated with VF workloads.

- GuC clears the VF interrupt interface: VF primary control, VF Interrupt additional info, and the VF GuC interrupt port.

- GuC interrupts PF KMD to indicate that cleanup is complete.

- Gunit resets VF-dedicated MMIO registers.

The above VF FLR handling occurs when hardware and GuC firmware are functioning properly. To catch possible errors, use PF KMD to monitor GuC firmware at regular intervals. If GuC does not respond in a timely manner, initiate an all-engine reset including reset of the GuC hardware, or use PF KMD to trigger a conventional reset (bus reset) of the entire device. When using PF to trigger a conventional reset, PF KMD must be able to notify the VMM, since the VMM must re-enable and rebuild the Virtual Functions.

#### **Clearing SR-IOV VF Enable**

When a VF Enable is cleared after being set, all of the VFs associated with PF cease to exist and must no longer issue PCIe transactions or respond to Configuration Space or Memory Space accesses. VFs must not retain any state (including sticky bits) after VF Enable has been cleared. These conditions are ensured by the following actions:

- VF Enable (Gunit) must qualify all configuration and memory accesses targeting VFs.

- Clearing VF Enable triggers an interrupt from Gunit to GuC.

- GuC firmware clears the internal state for all VFs, using the same flow described earlier for FLR targeting a VF. GuC firmware must follow the VF FLR flow for all previously enabled VFs.

#### **Engine-Specific Reset**

The PF KMD or GuC can reset specific hardware engines (e.g. RCS, BCS, VCS) when an engine is not responding. VF KMD is not allowed to directly reset any engine, since that engine may be executing work on behalf of a different VM. Instead, VF KMD interrupts GuC using the existing Host->GuC interrupt mechanism. GuC makes sure an engine is reset only if that engine is running on behalf of the interrupting VM/VF, and not running for any others.

#### **Stolen Memory Management**

Virtualization does not change stolen memory allocation. The BIOS allocates stolen memory and updates the BDSM and BGSM registers accordingly. The existence of stolen memory is exposed only to the PF driver.

Stolen memory segments are managed as follows:

GSM

- Global GTT is located in the stolen memory.

- Each VF can update its section of the GTT through the VF GTTADDR range.

DSM

- Only the PF driver can access DSM memory.

- VF must not map its Global GTT entries to DSM physical address.

#### **Local Memory Virtualization**

The GPU Device can be associated with a dedicated memory resource that is not shared with other system devices and not managed directly by the Operating System or Hypervisor / Virtual Machine Manager (VMM). Such a resource is referred to as "Local Memory". The most straightforward way to provide Local Memory is to directly attach dedicated memory, such as DDR, GDDR, or HBM, to the GPU device. But it is also possible to create a pool of Local Memory by carving out of stealing it from the normal System Memory pool (i.e., system DRAM).

Local Memory allocation is managed by the Device Driver instead of the OS or VMM. In a non-virtualized environment, the driver can differentiate Local vs System memory allocations using a bit in the 1st-level page tables (PPGTT or GGTT) and that is all that is required. Simple device virtualization using Direct Device Assignment or Pass-Thru models use the same mechanism, since the entire Local Memory is owned by the device and that device is attached to only one Guest VM.

However, with more complicated virtualization environments such as Single Root I/O Virtualization (SRIOV), the pool of Local Memory must be allocated among all Guests using the device, while preserving isolation requirements between the Guests. Specifically, a given Guest VM must be able to access Local Memory that was explicitly allocated to that Guest, but not be able to access any Local Memory that was allocated to a different Guest VM, nor to the Host/Hypervisor.

Since Local Memory is dedicated to the device, the Hypervisor does not manage this allocation. The GPU Driver and supporting HW must provide the mechanisms to provide and enforce the allocation of Local Memory.

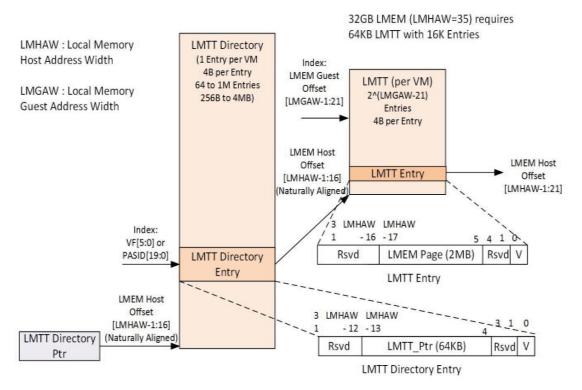

#### **Local Memory Translation Table**

In order to flexibly allocate a limited amount of memory that is local to the GPU device, and isolate that allocation from other Virtual Machines, a new 2<sup>nd</sup>-Level "Local Memory Translation Table" (LMTT) is implemented in GT HW and SW. This table is used for Local Memory in place of the VTd 2<sup>nd</sup>-level table used with memory managed by system software (OS and VMM).

The key characteristics of the Local Memory Translation Tables (LMTT) are:

- The LMTT tables are managed by the Host KMD, in coordination with the VMM or Host OS

- A separate LMTT structure is allocated for each Guest VM or Assignable Interface that receives Local Memory resources

- The parameter Local Memory Guest Address Width (LMGAW) defines the number of address bits available for Guest view of Local Memory

- The parameter Local Memory Host Address Width (LMHAW) defines the number of address bits available for the final Host view of Local Memory

- In the initial implementation, LMGAW and LMHAW are expected to be equal, so any Guest can access all of Local Memory, but this is not required architecturally.

- LMTT is a multi-level structure, residing entirely in Local Memory

- The top level is a Directory, with an entry for each Guest VM/VF

- For SRIOV, the Directory Entries are indexed by the Function Number (63 VF + 1 PF = 64 Entries)

- Each LMTT Directory Entry contains:

- Location of the next-level LMTT structure for the specified VM, in physical Local Memory, in multiples of 64KB (LMHAW-16 bits)

- Valid bit

- With future SIOV support, Directory Entries are indexed by the PASID (20-bit PASID = 1M Entries), and must be naturally aligned.

- LMTT Directory must be aligned on a 64KB boundary in Local Memory

- The location of the LMTT Directory is stored in two MMIO registers accessible only by the Host KMD: one in Gunit, and one in GT (GAM)

- LMTT Leaf level translates a 2MB page of Local Memory in Guest address space to physical Local Memory

- Each LMTT Entry is 32-bits wide and contains

- Final translation of 2MB page from Guest Local Memory into the final Host Local Memory Page (address bits LMHAW-1:21).

- Valid bit

#### LMTT Attributes

| LMGAW   | LMHAW   | Directory<br>Entry Size | Directory<br>Size | L2 Entry<br>Size | L2<br>Size | Leaf Entry<br>Size | Leaf Table<br>Size |

|---------|---------|-------------------------|-------------------|------------------|------------|--------------------|--------------------|

| 37 bits | 37 bits | 32 bits                 | 64 Entries        | N/A              | N/A        | 32 bits            | 64k Entries        |

| (128GB) | (128GB) |                         | 256 Bytes         |                  |            |                    | 256KB              |

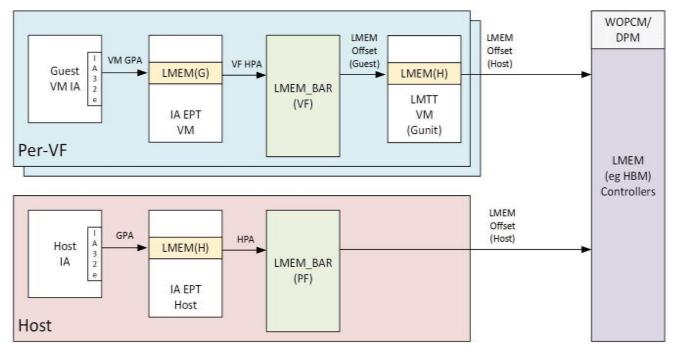

When a Guest VM is created, the VMM will virtualize an LMEM\_BAR for the Guest to configure. This is referred to as LMEM\_BAR(g) to differentiate from the "real" physical LMEM\_BAR associated with the device (LMEM\_BAR(h)). The Guest OS will assign a GPA to the LMEM\_BAR(g) as it would any other PCI MMIO resource.

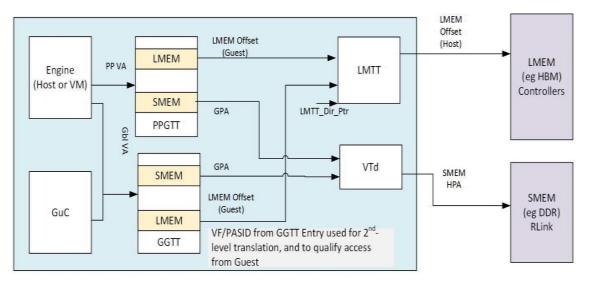

When a Command Streamer loads a new context, the VF# is extracted from the Context Descriptor and passed to the GAM, which tracks this information separately for each Engine.

When GAM HW receives a request from an "Engine" (e.g., Render or VDBox) it performs 1<sup>st</sup>-level translation using the appropriate PPGTT. Each PPGTT Entry includes a new "LMEM" bit that indicates whether the page is allocated in Local Memory, or System Memory. If the page resides in Local Memory, then LMTT is used for 2<sup>nd</sup> level translation, otherwise the standard VTd tables are used via Host-based IOMMU (there is no IOMMU functionality within the discrete GPU device).

TLBs in GAM work essentially the same as today, except that the TLB tag data must include the new LMEM information from the page table entry. There are no changes required to TLB invalidations -

appropriate entries are automatically invalidated whenever a new context starts (whether part of a new VM or not), and same SW controls (KMD and GuC FW) can also be used to force invalidations when necessary.

The following figure illustrates the structure and function of the LMTT:

#### **Two-Level LMTT Structure**

#### Multi-Level LMTT Structure

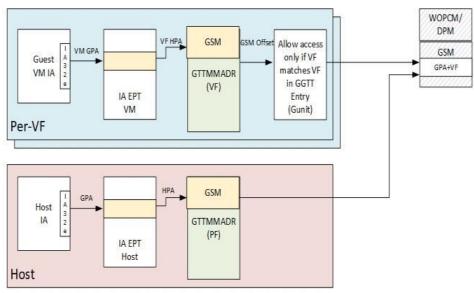

#### **Global Memory Space**

Global Address space, and the associated Global GTT, are shared for all Global allocations for all Guest VMs or Als, as is already defined for SRIOV in monolithic (non-G-die) configurations with UMA memory. In the current SRIOV definition, the Global GTT is managed by the Host KMD, which determines which global address can be accessed by which Guests. The Global GTT Entry includes the Function Number of the guest (or Host) to which that global page has been allocated. The Host KMD allocates the GGTT entries for each Virtual Function. A Guest Kernel Mode Driver is allowed to directly update GGTT Entries that have already been allocated to that Guest VM/VF. A VM will be allowed to access the GGTT range (GSM) within the GTTMMADR BAR of the VF to which it has been mapped. A read or write to a specific GGTT Entry within a VF GSM range results in Gunit HW reading that entry and ensuring the Function Number field within the Entry matches the VF# of the access. If it does, the access is allowed to proceed, else it is blocked (writes dropped, reads return all zeros).

The diagram below illustrates the flow for access from IA Guest or Host driver to the GGTT in GSM range.

When GAM receives a request from a global agent, such as GuC or OA, or from an Engine that is operating on behalf of the Host, that targets Global Memory, GAM will use the Function Number from the GGTT for 2<sup>nd</sup>-level translation, instead of the Host's Function Number of 0. This allows the Host to share global space with all Guests.

With Type 2 Local Memory, we build on the above mechanism, and add another bit ("LMEM" bit 1) to the GGTT Entry to distinguish Global addresses that are allocated in Local Memory vs those in regular system memory. If the Global Address is in Local Memory (Local = 1), then 2<sup>nd</sup>-level translation is performed using the LMTT, as described above. If the Global Address is not Local (LMEM = 0), then the address is a GPA and is further translated through VTd 2<sup>nd</sup>-level tables using via the Host IOMMU - there is no need for IOMMU within the ATS device.

Note: The astute reader may wonder why a new bit is required to distinguish Local vs System Memory? Why can't HW just compare the physical address in the GGTT Entry against the PF LMEM\_BAR, similar to PPGTT handling? That wouldn't work because the GGTT Entry may contain either a GPA pointing to DDR, or an HPA pointing to Local Memory, and nothing prevents the DDR GPA from overlapping the LMEM\_BAR range.

Because the global address space is shared by all contexts and all Guest VMs, and is limited to 4GB total, the GGTT page size granularity remains 4KB. When allocating global surfaces larger than 4KB, the Host KMD should attempt to choose contiguous 4KB pages up to at least 64KB, which is the minimum page size for which HBM accesses are optimized.

The updated GGTT Entry format:

GGTT Entry

| 6                 | 5 | 5 | 4              | 4         | 1    | 1 |   |   |   |

|-------------------|---|---|----------------|-----------|------|---|---|---|---|

| 3                 | 4 | 3 | 6              | 5         | 2    | 1 | 2 | 1 | 0 |

| PASID[19:10] Rsvd |   | Ģ | FA/LMEM[45:12] | VF/PASID[ | 9:0] | L | V |   |   |

The following diagram illustrates the key structures and flows described above:

#### **IA CPU Accesses to Local Memory**

With SRIOV and Local Memory, the VF GMADR BARs are replaced by VF LMEM\_BARs. The VMM virtualizes these VF BARs for each Guest VM. When a VM accesses its virtualized LMEM\_BAR(G), the IA EPT for that VM will translate the request to the VF LMEM\_BAR to which the VM has been assigned. The address of this request is in HPA space but does not yet map to the physical Local Memory, which resides at the PF LMEM\_BAR range. So SGunit HW must also use the LMTT to translate from the Guest view of HBM to the actual location. The index into the LMTT\_Directory structure is the VF# that contains the VF LMEM\_BAR that was targeted by the access. The location of the LMTT\_Directory structure is stored in a PF MMIO register (not accessible by a Guest VM).

The PF GMADR BAR is similarly replaced with a PF LMEM\_BAR, which provides direct access to Local Memory. No LMTT translation is required for Host/PF access to Local Memory. SGunit HW simply strips off the LMEM\_BAR base address to generate the final offset into Local Memory. HW does however need to protect certain non-IA accessible ranges such as WOPCM, DPM, and the GGTT (GGTT is only accessible to host via GSM range of GTTMMADR).

The following diagram illustrates the for SRIOV IA accesses to Local Memory:

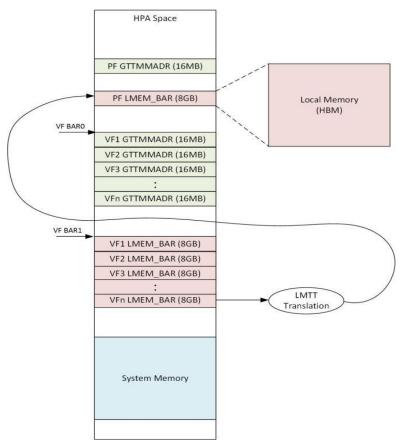

The following Diagram shows how the various SRIOV BARs fit into HPA Space, using default BAR sizes (LMEM\_BARs are configurable):

### MMIO

This is the MMIO chapter for System Interfaces Volume.

### Force Wake and Steering Table

| MMIO Range<br>Start | MMIO Range<br>End | #<br>Bytes | Wake<br>Target | Replicated<br>/<br>Multicast ? | Replication Group<br>Type | Inst.<br>Count | Steering                       |

|---------------------|-------------------|------------|----------------|--------------------------------|---------------------------|----------------|--------------------------------|

| 0000000             | 00000AFF          | 2816       |                |                                |                           |                |                                |

| 00000B00            | 00000BFF          | 256        | AON            | Yes                            | SQIDI                     | 8              | subsliceid[07]                 |

| 00000C00            | 00000DFF          | 512        | AON            | No                             | -                         | 1              | -                              |

| 00000E00            | 00000FFF          | 512        | AON            | No                             | -                         | 1              | -                              |

| 00001000            | 00001FFF          | 4096       | AON            | Yes                            | SQIDI                     | 8              | subsliceid[07]                 |

| 00002000            | 000026FF          | 1792       | RENDER*        | No                             | -                         | 1              | -                              |

| 00002700            | 000027FF          | 256        | GT             | No                             | -                         | 1              | -                              |

| 00002800            | 00002AFF          | 768        | GT             | No                             | -                         | 1              | -                              |

| 00002B00            | 00002FFF          | 1280       | GT             | No                             | -                         | 1              | -                              |

| 00003000            | 00003FFF          | 4096       | GT             | No                             | -                         | 1              | -                              |

| 00004000            | 000041FF          | 512        | GT             | Yes                            | MSLICE                    | 4              | sliceid[03]                    |

| 00004200            | 000043FF          | 512        | GT             | Yes                            | MSLICE                    | 4              | sliceid[03]                    |

| 00004400            | 000048FF          | 1280       | GT             | Yes                            | MSLICE                    | 4              | sliceid[03]                    |

| 00004900            | 00004AFF          | 512        | GT             | Yes                            | MSLICE                    | 4              | sliceid[03]                    |

| 00004B00            | 00004FFF          | 1280       |                |                                |                           |                |                                |

| 00005000            | 000050FF          | 256        | AON            | No                             | -                         | 1              | -                              |

| 00005100            | 000051FF          | 256        | AON            | No                             | -                         | 1              | -                              |

| 00005200            | 000052FF          | 256        | RENDER         | Yes                            | GSLICE                    | 8              | sliceid[07]                    |

| 00005300            | 000053FF          | 256        | RENDER*        | No                             | -                         | 1              | -                              |

| 00005400            | 000054FF          | 256        | RENDER         | Yes                            | GSLICE                    | 8              | sliceid[07]                    |

| 00005500            | 00005FFF          | 2816       | RENDER         | Yes                            | GSLICE                    | 8              | sliceid[07]                    |

| 00006000            | 00006FFF          | 4096       | RENDER         | Yes                            | GSLICE                    | 8              | sliceid[07]                    |

| 00007000            | 00007FFF          | 4096       | RENDER         | Yes                            | GSLICE                    | 8              | sliceid[07]                    |

| 0008000             | 000080FF          | 256        | GT             | No                             | -                         | 1              | -                              |

| 00008100            | 0000813F          | 64         | GT             | No                             | -                         | 1              | -                              |

| 00008140            | 0000814F          | 16         | RENDER         | Yes                            | GSLICE                    | 8              | sliceid[07]                    |

| 00008150            | 0000815F          | 16         | RENDER         | Yes                            | DSS                       | 32             | sliceid[07],<br>subsliceid[03] |

| 00008160            | 0000817F          | 32         |                |                                |                           |                |                                |

| 00008180            | 000081FF          | 128        | AON            | No                             | -                         | 1              | -                              |

| 00008200            | 000082FF          | 256        | GT             | No                             | -                         | 1              | _                              |

| 00008300            | 000084FF          | 512        | RENDER*        | No                             | -                         | 1              | _                              |

| 00008500            | 000085FF          | 256        | GT             | No                             | -                         | 1              | -                              |

| 00008600            | 000086FF          | 256        | GT             | No                             | -                         | 1              | -                              |

| MMIO Range<br>Start | MMIO Range<br>End | #<br>Bytes | Wake<br>Target | Replicated<br>/<br>Multicast ? | Replication Group<br>Type | Inst.<br>Count | Steering                       |

|---------------------|-------------------|------------|----------------|--------------------------------|---------------------------|----------------|--------------------------------|

| 00008700            | 000087FF          | 256        | GT             | Yes                            | SQIDI                     | 8              | subsliceid[07]                 |

| 00008800            | 0000883F          | 64         | -              |                                |                           | -              |                                |

| 00008840            | 000089FF          | 448        |                |                                |                           |                |                                |

| 00008A00            | 00008BFF          | 512        |                |                                |                           |                |                                |

| 00008C00            | 00008C7F          | 128        |                |                                |                           |                |                                |

| 00008C80            | 00008CFF          | 128        | GT             | Yes                            | L3BANK                    | 32             | sliceid[03],<br>subsliceid[07] |

| 00008D00            | 00008D7F          | 128        | RENDER         | Yes                            | DSS                       | 32             | sliceid[07],<br>subsliceid[03] |

| 00008D80            | 00008DFF          | 128        | RENDER         | Yes                            | DSS                       | 32             | sliceid[07],<br>subsliceid[03] |

| 00008E00            | 00008FFF          | 512        |                |                                |                           |                |                                |

| 00009000            | 000093FF          | 1024       | GT             | No                             | -                         | 1              | -                              |

| 00009400            | 0000947F          | 128        | GT             | No                             | -                         | 1              | -                              |

| 00009480            | 000094CF          | 80         |                |                                |                           |                |                                |

| 000094D0            | 0000951F          | 80         | RENDER         | Yes                            | GSLICE                    | 8              | sliceid[07]                    |

| 00009520            | 0000955F          | 64         | RENDER         | Yes                            | DSS                       | 32             | sliceid[07],<br>subsliceid[03] |

| 00009560            | 000095FF          | 160        | AON            | No                             | -                         | 1              | _                              |

| 00009600            | 0000967F          | 128        |                |                                |                           |                |                                |

| 00009680            | 000096FF          | 128        | RENDER         | Yes                            | DSS                       | 32             | sliceid[07],<br>subsliceid[03] |

| 00009700            | 000097FF          | 256        |                |                                |                           |                |                                |

| 00009800            | 00009FFF          | 2048       | GT             | No                             | -                         | 1              | -                              |

| 0000A000            | 0000AFFF          | 4096       | GT             | No                             | -                         | 1              | -                              |

| 0000B000            | 0000B0FF          | 256        | GT             | Yes                            | LNCF                      | 8              | sliceid[03],<br>subsliceid[01] |

| 0000B100            | 0000B3FF          | 768        | GT             | Yes                            | L3BANK                    | 32             | sliceid[03],<br>subsliceid[07] |

| 0000B400            | 0000B4FF          | 256        | GT             | No                             | -                         | 1              | _                              |

| 0000B500            | 0000BFFF          | 2816       |                |                                |                           |                |                                |

| 0000C000            | 0000C7FF          | 2048       | GT             | No                             | -                         | 1              | -                              |

| 0000C800            | 0000CFFF          | 2048       | GT             | Yes                            | MSLICE                    | 4              | sliceid[03]                    |

| 0000D000            | 0000D3FF          | 1024       | AON            | No                             | _                         | 1              | -                              |

| 0000D400            | 0000D7FF          | 1024       | AON            | No                             | _                         | 1              | -                              |

| 0000D800            | 0000D87F          | 128        | RENDER         | Yes                            | GSLICE                    | 8              | sliceid[07]                    |

| 0000D880            | 0000D8FF          | 128        | GT             | Yes                            | LNCF                      | 8              | sliceid[03],<br>subsliceid[01] |

| 0000D900            | 0000DBFF          | 768        | GT             | No                             | -                         | 1              | -                              |

| 0000DC00            | 0000DCFF          | 256        | RENDER         | Yes                            | GSLICE                    | 8              | sliceid[07]                    |

| MMIO Range<br>Start | MMIO Range<br>End | #<br>Bytes | Wake<br>Target | Replicated<br>/<br>Multicast ? | Replication Group<br>Type | Inst.<br>Count | Steering                       |

|---------------------|-------------------|------------|----------------|--------------------------------|---------------------------|----------------|--------------------------------|

| 0000DD00            | 0000DDFF          | 256        | GT             | Yes                            | MSLICE                    | 4              | sliceid[03]                    |

| 0000DE00            | 0000DE7F          | 128        | 01             | 105                            | WIGHTE                    | · ·            | 5110010[05]                    |

| 0000DE80            | 0000DEFF          | 128        | RENDER         | Yes                            | DSS                       | 32             | sliceid[07],<br>subsliceid[03] |

| 0000DF00            | 0000DFFF          | 256        | RENDER         | Yes                            | DSS                       | 32             | sliceid[07],<br>subsliceid[03] |

| 0000E000            | 0000E0FF          | 256        |                |                                |                           |                |                                |

| 0000E100            | 0000E1FF          | 256        | RENDER         | Yes                            | DSS                       | 32             | sliceid[07],<br>subsliceid[03] |

| 0000E200            | 0000E3FF          | 512        | RENDER         | Yes                            | DSS                       | 32             | sliceid[07],<br>subsliceid[03] |

| 0000E400            | 0000E7FF          | 1024       | RENDER         | Yes                            | DSS                       | 32             | sliceid[07],<br>subsliceid[03] |

| 0000E800            | 0000E8FF          | 256        | RENDER         | Yes                            | DSS                       | 32             | sliceid[07],<br>subsliceid[03] |

| 0000E900            | 0000E9FF          | 256        | GT             | Yes                            | MSLICE                    | 4              | sliceid[03]                    |

| 0000EA00            | 0000EFFF          | 1536       |                |                                |                           |                |                                |

| 0000F000            | 0000F0FF          | 256        | GT             | Yes                            | MSLICE                    | 4              | sliceid[03]                    |

| 0000F100            | 0000FFFF          | 3840       | GT             | Yes                            | MSLICE                    | 4              | sliceid[03]                    |

| 00010000            | 00011FFF          | 8192       |                |                                |                           |                |                                |

| 00012000            | 000127FF          | 2048       | AON            | No                             | -                         | 1              | -                              |

| 00012800            | 00012FFF          | 2048       |                |                                |                           |                |                                |

| 00013000            | 000131FF          | 512        | VD0            | No                             | -                         | 1              | -                              |

| 00013200            | 000133FF          | 512        | VD2            | No                             | -                         | 1              | -                              |

| 00013400            | 00013FFF          | 3072       |                |                                |                           |                |                                |

| 00014000            | 000141FF          | 512        | VD0            | No                             | -                         | 1              | -                              |

| 00014200            | 000143FF          | 512        | VD2            | No                             | -                         | 1              | -                              |

| 00014400            | 000145FF          | 512        | VD4            | No                             | -                         | 1              | -                              |

| 00014600            | 000147FF          | 512        | VD6            | No                             | -                         | 1              | -                              |

| 00014800            | 00014FFF          | 2048       | RENDER*        | No                             | -                         | 1              | -                              |

| 00015000            | 000153FF          | 1024       | GT             | No                             | -                         | 1              | -                              |

| 00015400            | 000157FF          | 1024       | GT             | No                             | -                         | 1              | -                              |

| 00015800            | 00015BFF          | 1024       | GT             | No                             | -                         | 1              | -                              |

| 00015C00            | 00015FFF          | 1024       | GT             | No                             | -                         | 1              | -                              |

| 00016000            | 00016DFF          | 3584       |                |                                |                           |                |                                |

| 00016E00            | 00016FFF          | 512        | RENDER*        | No                             | -                         | 1              | -                              |

| 00017000            | 00017FFF          | 4096       | RENDER         | Yes                            | GSLICE                    | 8              | sliceid[07]                    |

| 00018000            | 00019FFF          | 8192       | RENDER*        | No                             | -                         | 1              | -                              |

| 0001A000            | 0001BFFF          | 8192       | RENDER*        | No                             | -                         | 1              | -                              |

| 0001C000            | 0001DFFF          | 8192       | RENDER*        | No                             | -                         | 1              | -                              |

| MMIO Range               | MMIO Range<br>End | #<br>Puter           | Wake              | Replicated<br>/<br>Multicast ? | Replication Group | Inst.<br>Count | Steering                       |

|--------------------------|-------------------|----------------------|-------------------|--------------------------------|-------------------|----------------|--------------------------------|

| <b>Start</b><br>0001E000 |                   | <b>Bytes</b><br>8192 | Target<br>RENDER* |                                | Type<br>_         | 1              | Steering                       |

|                          | 0001FFFF          |                      |                   | No                             |                   |                | -                              |

| 00020000                 | 00020FFF          | 4096                 | VD0               | No                             | -                 | 1              | -                              |

| 00021000                 | 00021FFF          | 4096                 | CT                |                                |                   | 1              |                                |

| 00022000                 | 00022FFF          | 4096                 | GT                | No                             | -                 | 1              | -                              |

| 00023000                 | 00023FFF          | 4096                 | GT                | No                             | -                 | 1              | -                              |

| 00024000                 | 0002407F          | 128                  | AON               | No                             | -                 | 1              | -                              |

| 00024080                 | 0002417F          | 256                  |                   |                                |                   |                |                                |

| 00024180                 | 000241FF          | 128                  | GT                | No                             | -                 | 1              | -                              |

| 00024200                 | 000249FF          | 2048                 |                   |                                |                   |                |                                |

| 00024A00                 | 00024A7F          | 128                  | RENDER            | Yes                            | DSS               | 32             | sliceid[07],<br>subsliceid[03] |

| 00024A80                 | 000251FF          | 1920                 |                   |                                |                   |                |                                |

| 00025200                 | 0002527F          | 128                  | GT                | No                             | -                 | 1              | -                              |

| 00025280                 | 000252FF          | 128                  | GT                | No                             | -                 | 1              | -                              |

| 00025300                 | 000255FF          | 768                  |                   |                                |                   |                |                                |

| 00025600                 | 0002567F          | 128                  |                   |                                |                   |                |                                |

| 00025680                 | 000256FF          | 128                  |                   |                                |                   |                |                                |

| 00025700                 | 000259FF          | 768                  |                   |                                |                   |                |                                |

| 00025A00                 | 00025A7F          | 128                  |                   |                                |                   |                |                                |

| 00025A80                 | 00025AFF          | 128                  |                   |                                |                   |                |                                |

| 00026000                 | 00027FFF          | 8192                 | RENDER*           | No                             | -                 | 1              | -                              |

| 00028000                 | 0002FFFF          | 32768                |                   |                                |                   |                |                                |

| 00030000                 | 0003FFFF          | 65536                | GT                | No                             | -                 | 1              | -                              |

|                          |                   |                      |                   |                                |                   |                |                                |

|                          |                   |                      |                   |                                |                   |                |                                |

| 001C0000                 | 001C07FF          | 2048                 | VD0               | No                             | _                 | 1              | _                              |

| 001C0800                 | 001C0FFF          | 2048                 | VD0               | No                             | _                 | 1              | _                              |

| 001C1000                 | 001C1FFF          | 4096                 | VD0               | No                             | _                 | 1              | _                              |

| 001C2000                 | 001C27FF          | 2048                 | VD0               | No                             | -                 | 1              | -                              |